# Ph.D. Thesis Stability of Polarization in Organic Ferroelectric Metal-Insulator-Semiconductor Structures

presented by Dipl. Phys. René Kalbitz

Supervisor

Prof. Dr. Reimund Gerhard

University of Potsdam,

Department of Physics and Astronomy,

Karl-Liebknecht-Str. 24-25,

14476 Potsdam, Germany

April 6. 2011

Published online at the Institutional Repository of the University of Potsdam: URL http://opus.kobv.de/ubp/volltexte/2011/5727/URN urn:nbn:de:kobv:517-opus-57276 http://nbn-resolving.de/urn:nbn:de:kobv:517-opus-57276

'Almost everything you do will seem insignificant, but it is important that you do it'

> Mahatma Gandhi

|   | •  |   |

|---|----|---|

| _ | 1V | _ |

## Acknowledgments

I thank Dr. P. Sayers, C. Watson and Dipl.-Ing. W. Wirges for technical support and Prof. T.J. Lewis, Prof. D. Neher and Dipl.-Phys. P. Pingel for constructive discussions. I further wish to thank my supervisor Prof. R. Gerhard and Dr. P. Frübing for his support. Special thanks to Prof. D.M. Taylor for his scientific guidance. I am also very grateful for the assistance of the DAAD-RISE-exchange students M.A.R. Martinez and S. Monfardini as well as the student helper M. Sander. This program was initiated by grants from the British Council (ARC 1294) and DAAD (D/07/09993) and financed through the project 'Polymeric thin film memory devices' of the Fraunhofer Institute for Applied Polymer Research in Potsdam.

### Abstract

Organic thin film transistors (TFT) are an attractive option for low cost electronic applications and may be used for active matrix displays and for RFID applications. To extend the range of applications there is a need to develop and optimise the performance of non-volatile memory devices that are compatible with the solution-processing fabrication procedures used in plastic electronics. A possible candidate is an organic TFT incorporating the ferroelectric copolymer poly(vinylidenefluoride-trifluoroethylene) (P(VDF-TrFE)) as the gate insulator.

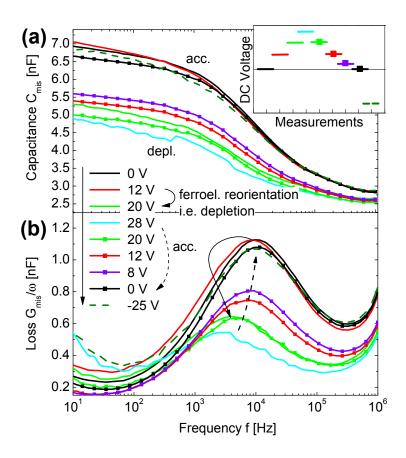

Dielectric measurements have been carried out on all-organic metal-insulator-semiconductor (MIS) structures with the ferroelectric polymer P(VDF-TrFE) as the gate insulator and poly(3-hexylthiophene) (P3HT) as p-type semiconductor. The capacitance spectra of MIS devices were measured under different biases, showing the effect of charge accumulation and depletion on the Maxwell-Wagner peak. The position and height of this peak clearly indicates the lack of stable depletion behavior and the decrease of mobility when increasing the depletion zone width, i.e. upon moving into the P3HT bulk.

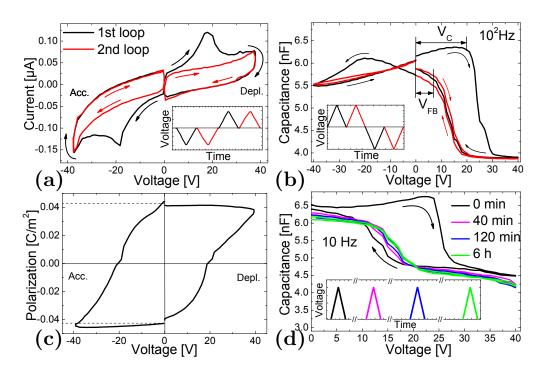

The lack of stable depletion was further investigated with capacitance-voltage (C-V) measurements. When the structure was driven into depletion, C-V plots showed a positive flat-band voltage shift, arising from the change in polarization state of the ferroelectric insulator. When biased into accumulation, the polarization was reversed. It is shown that the two polarization states are stable i.e. no depolarization occurs below the coercive field. However, negative charge trapped at the semiconductor-insulator interface during the depletion cycle masks the negative shift in flat-band voltage expected during the sweep to accumulation voltages.

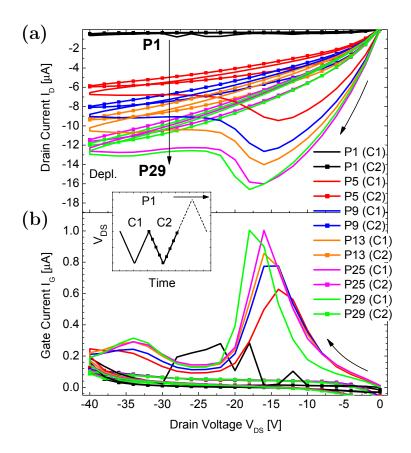

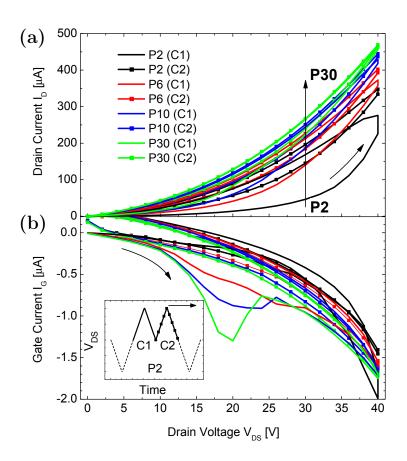

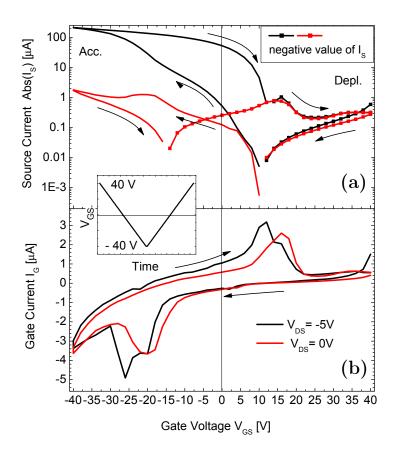

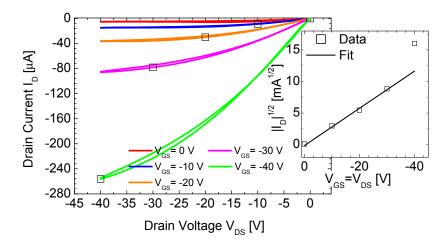

The measured output characteristics of the studied ferroelectric-field-effect transistors confirmed the results of the C-V plots. Furthermore, the results indicated a trapping of electrons at the positively charged surfaces of the ferroelectrically polarized P(VDF-TrFE) crystallites near the insulator/semiconductor interface during the first poling cycles. The study of the MIS structure by means of thermally stimulated current (TSC) revealed further evidence for the stability of the polarization under depletion voltages.

It was shown, that the lack of stable depletion behavior is caused by

the compensation of the orientational polarization by fixed electrons at the interface and not by the depolarization of the insulator, as proposed in several publications. <sup>77,80,81</sup> The above results suggest a performance improvement of non-volatile memory devices by the optimization of the interface.

## Zusammenfassung

Organische Transistoren sind besonders geeignet für die Herstellung verschiedener preisgünstiger, elektronischer Anwendungen, wie zum Beispiel Radio-Frequenz-Identifikations-Anhänger (RFID). Für die Erweiterung dieser Anwendung ist es notwendig die Funktion von organischen Speicherelementen weiter zu verbessern. Das ferroelektrische Polymer Poly(vinylidenfluoride-Trifluoroethylen) (P(VDF-TrFE)) eignet sich besonders gut als remanent polarisierbarer Isolator in Dünnschicht-Speicherelementen.

Um Schalt- und Polarisationsverhalten solcher Speicherelemente zu untersuchen, wurden P(VDF-TrFE)-Kondensatoren und Metall-Halbleiter-Isolator-Proben sowie ferroelektrische Feld-Effekt-Transistoren (FeFET) aus dem Halbleiter Poly(3-Hexylthiophen) (P3HT) und P(VDF-TrFE) hergestellt und dielektrisch untersucht.

Die Charakterisierung der MIS-Strukturen mittels spannungsabhängiger Kapazitätsspektren machte deutlich, dass es nicht möglich ist, einen stabilen Verarmungzustand (Aus-Zustand) zu realisieren. Kapazität-Spannungs-Messungen (C-V) an MIS-Proben mit uni/bi-polaren Spannungszyklen zeigten eine stabile ferroelektrische Polarisation des P(VDF-TrFE)-Films. Eine Depolarisation des Isolators durch den Mangel an Minoritäts-Ladungsträgern <sup>77,80,81</sup> konnte als Grund für die Instabilität des Verarmungszustandes ausgeschlossen werden. Die C-V-Kurven wiesen vielmehr auf die Existenz fixierter, negativer Ladungsträger an der Grenzfläche hin.

Messungen von Output-Charakteristiken an FeFETs zeigten, dass diese fixierten Ladungsträger erst durch Anlegen einer äußeren Spannung an die Isolator/Halbleiter-Grenzfläche gelangen und nicht durch die Präparation. Die wahrscheinlichste Erklärung ist ein Elektronen-Transfer vom P3HT im Verarmungszustand, das heißt, beim Anlegen von positiver Spannung, an die Grenzfläche. Diese Ladungen werden an der Grenzfläche durch positive Polarisationsladung des P(VDF-TrFE) eingefangen (Charge Trapping) und energetisch und räumlich stabilisiert. Die Stabilität der Polarisation konnte durch die Untersuchung mittels thermisch stimulierter Ströme (TSC) bestätigt werden.

Zusammenfassend kann festgestellt werden: die Ursache der Ladungsträgerinstabilitäten in organischen ferroelektrischen Speicherelementen ist auf die Kompensation der ferroelektrischen Orientierungspolarisation durch "ge-

trappte" (fixierte) negative Ladungsträger zurückzuführen. Dieses Ergebnis liefert nun eine Grundlage für die Optimierung der Isolator/Halbleiter-Grenzfläche mit dem Ziel, die Zahl der Fallenzustände zu minimieren. Auf diesem Wege könnte die Stabilität des Speicherzustandes in organischen Dünnschichtspeicherelementen deutlich verbessert werden.

## Contents

| A  | ckno  | wledgr     | nents                                                     | 7  |

|----|-------|------------|-----------------------------------------------------------|----|

| A  | bstra | act        |                                                           | vi |

| Ζι | usam  | menfa      | ssung                                                     | ix |

| 1  | Inti  | troduction |                                                           |    |

| 2  | The   | eoretic    | al Background                                             | 7  |

|    | 2.1   | Morp       | hology and Related Properties of the Materials            | 7  |

|    |       | 2.1.1      | Poly(3-Hexylthiophene)                                    | 7  |

|    |       | 2.1.2      | Polyvinylidene Fluoride and Its Copolymer                 | Ö  |

|    |       | 2.1.3      | Current-Voltage Characteristics                           | 12 |

|    | 2.2   | MIS (      | Capacitance Curves                                        | 14 |

|    |       | 2.2.1      | Ideal Capacitance-Voltage Characteristics                 | 14 |

|    |       | 2.2.2      | Effect of Interface Charges on Current-Voltage Charac-    |    |

|    |       |            | teristics                                                 | 18 |

|    |       | 2.2.3      | Calculation of Semiconductor Interface Potential          | 22 |

|    |       | 2.2.4      | Field-Effect-Transistor Equation                          | 23 |

| 3  | Pre   | parati     | on and Sample Characterization                            | 27 |

|    | 3.1   | Devic      | e Preparation                                             | 27 |

|    |       | 3.1.1      | Preparation of Poly(vinylidenefluoride-Trifluoroethylene) |    |

|    |       |            | and Poly(3-Hexylthiophene) Solution                       | 27 |

|    |       | 3.1.2      | Preparation of Metal-Insulator-Metal (MIM) devices $$     | 28 |

|    |       | 3.1.3      | Preparation of Semiconductor Devices                      | 31 |

|    | 3.2   | Chara      | acterization Methods                                      | 34 |

|    |       | 3.2.1      | Determination of Film Thickness                           | 34 |

|    |       | 3.2.2      | Impedance Measurements                                    | 35 |

|    |       | 3.2.3      | Field-Effect Transistor Measurements                      | 36 |

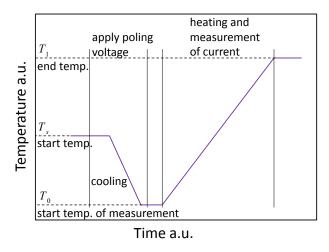

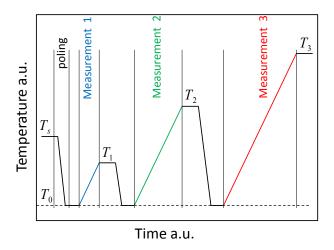

|    |       | 3.2.4      | Thermally Stimulated Current Measurements                 | 36 |

|    |       | 3.2.5      | Current-Voltage Measurements                              | 36 |

|    | 3.3   | Funda      | amental Device Characterization                           | 37 |

#### CONTENTS

| $\mathbf{St}$             | atem                           | nent of  | f Authorship/Selbstständigkeitserklärung                   | 113 |

|---------------------------|--------------------------------|----------|------------------------------------------------------------|-----|

| Bi                        | ibliog                         | graphy   | •                                                          | 99  |

|                           | Cur                            | riculum  | Vitae                                                      | 95  |

|                           | List                           | of Sym   | nbols                                                      | 93  |

|                           | Mod                            | deling C | C-V Spectra                                                | 88  |

| $\mathbf{A}_{\mathbf{j}}$ | ppen                           |          |                                                            | 87  |

| 5                         | 5 Final Conclusion and Outlook |          | iclusion and Outlook                                       | 85  |

|                           |                                | lated    | Current (TSC) measurements                                 | 76  |

|                           | 4.5                            |          | of stable Ferroelectric Polarization on Thermally Stimu-   |     |

|                           | 1.1                            |          | istor Performance                                          |     |

|                           | 4.4                            |          | of Stable Ferroelectric Polarization on the Field-Effect   |     |

|                           | 4.3                            |          | emiconductor Structures                                    |     |

|                           | 4.2                            |          | ity of Polarization in Organic Ferroelectric Metal-Insula- |     |

|                           |                                | _        | er Effect at Semiconductor/Insulator interface             |     |

|                           | 4.1                            | Influe   | nce of Remanent Polarization of the Insulator on Maxwell-  |     |

| -                         | Dev                            |          | The Total Zation in a Wietal-Institutor-Semiconduct        | 47  |

| 4                         | For                            | roelect  | tric Polarization in a Metal-Insulator-Semiconduct         | or  |

|                           |                                |          | ductor Structures                                          | 40  |

|                           |                                | 3.3.2    | Lateral Current Inspection in Metal-Insulator-Semicon-     |     |

|                           |                                | 0.0.1    | Trifluoroethylene) Films                                   |     |

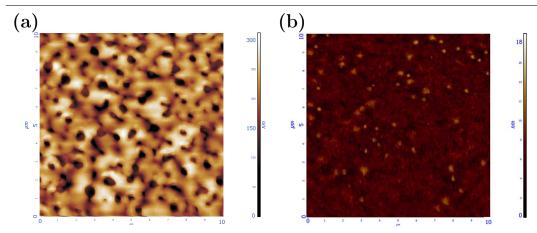

|                           |                                | 3.3.1    | Characterization of Ultra-Thin Poly(vinylidenefluoride-    |     |

## 1 Introduction

Organic electronic devices, have been the focus of several studies in recent years, <sup>2,30,62,68,80,81,124,125,131</sup> and follow the same working principles as their inorganic predecessors. Classical inorganic electronics are based on the semiconducting properties of silicon and have been studied since the mid-20th century. <sup>71,88,96,113</sup> The combination of the semiconductor with an insulator creates a two layer structure, usually referred to as metal-insulator-semiconductor (MIS) or metal-oxide-semiconductor (MOS) device. Those devices are of great interest because they have the same structure as MOS field-effect transistors (MOSFETs or just FETs), which may be used in integrated circuits. The importance of FETs for electronic applications is based on the accumulation and depletion behavior at the semiconductor/insulator interface.

Large parts of the theory, initially developed for the evaluation of inorganic devices, appear to be still applicable to organic-based MIS structures, including organic field-effect transistors (OFETs). <sup>2,68,81,125,131,133</sup> Tsumura *et al.* <sup>133</sup> was one of the first to fabricate an organic FET based on polythiophene as the semiconductor and showed that the current-voltage characteristics are virtually identical to those of conventional inorganic FETs.

For the operation of organic as well as inorganic FETs, it is important to understand the physical processes related to the accumulation and depletion behavior, such as the charge mobility and charge trapping. The accumulation and depletion behavior can be well studied in MIS devices, which have, compared to the FET, a relatively simple design. <sup>96,113</sup> A transition from accumulation towards depletion is indicated by a decrease of capacitance vs. gate voltage (C-V). The position of the onset of this transition is referred to as the flat-band voltage or the threshold voltage and is defined by the zero field condition at the insulator-semiconductor interface. MIS devices are often used to study charge trapping effects at semiconductor interfaces. <sup>88,96</sup> For instance, a permanent change of charge density at the interface results in a shift of the flat-band voltage to either positive or negative values. <sup>88</sup> FETs, on the other hand, measure mainly lateral currents, i.e. lateral charge transport effects, which can be largely influenced by the dielectric and surface properties of the insulator.

In order to obtain OFETs for non-volatile memory applications, a fer-

roelectric gate insulator  $^{48,77,79,80,102}$  has been incorporated into the field-effect transistor, which is in this case also referred to as ferroelectric field-effect transistor (FeFET). Poly(vinylidenefluoride-trifluoroethylene) (P(VDF-TrFE)) appears to be an ideal candidate for a remanently polarizable gate insulator. The working principle of these devices is to permanently change the charge density at the insulator/semiconductor interface by using a ferroelectric insulator, such as P(VDF-TrFE), which maintains its polarization. In this way the memory device can be kept either in the accumulation or depletion  $^{102}$  mode, which defines the *on* and *off* states, respectively.

Indeed, P(VDF-TrFE) based FeFETs and MIS devices have been studied in combination with organic  $^{71,77,124}$  as well as inorganic semiconductors  $^{48,62}$ . Jung et al.  $^{48}$  demonstrated, by using an additional gate electrode, that these kind of devices can be fabricated with an ultra thin P(VDF-TrFE) spincast film, which allows for gate-voltage operation well below 10V. The disadvantage of organic non-volatile memory devices, at the present stage of development, is caused by the relatively low mobility of the semiconductor. One limitation for the clock frequency at which memory devices and transistors can be operated is the mobility, which must be high enough to ensure a complete transfer of charge.  $^{114}$  Sirringhaus et al.  $^{111}$  and Cho et al.  $^{15}$  have reported mobilities for poly(3-hexylthiophene) (P3HT) of  $\approx 0.1~\rm cm^2(sV)^{-1}$  which is high for organic materials but still much lower than for inorganic semiconductors. Silicon for instance shows mobilities well above  $100~\rm cm^2(sV)^{-1}$ . Hence, applications for high performance electronics, such as Notebooks etc., which require a high clock rate, are not in reach so far.

However, the advantage of organic materials is their processability.  $^{22}$  Apart from the evaporation of electrodes, organic based electronics can be easily processed by spincoating or printing techniques. Furthermore, they can be placed on flexible substrates. This makes non-volatile data storage devices based on organic FeFETs especially attractive for low cost memory devices such as Radio-frequency identification (RFID) and smart tags. Promising switching characteristics and retention times for P(VDF-TrFE) based FeFETs have been published amongst others  $^{55,108,109}$  by Gelinck et al.  $^{35}$  as well as Naber et al.  $^{79}$  They have reported switching times in the millisecond range as well as retention times of several hours, which led to a detoriation of currents in the on state and to a concomitant decrease of the on/off ratio by 30%. However, in order to obtain devices suitable for commercial applications, it is especially important to have long data retention times of months or maybe even years.

For the stability of the *on* and *off* state it is essential to have a trap-free semiconductor/insulator interface as well as a stable remanent polarization of the insulator. Nicollian and Goetzberger<sup>96,116</sup> (NG) distinguishes here between charges that are fixed at the insulator interface and those that are trapped in fast states (also known as interface traps, interface states or surface states).

The latter type of traps can be considered as energetically less deep than those associated with fixed charges.

Fixed charges reside at the interface and have to be compensated by the external voltage source leading to a a threshold voltage shift, i.e. instability. This threshold voltage shift may change, depending on the operation time and bias stress of the device. Singh  $et\ al.^{109}$  demonstrated a strong shift of threshold voltage in the output characteristics of a FeFET with an increasing number of measurement cycles. This shift can eventually lead to a detoriation of the on/off ratio and limits the retention time of the memory device. In order to understand such instabilities and determine the nature of traps, organic semiconductors have been studied mainly in combination with several nonferroelectric organics (such as polysilsesquioxane(PSQ) and polyimide (PI)), as well as inorganic (SiO<sub>2</sub>) insulators. Threshold voltage shifts and the dynamics of charge trapping were further investigated by Salleo  $et\ al.^{106}$  and Taylor  $et\ al.^{124}$  However, other authors have also published on this issue for organic  $^{54,148}$  as well as inorganic  $^{141,142}$  devices.

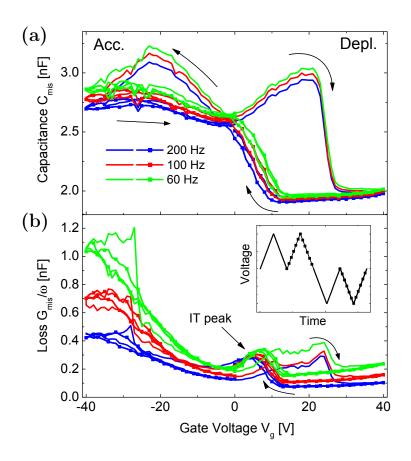

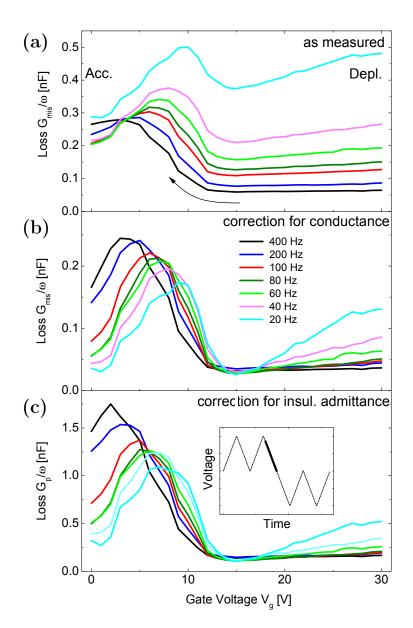

Fast states (or interface traps) can exchange majority charge carriers with the semiconductor bulk. This process may be modulated by the applied probing voltage and, thus, identified by a stretch-out of the C-V plot and a concomitant peak in the loss-voltage characteristic.  $^{96}$  Torres et~al.  $^{132}$  found threshold voltage instabilities for accumulation as well as depletion voltages caused by fast states at P3HT/PI interfaces. Similar results of hole trapping near the interface have been reported by Salleo et~al.  $^{106}$  who studied the organic semiconductor poly-9,9'dioctyl-fluorene-co-bithiophene (F8T2). Further studies on P3HT-based MIS devices were carried out by Alves et~al. using a method developed by NG to retrieve interface trap densities for majority charge carriers, i.e. holes.

The NG technique may yield good approximations of interface trap density, however, it probes only the interaction with the majority charge carriers. In order to develop organic ambipolar semiconductors, it is also important to understand and study the trapping of minority charge carriers. This type of charge carriers usually make only negligible contribution to the overall charge trapping process. Hence, the trapping process of minority charge carriers can not be studied with the NG method. Therefore, Taylor et al. 125 investigated the presence of electron traps at P3HT/PI interfaces by means of photo-excitation and with that made a contribution towards the development of n-channel and ambipolar transistors as well as organic photo transistors. Apart from the flatband voltage instabilities, interface traps may also influence the charge transport behavior which is mainly confined to the interface region in FETs. Zen et al. 143 showed that the deposition of a hexamethyldisilazane (HMDS) monolayer onto the SiO<sub>2</sub> insulator may passivate hole traps leading to an increase of majority charge carrier mobility. Furthermore Chua et al. 18 demonstrated that the elimination of electron traps at the interface may result in n-type behavior in organic semiconductors, which were thought to show only p-type activity.

The above discussed instabilities of the threshold voltage were mainly observed by trapping of either holes or electrons at the insulator/semiconductor interfaces in devices with a non-ferroelectric gate insulator. However, as already mentioned, non-volatile memory devices require a remanently polarizable gate insulator, such as P(VDF-TrFE). For these devices another source of instability was proposed by Naber et al. 76,79,80 They suggested that the lack of stable remanent depletion behavior of the studied P3HT/P(VDF-TrFE)-based MIS and FeFET devices is caused by the depolarization of the ferroelectric insulator at depletion voltages. They argued that the ferroelectric polarization of the insulator requires electrons at the insulator/semiconductor interface, which can not be supported by the p-type semiconductor P3HT. Hence, it was concluded, this lack of compensation charges would lead to the depolarization of the insulator. However, in the course of this work it will be clearly demonstrated, that the remanent polarization is stable in MIS devices in depletion mode. <sup>50</sup> Furthermore, it will be shown that enough electrons are permanently trapped (fixed) near the interface, to completely compensate (even slightly overcompensate) the ferroelectric polarization.

Naber et al. as well as Meijer et al. <sup>68</sup> have considered the presence of a small number of permanently trapped electrons at the semiconductor/insulator interface, but only for non-ferroelectric gate insulators. However, the scientific opinion of Naber et al. concerning fixed charges at ferroelectric P(VDF-TrFE) interfaces is ambiguous. They reject the idea that fixed charges might cause instabilities using the argument that charge injection into P(VDF-TrFE) 'is less probable because it is a wide band gap insulator' <sup>79</sup> on one side, but also acknowledge the possibility of entrapment <sup>80</sup> of electrons on the other side.

A very recent study by Nakajima  $et~al.^{84}$  about the switching dynamics of P(VDF-TrFE) layers in MIS devices based on  $\alpha,\omega$ -dihexylsexithiophene (DH-6T) has also produced evidence for a 'screening charge' situated at the semiconductor/insulator interface. Furthermore, Nakajima et~al. suggest a lack of ferroelectric depolarization but gives no further statement about the stability of the ferroelectric polarization in the depletion regime. Rather, they consider the influences of the depolarization field  $^{66}$  induced by the lack of compensation charges in the semiconductor under depletion.

A similar effect was discussed by Lim  $et\ al.^{62}$  and Ma  $et\ al.^{64}$  in terms of the introduction of a second dielectric layer as a additional blocking layer into a MIS device. Such a layer lowers the leakage current but constitutes another issue for the design of reliable memory devices. Since additional buffer layer may induce a depolarization field under short circuit condition or reduce the voltage drop over the active P(VDF-TrFE) layer when voltage is applied, these layers need to be further optimized as discussed, for instance, by Henkel  $et\ al.^{40}$  Indeed, in organic based electronics, thin blocking layers were successfully

implemented for silicon oxide surfaces and lead to an enhancement of charge carrier mobility due to the reduction of trap sites at the interface. <sup>18,146</sup>

As mentioned above the work presented in this thesis yields strong evidence for the stability of the ferroelectric polarization of the P(VDF-TrFE) gate insulator in MIS devices and the presence of permanently fixed charges at the interface. Therefore, since a depolarization can no longer account for the observed lack of stable depletion mode in P3HT/P(VDF-TrFE)-based MIS devices, it appears necessary to modify the interface, to minimize the effect of charge entrapment. Further, it was shown, the insulator/semiconductor interface contains, in addition to the fixed electrons, also a density of hole traps, usually referred to as fast states. <sup>116</sup>

In this thesis P(VDF-TrFE) based MIS and FET structures have been studied by means of different dielectric characterizations, including capacitance spectra, TSC measurements, C-V and I-V characteristics of MIS devices as well as FET characteristics.

The thesis consists of three parts:

- chapter 2 is an introduction into the theoretical background including a short summary about morphology and important properties of P3HT and P(VDF-TrFE) and an introduction into the physics of MIS structures,

- chapter 3 provides details about the preparation and characterization of the insulator as well as MIS structures

- chapter 4 and 5 present the study of ferroelectric polarization by different dielectric measurements and the final conclusion, respectively.

For clarity, chapter 4 is further subdivided into five sections, each providing a more specific introduction into the individual field of research, the presentation of results and discussion as well as conclusions.

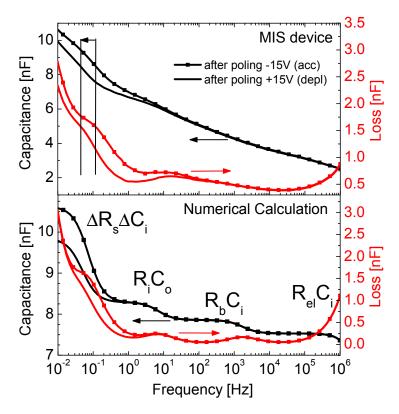

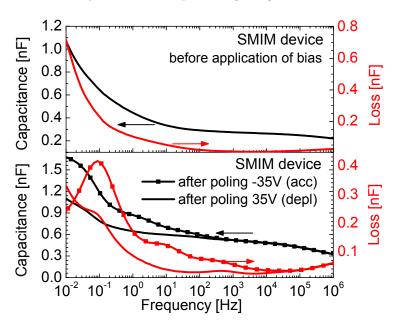

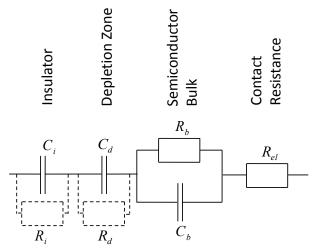

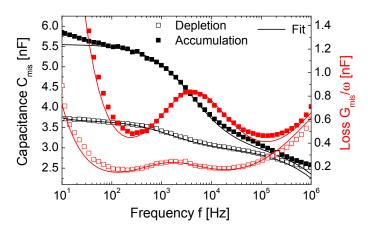

Section 4.1 presents a study of the all-organic MIS device with the ferroelectric P(VDF-TrFE) by means of capacitance spectra. Here, the spectra were measured under different biases, showing the effect of charge accumulation and depletion on the Maxwell-Wagner peak. The position and height of this peak shows clearly the lack of stable depletion behavior and the decrease of mobility when increasing the depletion-zone width, i.e. upon moving into the P3HT bulk.

In section 4.2 C-V and current-voltage (I-V) measurements have been carried out on all-organic MIS structures with the ferroelectric polymer P(VDF-TrFE) as the gate insulator. When the structure was driven into depletion, a positive flat-band voltage shift was observed arising from the change in polarization state of the ferroelectric insulator. When driven into accumulation,

the polarization was reversed. It is shown that the two polarization states are stable i.e. no depolarization occurs below the coercive field. However, negative charge trapped at the semiconductor-insulator interface during the depletion cycle masks the negative shift in flat-band voltage expected during the sweep to accumulation voltages.

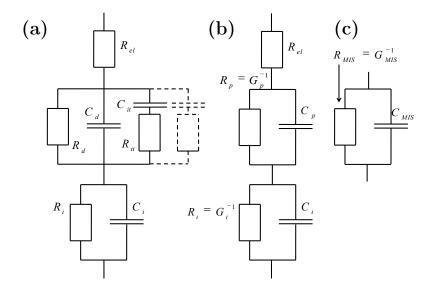

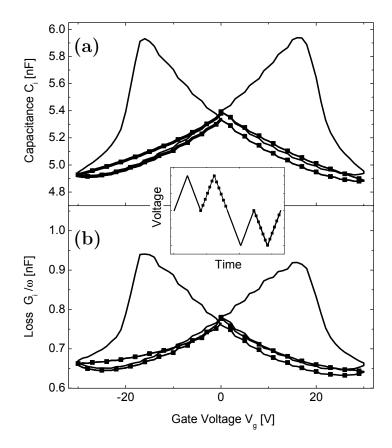

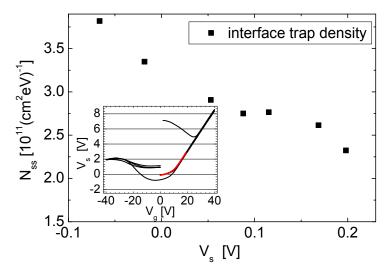

Section 4.3 shows that by means of a unipolar/bipolar voltage pattern the influence of the ferroelectric switching on the C-V data of the MIS device can be removed and that the conductance method<sup>96,113</sup> can be applied to determine the interface trap density. Hence, it turns out, the P3HT/P(VDF-TrFE) interface contains both the structurally fixed positive charges (see section 4.2) and a distribution of fast traps sites for majority charge carriers, i.e. holes.

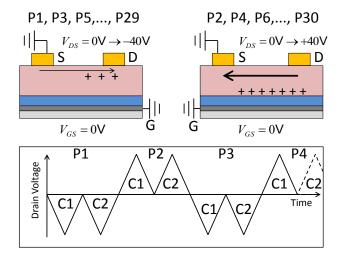

Section 4.4 presents the study of the output and transfer characteristics of FeFETs. The FeFET measurements confirm the previous results on the stability of the ferroelectric polarization and the presence of negative charges at the insulator/semiconductor interface. Furthermore, the output characteristics suggest the permanent trapping of negative charges at the interface during the first poling steps, leading to an increased drain current for negative drain voltages with increasing number of poling cycles.

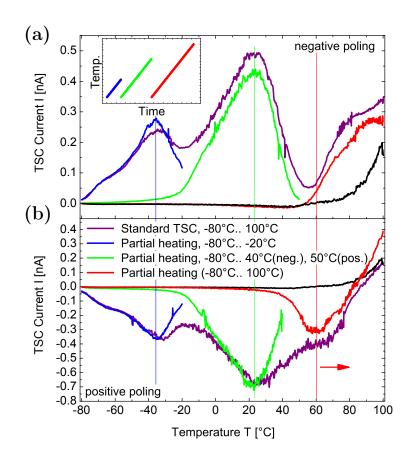

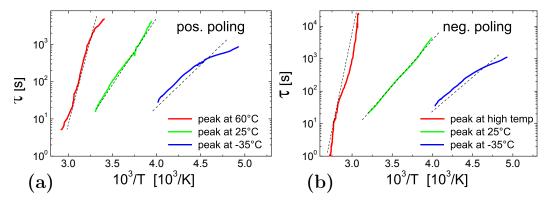

In section 4.5 the MIS device is subjected to thermally-stimulated current (TSC) measurements. Here three relaxations at −35°C, 25°C and 50°C are measured. The first two are assigned to the glass transition and an interface polarisation effect at crystallite boundaries, respectively. This interface polarization presents further evidence for the stability of the polarization under depletion voltages. The exact origin of the relaxation above 50°C could not be inferred from this measurement. However, it might be related to the charge trapping at the semiconductor/insulator interface.

## 2 Theoretical Background

## 2.1 Morphology and Related Properties of the Materials

Sections 2.1.1 and 2.1.2 present an introduction into morphology and related properties of P3HT and P(VDF-TrFE), respectively. The conformation of the P3HT molecules strongly influence the electronic properties of the semiconducting layer. The crystalline modifications of PVDF and P(VDF-TrFE) are also important, since they have a significant effect on the ferroelectric properties of the spincoated film. Section 2.1.3 gives an introduction into the measurement of the ferroelectric polarization in P(VDF-TrFE) films by current-voltage characteristics.

#### 2.1.1 Poly(3-Hexylthiophene)

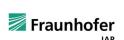

Figure 2.1: (a) Regio regular conformation of P3HT. The hexyl groups are arranged in a Head-to-Tail(HT) coupling. The position of the hexyl group marks the Head and the opposite side the Tail of the thiophene ring. (b) (Source: Zen *et al.* <sup>145</sup>) Morphology of P3HT for high and low molecular weight.

Structure and morphology of regionegular poly(3-hexyl thiophene) (rrP3-HT) is shown in Fig. 2.1(a) and (b). The  $\pi$ -bonds form the conjugated back-

bone of P3HT. The length of an unperturbated backbone is referred to as conjugation length. Since the  $\pi$  electrons are delocalised and may move along these conjugated backbones the conjugation is mainly responsible for the electronic and optical properties of rrP3HT. The hexyl group, however, is isolating since it lacks delocalised electrons due to its  $\sigma$ -backbone. Nevertheless, the position of the hexyl group is important for the conjugation of P3HT, since it influences the selforganised arrangement of the P3HT chain as has been shown by Prosa et al. 101 and Bao et al., Siringhaus et al. 110,111 as well as others. 53 Self organisation of rrP3HT into a planar conformation makes it feasible to obtain relatively high mobilities in solution processed thin films. 3

The position of the hexyl group marks the head of the thiophene ring and the opposite side its tail. The rrP3HT molecule assembles in Head-to-Tail(HT) coupling. That kind of arrangement of side chains allows P3HT to aggregate in highly ordered domains, which are embedded in to an amorphous matrix. In the disordered matrix, charge transport is mainly limited by hopping processes. 110 Zen et al. 146 have studied the aggregation as well as its effect on the hole mobility of P3HT for different molecular weights and developed morphology schemes for high and low molecular weights, given in Fig. 2.1(b). 20,65 He showed that the mobility increases with the molecular weight. Most of the crystalline domains in the low-molecular weight layers are isolated by the amorphous matrix, and transport will be mainly between the few interconnected domains. However, in the high molecular weight layers, a larger number of chains organizes in ordered domains and creates therewith many possible pathways for the carriers to travel. 145

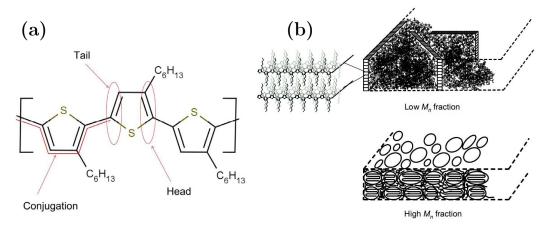

Figure 2.2: Energy levels of an isolated molecule, i.e. gas phase (left), a molecular crystal (middle) and an amorphous solid. The width  $2\sigma$  of Gaussian distribution of localized states (density of states) N(E) defines the the band width of the HOMO and LUMO level. (Source: 'Physics of Organic Semiconductors'  $^{10}$ )

The above mentioned  $\pi$  bonds in organic semiconductors, such as P3HT, give rise to energetic levels, i.e. molecular states: the highest occupied molecular orbital (HOMO) and the lowest unoccupied molecular orbital (LUMO), as illustrated in Fig. 2.2.  $^{4,9,10,146}$  In unordered organic materials the sum off all these levels form a Gaussian distribution of localized states. This distribution of HOMO and LOMO levels can be, in analogy to inorganic semiconductors

physics, considered as valence and conduction bands. The charge transport is, unlike in inorganic semiconductors, rather incoherent and realized by hopping, i.e. Poole-Frenkel effect, from one state to another. <sup>6,32</sup> Hopping describes a thermally activated tunneling process between chains or chain segments, i.e. localized states, and is therefore less efficient as the coherent charge transport in crystalline structures. <sup>5,6,32,41,99</sup>

#### 2.1.2 Polyvinylidene Fluoride and Its Copolymer

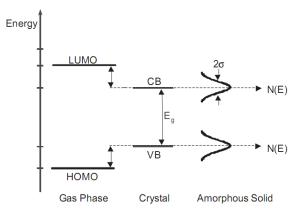

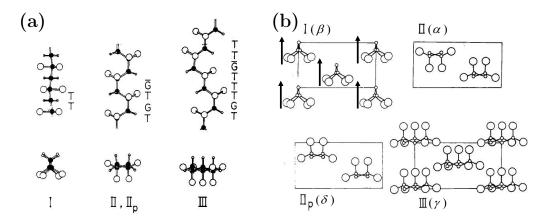

Figure 2.3: (Source: Tashiro *et al.* <sup>121</sup>) Molecular structure (a) and crystalline modification (b) of PVDF which are referred to as Form:  $I(\beta)$ ,  $II(\alpha)$ ,  $II_p(\delta)$  and  $III(\gamma)$ . The arrows in (b) indicate the net dipole moment of the  $\beta$ -form.

Fig. 2.3(a) and (b) illustrates the four crystalline modifications of PVDF, referred to as form I ( $\beta$ ), II ( $\alpha$ ), II<sub>p</sub> ( $\delta$ ), which is the polar configuration of form II, and III ( $\gamma$ ). <sup>85</sup> The  $\alpha$  and  $\delta$  PVDF have the same molecular conformation  $\bar{G}TGT$  but differ in the chain arrangement. The unit cell of  $\alpha$  and  $\delta$  PVDF, as depicted in Fig. 2.3(b), consists of two chains, each with an associated dipole moment. In  $\alpha$  PVDF the dipole moment of each chain is oriented into opposite direction with respect to its neighbors, thus, the net dipole moment is zero. The parallel orientation of the dipole moments yields the polar unit cell of  $\delta$  PVDF. A non-zero net dipole moment is also associated to the  $\gamma$  PVDF, which requires a  $TTTGTTT\bar{G}$  molecular structure. Melt processed films consist predominantly of the non-polar  $\alpha$  PVDF, since it constitutes the thermodynamically most stable conformation. In this type of conformation the molecules are folded many times and are, assembled in the form of lamellae, which may form circular structures (> 100  $\mu$ m) know as spherulites. <sup>63</sup>

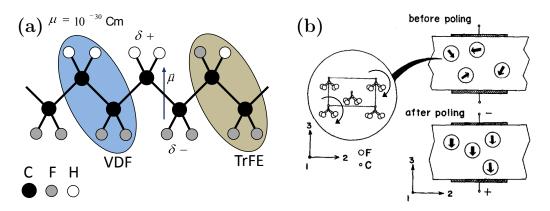

Most interesting, from a technical point of view, is the large net dipole moment associated to the  $\beta$  PVDF. Its crystal structure is built of parallel aligned molecules with an all-trans (TT) conformation. Each (CH<sub>2</sub> – CF<sub>2</sub>)<sub>n</sub> repeat unit carries a vacuum dipole moment of  $\mu = 7 \times 10^{-30}$  Cm induced by the negative fluorine ( $\delta$ +) and positive hydrogen atoms ( $\delta$ -) as depicted in

Fig 2.4(a). The summation of  $\mu$  over one unit cell volume yields a theoretical polarization of 130 mCm<sup>2</sup>.<sup>33</sup> Hence, the TT conformation is the reason for the large polarizations of  $\beta$  PVDF films and may be obtained by stretching<sup>1</sup>  $\alpha$ -PVDF films. During the stretching the lamellae conformation of the  $\alpha$ -phase becomes destroyed and the molecules reorient parallel to the drawing direction.

The copolymer P(VDF-TrFE) on the other side, may crystallize mainly in all trans  $\beta$ -phase right from melt or solution. A detailed discussion how the crystallization depends on TrFE content as well as preparation was given by Tashiro et al. 86,121,122 Due to the similarity in the size of hydrogen and fluorine atoms, VDF and TrFE units are randomly distributed along the molecular  $(-CH_2-CF_2)_n-(CH_2-CHF)_m$ -chain to form a random copolymer and cocrystallize into a single crystalline phase analogous to  $\beta$  PVDF (Fig. 2.4(a)).<sup>33</sup> The TrFE units induces small defects in the polymer chain, which lead to the spontaneous all-trans arrangement of the molecule. Since  $\beta$ -phase in P(VDF-TrFE) is formed spontaneously, it is possible to produce solution processed films with high degree of crystallinity well above 50% depending on the amount of chain ordering defects. <sup>26,82</sup> These crystalline domains are then embedded in a noncrystalline amorphous matrix. In contrast to pure PVDF, P(VDF-TrFE) shows a clear Curie temperature, which changes with the mol%-content of TrFE. PVDF, on the other side, does not show a clear Curie temperature, since the the ferroelectric phase melts below the hypothetical Curie point.<sup>33</sup>

Figure 2.4: (a) Schematic of P(VDF-TrFE) molecule in the all trans  $\beta$ -phase. The arrow indicates the vacuum dipole moment of VDF repeat unit. (b) (Source: Tashiro *et al.*<sup>122</sup>) Illustration of the poling process in a crystal domain of P(VDF-TrFE). Arrows indicate the rotation of the molecules around their axis.

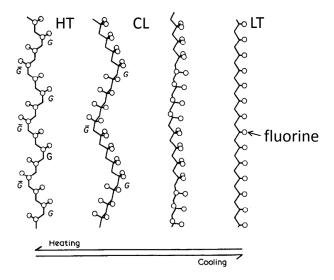

Degree of crystallinity of P(VDF-TrFE) as well as chain conformation may depend critically on the preparation details as well as the TrFE mol% content.  $^{86,121,122}$  Typically three conformations have been reported, referred to

$<sup>^1{\</sup>rm Tamura}~et~al.^{120}$  for instance used PVDF films that were uniaxially stretched up to four times the original length at 65°C.

as high temperature (HT), cooled (CL) and low temperature (LT) phase (refer to Fig. 2.5). The non-ferroelectric HT phase is assumed to be a mixture of different gauge conformations (TG,  $T\bar{G}$ , TTTG and  $TTT\bar{G}$ ) and exists at elevated temperatures. When quickly cooled to room temperature the HT phase may result in CL phase, which consists of gauge and all trans conformations. The LT phase is essentially identical to form I of PVDF (TT) and may be obtained for instance by slow cooling from HT or CL phase, i.e. by annealing. Hence, both conformations, CL and LT, may be found in solution and melt processed films. <sup>86</sup> The 65 mol% VDF copolymer for instance is known to crystallize predominantly in LT phase with some fraction of CL phase. <sup>123</sup>

Figure 2.5: Illustration of molecular high temperature (HT), cooled (CL) and low temperature (LT) conformation of P(VDF-TrFE). The effect of ferroelectric phase transition is due to the large conformational change between the extended all-trans structure (LT) and the contracted chain structure with statistically disordered sequence of trans and gauche bonds (HT). (Source. Tashiro et al. <sup>122</sup>)

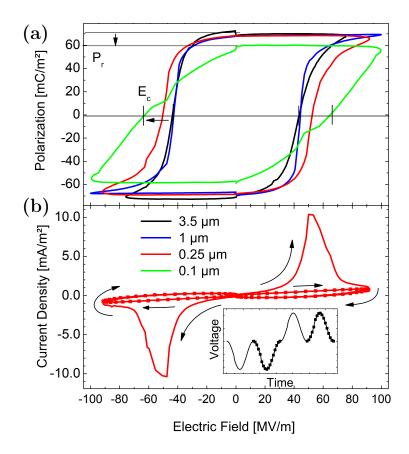

The formation of crystalline  $\beta$ -PVDF gives rise to the ferroelectric polarization of P(VDF-TrFE) films of around 60 mC/m<sup>2</sup> with a coercive field of around 50 MV/m (refer to Fig. 3.7 on page 38).  $^{33,77,136,138}$  This macroscopic effect of remanent polarization is attributed to the large net dipole moment of the  $\beta$ -conformation on one side and the fact that the molecular dipoles can maintain the orientation on the other side. When the coercive field is exceeded, the molecules start to rotate around their axis and align therewith their molecular dipoles along the field lines, as illustrated in Fig. 2.4(b).

The effect of stable polarization, however, is not only a pure intrinsic effect of P(VDF-TrFE) films but may be largely influenced by the presence of charges as discussed in reviews articles by Eberle  $et\ al.^{26}$  and Eisenmenger  $et\ al.^{28}$  Measurements presented in these articles suggest the depolarization of P(VDF-TrFE) films within minutes, when charge injection was prevented

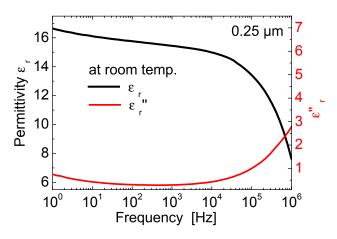

by blocking electrodes. The remanent polarization and the coercive field may further be influenced when the thickness of the P(VDF-TrFE) film is decreased below 0.5  $\mu$ m. Several authors <sup>77,136–138</sup> have shown that the decrease of film thickness leads also to a decrease of remanent polarization, however, increases the coercive field. This behavior is strongly amplified for film thicknesses below a critical thickness of around 0.15 $\mu$ m. The increase of coercive field and the decrease of remanent polarization is related to the increase of surface tension as well as the decrease of crystallinity in ultra thin films, respectively. <sup>77,136–138</sup>

#### 2.1.3 Current-Voltage Characteristics

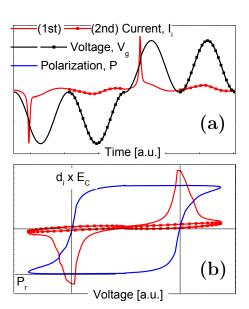

Figure 2.6: Example of the applied unipolar/bipolar voltage pattern and the corresponding current reading (a) of a ferroelectric insulator of thickness  $d_i$  as well as resulting Polarization P (b). Straight line and line with  $\blacksquare$ -symbols indicates the 1st and 2nd unipolar cycle, respectively.

Current-voltage (I-V) characteristics of ferroelectric insulators may contain contributions from the ferroelectric reorientation of the dipoles, pure capacitive effects and contributions from the ohmic conductance of the material. Bauer et al., Dickens et al. but also other authors have demonstrated the separation of these effects by means of a unipolar/bipolar voltage sweep method. For this method a voltage pattern  $V_g(t)$ , as exemplary shown in Fig. 2.6(a), is applied to the sample. The measured current  $I_i = dQ/dt$  for an insulator with capacitance C and a ferroelectric polarization P and resistance R can be written as

$$I_i = C\frac{\mathrm{d}V_g}{\mathrm{d}t} + \frac{\mathrm{d}P}{\mathrm{d}t} + \frac{V_g}{R}.$$

(2.1)

The dielectric constant  $\varepsilon_r$  is related to C by  $C = \varepsilon_0 \varepsilon_r A/d$ , which yields the pure capacitive contribution. The contribution of the polarization P to the measured current is dP/dt. The expression  $V_g/R$  represents the contribution of the ohmic resistance R.

A reversal of the ferroelectric polarization, when the coercive field is exceeded during an initial voltage sweep, will manifest itself as peak in the I-V plot. When a second unipolar sweep is undertaken, if P remains unchanged no current peak will be observed, in  $I_i$ , even though the coercive field is exceeded. Thus, if two unipolar voltage loops are applied to a ferroelectric only the current reading of the first contains a contribution of the switching of the ferroelectric dipoles. Therefore, the pure polarization current  $I_p$  may be obtained by subtracting the current reading of the second loop  $I_2$  from the first loop  $I_1$ , i.e.

$$I_{p} = \underbrace{A \frac{\mathrm{d}P}{\mathrm{d}t} + C \frac{\mathrm{d}V}{\mathrm{d}t} + \frac{V}{R}}_{=I_{1}} - \underbrace{\left(C \frac{\mathrm{d}V}{\mathrm{d}t} + \frac{V}{R}\right)}_{=I_{2}}$$

$$I_{p} = A \frac{\mathrm{d}P}{\mathrm{d}t}. \tag{2.2}$$

Finally, the integration

$$P(t) = \frac{1}{A} \int_{t_0}^{t} I_p(t_m) dt_m$$

(2.3)

yields the polarization. P(t) can also be expressed as  $P(V_g)$ , since time and applied voltage  $V_g$  are measured simultaneously, i.e.  $V_g$  can be expressed as function of t. With knowledge about the film thickness  $d_i$ ,  $V_g$  can of course also rewritten into the corresponding field  $E = V_g/d_i$ . For this type of measurement, the coercive field can not be measured directly and will, therefore, be defined by the position, that bisects the area of the polarization peak, i.e.  $P_{max}/2 = P(E_c)$ . Hence, the polarization for the positive and negative voltages, as exemplified in Fig. 2.6(b), is given with  $P(V_g) \pm P_{max}/2$ .

#### 2.2 MIS Capacitance Curves

#### 2.2.1 Ideal Capacitance-Voltage Characteristics

In the following section the basic concepts of physics in MIS structures shall be recapitulated. Parts of the theory for inorganic MOS devices<sup>89,117</sup> appear still to be applicable to organic<sup>81,124,126,131</sup> electronics. A comprehensive discussion of the physics of inorganic MIS (or MOS) structures may be found for instance in *Physics of Semiconductor Devices*. <sup>117</sup>

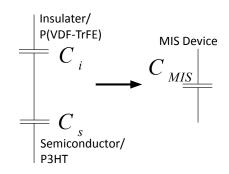

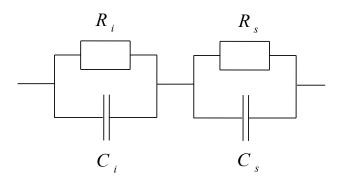

Figure 2.7: Equivalent circuit representing MIS device.

A common approach to describe and understand the capacitive behavior of MIS

devices is a model based on an equivalent circuit. A simple representation of a MIS structure by such an equivalent circuit is obtained by the series combination of the capacitance representing the semiconductor  $C_s$  and the insulator  $C_i$ , as depicted in Fig. 2.7. The resulting capacitance of the MIS device is then expressed by

$$C_{\rm MIS} = \frac{C_i C_s}{C_i + C_s}. (2.4)$$

Assuming a linear response of the insulator, its capacitance may be written as  $C_i = \varepsilon_0 \varepsilon_i A/d_i$  with  $\varepsilon_0$ ,  $\varepsilon_i$ , A and  $d_i$  as the permittivity of free space, dielectric constant, device area as well as insulator thickness, respectively. In the absence of mobile charge carriers the capacitance of the semiconducting layer may also be expressed in terms of its dielectric constant  $\varepsilon_s$  and film thickness  $d_s$  with  $C_s = \varepsilon_0 \varepsilon_s A/d_s$ . This expression however, is only valid for a fully depleted semiconductor or if charges, for what reason ever (blocking layer), can not be injected into the semiconductor. A complete description of  $C_s$  will be given below.

Using the continuity condition for the electrical displacement at the interfaces of the dielectrics the series combination of capacities yields $^2$

$$\frac{1}{C_{\text{MIS}}} = \frac{1}{C_i} + \frac{1}{C_s}$$

$$\frac{V_{\text{MIS}}}{Q_s} = \frac{V_i}{Q_s} + \frac{V_s}{Q_s}$$

$$V_{\text{MIS}} = V_i + V_s$$

$$(2.5)$$

<sup>&</sup>lt;sup>2</sup>The electric capacitance C of a dielectric material is defined as ratio of charges at the dielectric surface Q to voltage V on the dielectric,  $C = \frac{Q}{V}$ .

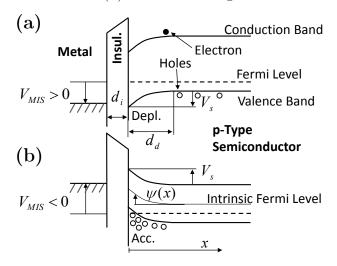

with  $V_{\rm MIS}$ ,  $V_i$ ,  $V_s$  and  $Q_s$  as the voltage drop over the MIS device, insulator, semiconductor as well as the number of charges at the semiconductor/insulator interface, respectively. The voltage drop over the semiconductor  $V_s$  is also referred to as band bending and is depicted in Fig. 2.8 for depletion (a) and accumulation (b).  $^{38,90,117}$  Through an ohmic contact between electrode and

Figure 2.8: Band diagram of an ideal MIS structure at positive (a), i.e. depletion, voltage  $V_{\rm MIS} > 0$  and negative, i.e. accumulation, voltage  $V_{\rm MIS} < 0$ . The band bending at the semiconductor interface leads in case (a) to a depletion zone of width  $d_d$ . A further depletion causes inversion and increase of number of electrons (minority charge carriers).

semiconductor (not depicted in Fig. 2.8) charges can be injected, which may then lead to accumulation or depletion of the semiconductor interface, for negative and positive gate voltages  $V_{\text{MIS}}$ , respectively. The depicted bending of the bands, described by  $\psi(x)$ , is a result of the total space charge distribution  $\rho(x)$  in the semiconductor. The total number of space charges, i.e space charge density  $\sigma = Q_s/A$ , with A as the device area, depends on  $\psi(x = 0) \equiv V_s$ . Solving the one dimensional Poisson equation  $^{90,117}$

$$\frac{\mathrm{d}\psi(x)}{\mathrm{d}x} = -\frac{\rho(x)}{\varepsilon_s} \tag{2.6}$$

for the surface potential at the semiconductor/insulator interface yields the space charge density

$$\sigma(V_s) = -\operatorname{Sign}(V_s)\sqrt{2} \left(\frac{\varepsilon_0 \varepsilon_s}{\beta L_b}\right) \left[\underbrace{\left(e^{-\beta V_s} - \beta V_s - 1\right)}_{\text{majority charges}} + \underbrace{\left(\frac{n_i}{N_a}\right) \left(e^{\beta V_s} - \beta V_s - 1\right)}_{\text{minority charges}}\right]^{1/2}$$

(2.7)

with  $n_i$ ,  $N_a$ ,  $L_b = \sqrt{\varepsilon_0 \varepsilon_s / \beta q N_a}$  and  $\beta = q/KT$  as intrinsic charge carrier concentration, doping density, Debye length and reciprocal thermal potential, respectively. The derived charge density  $\sigma(V_s) = Q_s/A$ , plotted in Fig. 2.9, yields a good description of the accumulation, depletion and inversion behavior of the semiconducting layer. Equ. 2.7 further be utilized to calculate capacitance of the semiconductor

$$C_s = \frac{\mathrm{d}Q_s}{\mathrm{d}V_s}.\tag{2.8}$$

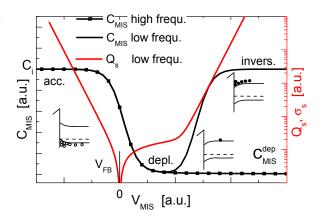

This expression may now be used to calculate the capacitance of an ideal MIS system as it is measured with the probing signal  $V_{sig}(t) = V_{\text{MIS}} + V_{pr} \sin(\omega t)$ . The term  $V_{pr} \sin(\omega t)$  represents a small alternating voltage signal to probe the capacitative response of the MIS device, which is driven into either accumulation or depletion by the application of the semi-DC voltage signal,  $V_{\text{MIS}}$ . The general response of a MIS device as calculated by means of Equ. (2.4),(2.7) and (2.8) can be found in Fig. 2.9. Here, four regions may be distinguished: the

Figure 2.9: Schematic plot of C-V characteristics for a MIS structure as measured at high and low probing frequencies with corresponding variation of number of space charges, i.e. space charge density, in a p-type semiconductor, calculated with Equ. (2.7). <sup>90,117</sup> The band diagrams show the accumulation, inversion and depletion case.

accumulation, depletion, weak inversion and strong inversion. In accumulation, i.e. at negative voltages for a p-type semiconductor, the large number of charges within the semiconductor lead to  $C_s \to \infty$  and consequently  $C_{\text{MIS}} \approx C_i$ . An increase towards positive voltages yields a decrease of  $C_{\rm MIS}$ , caused by the depletion and a concomitant decrease of the semiconductor capacitance, which is, in depletion, well approximated by  $C_s = \varepsilon_0 \varepsilon_s A/d_d$ . The further increase of positive voltages may cause a inversion layer formation and hence an increase of minority charge carriers (electrons) leading finally to an increase of the MIS device capacitance towards  $C_{\text{MIS}} \approx C_i$ . Such a behavior, however, is only measured at low probing frequencies, when generation-recombination rates of minority charge carriers and the charge exchange with the inversion layer can follow the probing signal. 117|3 At high measurement frequencies the minority charge carriers can no longer follow the signal, leading to a decrease of  $C_s$  and to the high frequency C-V characteristic also shown in Fig. 2.9. In deep depletion, the maximum depletion zone width is defined by the semiconductor thickness, i.e.  $d_d = d_s$ , yielding finally a MIS device capacitance of

$$C_{\text{MIS}}^{dep} = \frac{A\varepsilon_o\varepsilon_i}{\varepsilon_i d_s + \varepsilon_s d_i}.$$

(2.9)

Such C-V characteristics are typically found for MIS devices, based on organic semiconductors. <sup>37,80,84</sup> The lack of inversion behavior, i.e. increase of capacitance, at depletion voltages is attributed to the lack of minority charge

$<sup>^3</sup> The response time for minority charge carriers in silicon at room temperature is typically <math display="inline">0.001s-1s.\,^{91}$

carriers. A phenomenon probably caused by trap sites in the semiconductor near the interface. Chua et al. <sup>18</sup> have provided evidence that silanol groups at the SiO<sub>2</sub> gate dielectric interface in OFETs may be responsible for the trapping of electrons in several organic p-type semiconductors. Also polyimide (PI) insulators may lead to strong electron trapping near at the P3HT/PI interface as discussed by Taylor et al. <sup>125</sup> This charge trapping could be identified by its characteristic flat-band voltage shift, which will be further discussed in the next section 2.2.2. Hence, based on these results it may be concluded that electrons are likely to be present in most organic p-type semiconductors, however, basically immobile due to trapping. <sup>125</sup> Due to this trapping, electrons are unable to follow the ac probing signal and are also not available as inversion charges. The high frequency C-V characteristics as derived for inorganic MIS structures <sup>90</sup> reflects the lack of response of minority charge carriers, i.e. electrons, and yields therefore a valid description for the typically measured C-V characteristics of organic MIS structures.

To understand the working principle of a non-volatile memory device, the ferroelectric polarization behavior of the insulator has to be considered. A typical polarization curve of a P(VDF-TrFE) film is exemplified in Fig. 2.6. When introducing a ferroelectric insulator into the MIS stack, Equ. (2.5) has to be modified to account for the nonlinear behavior of the ferroelectric polarization  $P(E_i)$  (in  $[C/m^2]$ ) upon the field at the insulator  $E_i$ . Details about the derivation may be found in work of Miller  $et\ al.^{71-73}$  or in the Appendix.

After modifying Equ. (2.5),  $V_{\rm MIS}$  at the in MIS stack can be described with

$$V_{\text{MIS}} = V_s - \sigma(V_s) \frac{d_i}{\varepsilon_0 \varepsilon_i} - P(E_i) \frac{d_1}{\varepsilon_0 \varepsilon_i}.$$

(2.10)

Consequently, the field at the insulator is given by

$$E_i = -\frac{\sigma(V_s) + P(E_i)}{\varepsilon_0 \varepsilon_i}.$$

(2.11)

Equ. (2.7), (2.10) and (2.11) yield a complete theoretical description of the capacitative behavior of the MIS structure and may be used to calculate the theoretical C-V characteristics (refer to Appendix). Although, such a numerical description will not be presented in this thesis, it is still worthwhile to consider Equ. (2.10) to gain an insight into the working principle of non-volatile memory devices. For this purpose it shall be assumed that, a positive or negative voltage was applied to the MIS system, large enough to exceed the coercive field  $E_c$  of the insulator into the corresponding direction. I this limit  $P(E_i)$  becomes basically constant and can be replaced by the remanent polarization  $P(E_i) = P_r = Q_p/A$ . Hence, the polarization term in Equ. (2.10) can be simplified

$$P_r \frac{d_i}{\varepsilon_0 \varepsilon_i} = \frac{Q_p}{C_i} = V_{\text{FB}} \tag{2.12}$$

with  $Q_p$  as number of remanent charges at the insulator interface, induced by the ferroelectric polarization of the insulator. In principle,  $Q_p$  may now act as fixed charge, influencing a shift of the threshold voltage, denoted as  $V_{\rm FB}$ . Depending on the polarization direction,  $Q_p$  can be negative or positive and cause stable accumulation or depletion of the semiconductor, respectively (assuming a p-type). In other words, if the external voltage is removed, i.e.  $V_{\rm MIS} = 0$  V, then  $V_{\rm FB}$  constitutes an internal voltage source, influencing a field and with that a band bending at the semiconductor interface. Thus, once the coercive field has been exceeded, the molecular dipoles remain in their orientation and keep the device in accumulation or depletion. This effect may then be used in a FET configuration, where it causes a stable on or off state of the device. The phenomenon of threshold voltage shift, i.e trapped charges, on the C-V will be further considered in the following section.

It shall be mentioned again that the above consideration is only valid, once the coercive field has been exceeded and the polarization has been stabilized. The simplification becomes incorrect at the coercive field, i.e. when the polarization is changed. At this position,  $P(E_c \approx E_i)$  strongly depends on the field and needs to be numerically evaluated.<sup>71</sup>

# 2.2.2 Effect of Interface Charges on Current-Voltage Characteristics

C-V characteristics not only provide information about the state of accumulation and depletion in the semiconductor layer, but also about the presence of interface charges, at the semiconductor/insulator interface.  $^{96,127}$  In principle it is possible to discriminate between structurally fixed (or deeply-trapped) charges  $Q_f$ , which are immobile under an applied field and interface state charges  $Q_{it}$ , which strongly depend on  $V_s$ . The latter type of charge trap is also known as fast states or surface states,  $^{116}$  which are energetically less deep than the structurally fixed charges.

The presence of fixed charges leads to band bending at  $V_{\rm MIS}$  = 0 and has to be compensated by an additional voltage to realize the flat-band condition. This additional bias causes a voltage shift of the ideal C-V characteristic, referred to as flat-band voltage shift

$$V_{\rm FB} = -\frac{Q_f}{C_i} + \underbrace{\phi_{ms}}_{=\phi_m - \phi_s} . \tag{2.13}$$

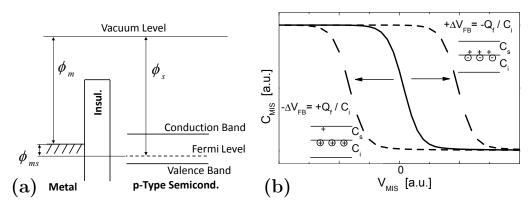

For the sake of completeness, Equ. (2.13) also contains a term representing the difference between the metal and semiconductor work functions, denoted as  $\phi_m$  and  $\phi_s$ , respectively. The band diagram of metal and semiconductor with its work functions before they come into contact is given in Fig. 2.10(a).

Fig. 2.10(b) shows the effect of positive and negative fixed interface charges on the C-V curve. At this point it shall be just mentioned that  $Q_f$  in principle is a net charge, which may consist of various type of charges having different physical properties such as polarity and electric field dependence.<sup>4</sup> In section 4.2 the idea of different type of charges will be adapted and further modified to model polarization charges of the P(VDF-TrFE) insulator as well as structurally fixed interface charges. This model about different charge types is also based on the considerations given at the end of the last section 2.2.1, were the effect of remanent polarization charge was discussed.

Figure 2.10: (a) Band diagram of metal and semiconductor before the contact making with semiconductor and metal work function, denoted as  $\phi_s$  and  $\phi_m$ , respectively. (b)Effect of structurally fixed charges  $\pm Q_f$  on the C-V characteristics. Negative or positive charges cause shift of the flat-band foltage  $\Delta V_{\rm FB}$  towards positive or negative gate voltages  $V_{\rm MIS}$ .

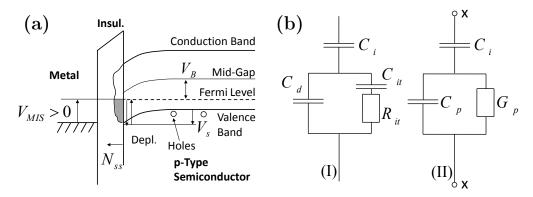

Interface traps (fast traps) are caused by defects located at the insulator/semiconductor interface and have, in contrast to the fixed charges, a strong field dependence (as discussed below). 2,36,92,126 Although developed for crystalline silicon, the model makes no appeal to any specific density of states distribution in the semiconductor, so that the approach is more general. These states are energetically located between valence and conduction band and can exchange charges with the semiconductor bulk as illustrated in Fig. 2.11(a) for a p-type sample. In this process, interface states interact with the valence band by emitting or capturing holes. The occupancy of the filled states may now be modulated through the applied small ac field by moving the valence band, i.e. Fermi level, up and down. A change of the DC bias, on the other hand, leads to a (different) band bending and enables therewith the probing of the interface traps at different energetic cites.

This trapping process has its characteristic relaxation time  $^{96}$   $\tau_{it} \propto \text{Exp}(V_s -$

<sup>&</sup>lt;sup>4</sup>The literature about inorganic MOS devices <sup>116</sup> discriminates for instance between oxide charges and ionic charges.

Figure 2.11: (a) Band bending of p-type semiconductor in depletion with arbitrary distribution of interface states  $N_{ss}$  at the semiconductor/insulator interface. (b) Equivalent circuit of a single interface trap level with relaxation time  $\tau_{it} = R_{it}C_{it}$  (I) and its equivalent representation by a frequency dependent capacitance  $C_p$  and conductance  $G_p$  (II).

$V_{\rm B}$ ),<sup>5</sup> which generally varies exponentially as function of the applied band banding  $V_s$ , i.e surface potential.<sup>92,116</sup> Due to  $\tau_{it}$  the interface charges may not respond immediately to the applied ac signal, leading eventually to a loss peak in the spectra and the loss-voltage characteristics as illustrated in Fig. 2.12. The interface states lead also to a stretch out of the C-V curves. This is due to the fact that extra charges have to fill the traps. Hence, it takes more charges, i.e. applied voltage to obtain the same surface potential as for the case without interface states.

Figure 2.12: Effect of fast interface traps on the C-V, i.e. loss-voltage, characteristics. Interface traps cause trenching of C-V, in comparison to the ideal characteristics.

Interface traps may also be modeled by means of equivalent circuits. Fig. 2.11(b)(I) shows a relatively simple representation of a single level interface state with a single time constant. In this case,  $\tau_{it} = R_{it}C_{it}$  is represented by a series branch of the majority carrier resistance  $R_{it}$  and interface state capacitance  $C_{it}$ . The insulator and depletion zone capacitance is given by  $C_i$  and

$<sup>^5</sup>V_{

m B}$  is the potential difference between the mid-gap and fermi level in the quasi neutral region of the semiconductor.

$C_d$ , respectively. The parallel branch can be then translated into a frequency dependent capacitance  $C_p$  and conductance  $G_p$  as given in Fig. 2.11(b)(II), with  $^{61,95}$

$$C_p = C_d + \frac{C_{it}}{1 + \omega^2 \tau_{it}^2}$$

(2.14)

$$\frac{G_p}{\omega} = \frac{C_{it}\omega\tau_{it}}{1 + \omega^2\tau_{it}^2}.$$

(2.15)

The height of the loss peak is governed by  $C_{it}$ , occurring at  $\omega \tau_{it} = 1$ . A relation between  $C_{it}$  and the interface trap density  $N_{ss}$  is obtained by using that  $dQ_{it} = qAN_{ss}dE$  and  $dE = qdV_s$ . Hence, it follows that

$$C_{it} \equiv \frac{\mathrm{d}Q_{it}}{\mathrm{d}V_s}$$

$$C_{it} = Aq^2 N_{ss}.$$

(2.16)

Equ. (2.16) and (2.14) may now be used to relate the loss peak maximum to  $N_{ss}$ , with

$$\left[\frac{G_p}{\omega}\right]_{max} = \frac{C_{it}}{2} = \frac{Aq^2N_{ss}}{2}.$$

(2.17)

The extraction of  $N_{ss}$  from  $[G_p/\omega]_{max}$  is usually referred to as Conductance Method, a technique developed by Nicollian and Goetzberger. <sup>96</sup> In order to extract  $G_p/\omega$  from the measured capacitance  $C_{\text{MIS}}$  and conductance  $G_{\text{MIS}}$  the insulator capacitance  $C_i$  has to be extracted. The admittance measured across the terminals x-x in Fig. 2.11(b)(II) is  $G_{\text{MIS}} + i\omega G_{\text{MIS}}$ . Converting this to an impedance, subtracting the reactance of  $C_i$ , and converting back to an admittance, finally yiels <sup>96</sup>

$$\frac{G_p}{\omega} = \frac{\omega C_i^2 G_{\text{MIS}} \left( G_{\text{MIS}}^2 + \omega^2 C_{\text{MIS}} \right)}{\omega^2 C_i^2 G_{\text{MIS}}^2 + \left[ \omega^2 C_{\text{MIS}} \left( C_i - C_{\text{MIS}} \right) - G_{\text{MIS}}^2 \right]}$$

(2.18)

$$C_p = \frac{C_i (G_{\text{MIS}}^2 + \omega^2 C_{\text{MIS}}^2) \left[ \omega^2 C_{\text{MIS}} (C_i - C_{\text{MIS}}) - G_{\text{MIS}}^2 \right]}{\omega^2 C_i^2 G_{\text{MIS}}^2 + \left[ \omega^2 C_{\text{MIS}} (C_i - C_{\text{MIS}}) - G_{\text{MIS}}^2 \right]}.$$

(2.19)

This correction only requires knowledge about the actual value of  $C_i$ , which can be inferred from the C-V characteristics of the MIS device at accumulation voltages.

Although the approach with Equ. (2.14) only considers a single trap level, it conveys the concept of interface traps and their modeling. A more realistic description of the loss phenomenon is obtained by the introduction of a continuum of trap levels, represented by a network of R-C branches, which will be discussed in section  $4.3.^6$

<sup>&</sup>lt;sup>6</sup>The correction in Equ. (2.18) remains still applicable for a continuum of interface traps.

#### 2.2.3 Calculation of Semiconductor Interface Potential

In section 4.3 fast interface traps are determined as function of the interface potential  $V_s$ . This quantity can not be measured directly but has to be inferred from the C-V characteristics. The surface potential  $V_s(V_g)$  as function of applied gate voltage  $V_g$  can be calculated from the low-frequency capacitance  $C_{lf} = \mathrm{d}Q_s/\mathrm{d}V_g$ . In this frequency regime the voltage drop across the insulator and semiconductor capacitance and its differential form is given by

$$V_g = V_s + \frac{Q_s}{C_i}$$

and  $dV_g = dV_s + \frac{dQ_s}{C_i}$ . (2.20)

With  $C_{lf} = dQ_s/dV_g$ , integration of the rearranged equation (2.20) yields

$$V_s(V_g) = \int_{V_{\text{FB}}}^{V_g} \left(1 - \frac{C_{lf}}{C_i}\right) dV_g + V_s(V_{\text{FB}}).$$

(2.21)

The integration constant  $V_s(V_{\rm FB})$  has to be chosen in such a way that the band bending in the flat-band condition is zero. It would also be possible to determine the additive constant in the case of strong accumulation as described in detail by Nicollian and Goetzberger. <sup>96</sup>

It shall be mentioned that Equ. (2.21) constitutes an approximation, only valid for insulators with sufficiently high resistivity that is to say with  $R_i \to \infty$ . The increase of leakage current in ultra thin organic insulator films <sup>48</sup>, however, may pose a problem for this kind of approximation. It is therefore worthwhile to consider the influence of a low  $R_i$ , in order to obtain a correct expression for  $V_s(V_g)$  on one side and to retrieve a lower limit of  $R_i$  for which Equ (2.21) is true on the other side. In order to account for the insulator and semiconductor resistance the circuit in Fig. 2.7, on page 14, has to be modified as depicted in Fig. 2.13. Here, semiconductor and insulator resistance, denoted as  $R_s$  and  $R_i$ , respectively, are connected in parallel to semiconductor and insulator capacitance. A more general approach is, then, given by replacing the real with complex capacities, that is to say  $C_i \to \tilde{C}_i$ ,  $C_s \to \tilde{C}_s$  and  $C_{lf} \to \tilde{C}_{lf}$ . In a similar fashion to above, the series branch of these complex capacities  $\tilde{C}_{lf}^{-1} = \tilde{C}_i^{-1} + \tilde{C}_s^{-1}$  yields

$$V_s(V_g) = \int_{V_{\text{FB}}}^{V_g} \text{Re}\left[1 - \frac{\tilde{C}_{lf}}{\tilde{C}_i}\right] dV_g + V_s(V_{\text{FB}}). \tag{2.22}$$

Here, it was used that only the real part  $\text{Re}[V_g/V_s] = \text{Re}[1 + C_s/C_i]$  needs to be considered for the calculation of  $V_s(V_g)$ .

Since each complex capacity can be expressed as parallel branch of capacitance and resistance, as shown in Fig. 2.13, the integrand of Equ. (2.22)

#### Insulator Semiconductor

Figure 2.13: Equivalent circuit representation of a MIS structure (refer to Fig. 2.7, on page 14) with  $R_i$  and  $R_s$  as insulator and semiconductor resistance, respectively.

can be rewritten as

$$\operatorname{Re}\left[1 - \frac{\tilde{C}_{lf}}{\tilde{C}_{i}}\right] = \operatorname{Re}\left[1 - \frac{C_{lf} + (i\omega R_{lf})^{-1}}{C_{i} + (i\omega R_{i})^{-1}}\right]$$

(2.23)

$$=1-\frac{\omega^{4}C_{i}C_{lf}\left(R_{lf}\right)^{2}R_{i}^{2}+\omega^{2}R_{i}R_{lf}}{\omega^{4}C_{i}^{2}\left(R_{lf}\right)^{2}R_{i}^{2}+\omega^{2}\left(R_{lf}\right)^{2}}.$$

(2.24)

With the weak assumption that the overall resistance of the MIS device  $R_{lf} = R_i + R_s$  will be largely governed by  $R_i$ , i.e.  $R_i \approx R_{lf}$ , we arrive at

$$\operatorname{Re}\left[1 - \frac{\tilde{C}_{lf}}{\tilde{C}_{i}}\right] = 1 - \frac{\omega^{2} C_{i} C_{lf} + R_{i}^{-2}}{\omega^{2} C_{i}^{2} + R_{i}^{-2}}.$$

(2.25)

From this estimate it is possible to infer the lower limit for the insulator resistance. Hence, as long as  $\omega^2 C_i C_{lf} > R_i^{-2}$ , Equ. (2.21) yields a good approximation of the surface potential, since the capacity  $C_i$  is not shunted by the insulator resistance  $R_i$ .

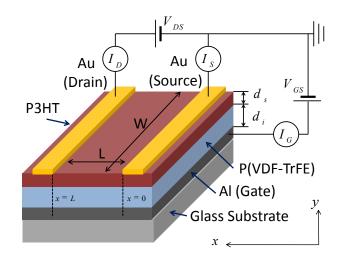

#### 2.2.4 Field-Effect-Transistor Equation

Fig. 2.14 shows a schematic illustration of a bottom gate FET as it was used for the measurements in section 4.4. When the forward bias is increased between source and gate charges become injected through the source and accumulate at the insulator/semiconductor interface (refer to section 2.2.1). This leads to formation of a conductive sheet near the interface, i.e. a channel, defined by channel width W and length L. Is a voltage applied between source and drain, this accumulation may then be monitored by means of the drain current  $I_D$ . This conduction process is described by hopping between neighboring localized states and is based on a Poole-Frenkel<sup>5,6,32,41,99</sup> effect.

An analytical expression for the drain current  $I_D$  can be found by using the differential expression for the field between source and drain, dV(x)/dx

Figure 2.14: OFET layer structure with channel length ( $L=100~\mu\mathrm{m}$ ), channel width ( $W=14.85~\mathrm{cm}$ ) as well as the insulator and semiconductor thickness  $d_i=0.3~\mu\mathrm{m}$  and  $d_s=0.06~\mu\mathrm{m}$ , respectively. Measurement circuitry and the contact making is schematically depicted. The source contact is grounded.

with x = 0 at the source and x = L at the drain contact. Thus the current density  $j_{DS}$  between source and drain may be written as

$$j_{\rm DS} = N_a(x)e\mu \frac{\mathrm{d}V(x)}{\mathrm{d}x} = \sigma \frac{\mathrm{d}V(x)}{\mathrm{d}x}$$

(2.26)

with  $N_a(x)$ , q,  $\mu$  and  $\sigma$  as number density, elementary charge, drift mobility and conductivity respectively. For simplicity,  $N_a$  shall only depend on x and  $\mu$  shall be considered as constant. <sup>118</sup> The charge at the interface can be expressed by

$$Q_s(x) = C_i [V_{GS} - V_t - V(x)] = N_a(x) qW L d_s$$

(2.27)

where  $C_i$ ,  $V_{\rm GS}$  and  $V_t$  are the capacitance of the insulator, the voltage applied between gate and source as well as the threshold voltage (refer to section 2.2.2), respectively. Equ. (2.26) and (2.27) then yields the expression for the drain current  $I_{\rm DS} = j_{\rm DS}Wd_s$ ,

$$I_{\rm DS} = WC_i'\mu \left[V_{\rm GS} - V_t - V(x)\right] \frac{\mathrm{d}V(x)}{\mathrm{d}x} \quad \text{with} \quad C_i' = \frac{C_i}{WL}. \tag{2.28}$$

Separation of variables and integration from drain to source leads to

$$I_{\rm DS} dx = W C'_{i} \mu [V_{\rm GS} - V_{t} - V(x)] dV$$

$$I_{\rm DS} \int_{L}^{0} dx = \int_{0}^{V_{\rm DS}} W C'_{i} \mu [V_{\rm GS} - V_{t} - V(x)] dV \qquad (2.29)$$

$$I_{\rm DS} = -\frac{W C'_{i} \mu}{L} \left[ (V_{\rm GS} - V_{t}) V_{\rm DS} - \frac{V_{\rm DS}^{2}}{2} \right].$$

For the integration of the left hand side of the equation, Kirchhoff's law of charge conservation was used. The change of upper and lower limit of this integral reflects the current direction, which can be defined as positive or negative. The saturation regime is reached when the effective potential between

drain and gate becomes zero, i.e.  $V_{\rm DS} = V_{\rm GS} - V_t$ . In this voltage regime the injection of holes into the semiconductor is suppressed, leading to a flattening of the drain current. Hence, with the condition  $V_{\rm DS} = V_{\rm GS} - V_t$ , Equ. (2.29) simplifies to

$$I_{\rm DS}^{s} = -\frac{WC_{i}'\mu}{2L} \left(V_{\rm GS} - V_{t}\right)^{2} \tag{2.30}$$

and can be conveniently used to calculate the mobility and the threshold voltage.

A reliable FET measurement requires a good insulating layer to ensure that  $I_{\rm DS} >> I_{\rm GS}$ , otherwise evaluation of the drain current becomes difficult. Under this condition,  $I_{\rm DS}$  is independent from the gate current  $I_{\rm GS}$  and may be measured as function of gate  $V_{\rm GS}$  or drain voltage  $V_{\rm DS}$  giving the transfer  $I_{\rm D}(V_{\rm GS})$  or output  $I_{\rm D}(V_{\rm DS})$  characteristic of a FeFET, respectively. <sup>118,133</sup>

# 3 Preparation and Sample Characterization

# 3.1 Device Preparation

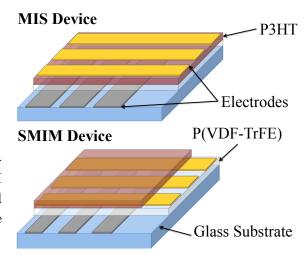

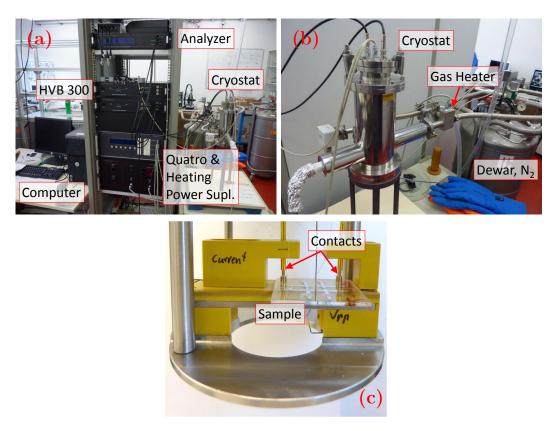

The sections below provide detailed information concerning the preparation of the Metal-Insulator-Metal (MIM), Metal-insulator-Semiconductor, Semiconductor-Metal-Insulator-Metal (SMIM) devices as well as Field-Effect-Transistors.

# 3.1.1 Preparation of P(VDF-TrFE) and P3HT Solution

For the preparation of the poly(vinylidenefluoride-trifluoroethylene) (P(VDF-TrFE)) solution two solvents were used: Acetone with a purity of  $\geq 99.7\%$  as well as 2-Butanone (MEK) with a purity of  $\geq 99.5\%$  and a acetic acid content of  $\leq 0.003\%$ . The latter solvent was more suitable for thin film preparations below 1  $\mu$ m, since P(VDF-TrFE)/2-butanone solution always produced smooth and transparent films. Further details about the P(VDF-TrFE) film preparation are given in section 3.1.2. The P3HT solutions were prepared with chloroform (purity 99%, stabilized with 1% ethanol.

All solutions were prepared in cleaned glass vials with teflon lids. It turned out that 2-butanone and chloroform can corrode the plastic of syringes and lids, which lead to pollution of the solution and consequently to speckles on the spincoated films. Therefore, it was necessary to use clean glass intead of plastic syringes in order to produce defect free, thin films. Syringes used for the preparation of poly(3-hexylthiophene) (P3HT) and P(VDF-TrFE) solution were always cleaned separately and never interchanged to avoid contaminations.

P3HT was purchased from American Dye Source, Inc. (ADS) with the following specifications:

- Molecular Weight (GPC): 60 000 g/mol (Polystyrene Standard)

- Polydispersity  $(M_w/M_n)$ : 1.7

- UV-VIS  $(\lambda_{max})$  Absorption: 446 nm

- Photoluminescence ( $\lambda_{max}$  Emission): 446 nm

- Metal content (Atomic Absorption analysis): Ni < 1 ppm

To promote the dissolution of the P3HT flakes the P3HT/chloroform solution was placed into an ultrasonic bath for about 1h. After that the solution was filtered twice, for precipitating possible unsolved particles. For the preparation of the organic electronic devices only one concentration of P3HT/solution was used (see Table 3.1)

The used copolymer, P(VDF-TrFE) (65/35 mol %), purchased from Solvey (Batch: 2P001), had the following specifications:

- Molecular Weight:  $M_W = 1.97 \times 10^5$  g/mol (Polystyrene Standard)

- Melting Temperature:  $T_M = 154, 4$  °C

- Curie Temp.:  $T_C = 106 \, ^{\circ}\text{C}$

In order to completely dissolve the P(VDF-TrFE) powder the solution was stirred at a temperature of 70°C for about 20 minutes. After the P(VDF-TrFE) was dissolved the preparation was finished with the filtering of the solution. Depending on the desired film thickness, different P(VDF-TrFE)/solvent concentrations were prepared ranging from 15 mg/ml up to 100 mg/ml. In Table 3.1 details can be found about the concentration and spin coating parameter for the respective layer thickness.

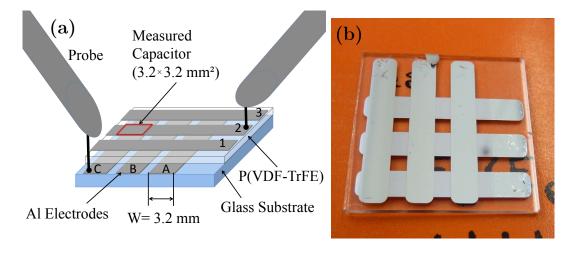

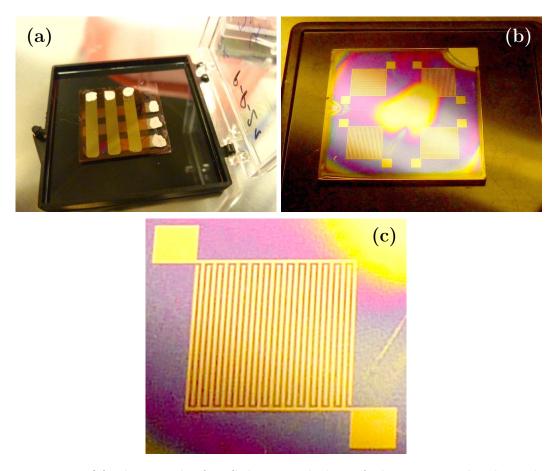

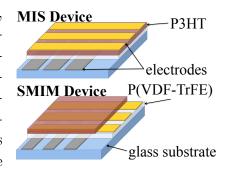

# 3.1.2 Preparation of Metal-Insulator-Metal (MIM) devices

The P(VDF-TrFE) capacitors (MIM devices), shown in Fig. 3.1(a) and (b) were prepared in an  $3\times3$ -array pattern (labeled as: 1A, 2A,...,1B,...1C,...). P(VDF-TrFE) capacitors as well as MIS and semiconductor-metal-insulator-metall (SMIM) devices, described below, were prepared onto cleaned glass substrates of size 1 mm  $\times$  24 mm  $\times$  24 mm. For cleaning the glass substrates were

- 1. manually rubbed with Deconex soap solution and subsequently rinsed with stain free water to remove all soap residuals,

- 2. placed into a soaking container filled with aceton and subjected to an ultrasonic bath for approximately 10 minutes (this step was afterwards repeated with isopropanol) and finally <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>If substrates needed to be stored for several days it turned out to be practicable to leave the samples in the isopropanol bath.

| Final Film          | Solute/Solvent                          | Spincoating                  |  |

|---------------------|-----------------------------------------|------------------------------|--|

| Thickness[ $\mu$ m] | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Parameter                    |  |

| 5                   | P(VDF-TrFE) / Acetone                   | 1st 400  rpm  (10  sec),     |  |

| 9                   | 100  mg/ml                              | $2nd\ 200\ rpm\ (20\ sec)$   |  |

|                     | P(VDF-TrFE) / Acetone                   | $1st\ 1000\ rpm\ (10\ sec),$ |  |

| 3.5                 | , ,                                     | $2st\ 600\ rpm\ (20\ sec),$  |  |

|                     | 100  mg/ml                              | 3rd 500  rpm  (20  sec)      |  |

| 1                   | P(VDF-TrFE) / 2-Butanon                 | 2000 rpm (10 sec)            |  |

| 1                   | 60  mg/ml                               |                              |  |

| 0.5                 | P(VDF-TrFE) / 2-Butanon                 | 1500 rpm (10 sec)            |  |

| (2 Layers)          | 30  mg/ml                               |                              |  |

| 0.25                | P(VDF-TrFE) / 2-Butanon                 | 1500 rpm (10 sec)            |  |

| 0.20                | 30  mg/ml                               |                              |  |

| 0.25                | P(VDF-TrFE) / 2-Butanon                 | inon 1900 rpm (10 gas)       |  |

| (2 Layers)          | 25  mg/ml                               | 1800 rpm (10 sec)            |  |

| 0.1                 | P(VDF-TrFE) / 2-Butanon                 | 1000 rpm (10 sec)            |  |

| (2 Layers)          | 15  mg/ml                               |                              |  |

| 0.05                | P3HT / Chloroform                       | 1500 rpm (10 sec)            |  |

| 0.00                | 10  mg/ml                               |                              |  |

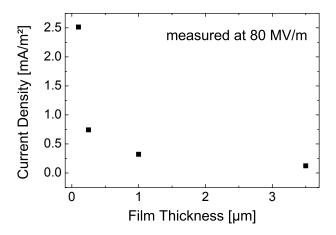

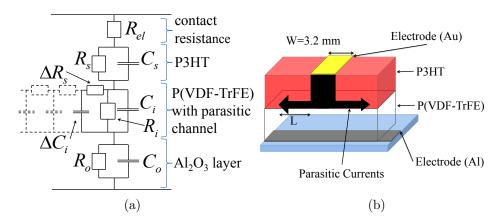

Table 3.1: Parameters as used for the preparation of the P(VDF-TrFE) layer.