# Scalable Compatibility for Embedded Real-Time components via Language Progressive Timed Automata

Stefan Neumann, Holger Giese

Technische Berichte Nr. 65

des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam | 65

Stefan Neumann | Holger Giese

Scalable Compatibility for Embedded Real-Time Components via Language Progressive Timed Automata

### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.de/ abrufbar.

# **Universitätsverlag Potsdam 2013**

http://verlag.ub.uni-potsdam.de/

Am Neuen Palais 10, 14469 Potsdam Tel.: +49 (0)331 977 2533 / Fax: 2292 E-Mail: verlag@uni-potsdam.de

Die Schriftenreihe **Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam** wird herausgegeben von den Professoren des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam.

ISSN (print) 1613-5652 ISSN (online) 2191-1665

Das Manuskript ist urheberrechtlich geschützt.

Online veröffentlicht auf dem Publikationsserver der Universität Potsdam URL http://pub.ub.uni-potsdam.de/volltexte/2013/6385/URN urn:nbn:de:kobv:517-opus-63853 http://nbn-resolving.de/urn:nbn:de:kobv:517-opus-63853

Zugleich gedruckt erschienen im Universitätsverlag Potsdam: ISBN 978-3-86956-226-1

#### **Abstract**

The proper composition of independently developed components of an embedded realtime system is complicated due to the fact that besides the functional behavior also the non-functional properties and in particular the timing have to be compatible. Nowadays related compatibility problems have to be addressed in a cumbersome integration and configuration phase at the end of the development process, that in the worst case may fail. Therefore, a number of formal approaches have been developed, which try to guide the upfront decomposition of the embedded real-time system into components such that integration problems related to timing properties can be excluded and that suitable configurations can be found. However, the proposed solutions require a number of strong assumptions that can be hardly fulfilled or the required analysis does not scale well. In this paper an approach based on timed automata is represented that can provide the required guarantees for the later integration without strong assumptions, which are difficult to match in practice. The approach provides a modular reasoning scheme that permits to establish the required guarantees for the integration employing only local checks and therefore scales. It is also possible to determine potential configuration settings by means of timed game synthesis.

# Contents

| 1                                                  | Introduction                           |                                                                                             |                    |  |  |  |  |

|----------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

|                                                    | 1.1                                    | State of the Art                                                                            | 1                  |  |  |  |  |

|                                                    | 1.2                                    | Contribution                                                                                | 3                  |  |  |  |  |

| 2                                                  | 2 Prerequisites                        |                                                                                             |                    |  |  |  |  |

|                                                    | 2.1                                    | Timed Automata                                                                              | 4                  |  |  |  |  |

|                                                    | 2.2                                    | Timed I/O Automata                                                                          | 9                  |  |  |  |  |

| 3                                                  | 3 Application Example - Engine Control |                                                                                             |                    |  |  |  |  |

|                                                    | 3.1                                    | Component Engine-Model                                                                      | 11                 |  |  |  |  |

|                                                    | 3.2                                    | Component Fuel-Sensor                                                                       | 12                 |  |  |  |  |

|                                                    | 3.3                                    | Component Fuel-Controller                                                                   | 14                 |  |  |  |  |

| 4                                                  | Pro                                    | gressive and Receptive TIOA                                                                 | 17                 |  |  |  |  |

| 5 Language Progressive and Language Receptive TIOA |                                        |                                                                                             |                    |  |  |  |  |

|                                                    | 5.1                                    | Checking Language-Progressive TIOA                                                          | 23                 |  |  |  |  |

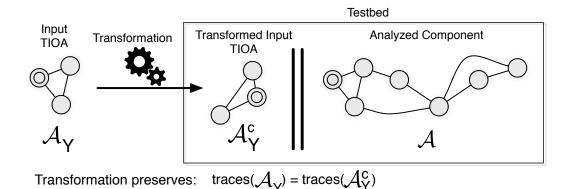

|                                                    | 5.2                                    | Creating a Testbed                                                                          | 26                 |  |  |  |  |

|                                                    |                                        |                                                                                             |                    |  |  |  |  |

|                                                    | 5.3                                    | Checking Language Receptive TIOA                                                            | 33                 |  |  |  |  |

| 6                                                  |                                        | Checking Language Receptive TIOA                                                            | 33<br><b>35</b>    |  |  |  |  |

| 6                                                  |                                        |                                                                                             |                    |  |  |  |  |

| 6                                                  | Cor                                    | npositional Reasoning - Supporting Single I/O Ports                                         | 35                 |  |  |  |  |

| 6                                                  | <b>Cor</b> 6.1                         | npositional Reasoning - Supporting Single I/O Ports  Well-Formedness - Language Progressive | <b>35</b><br>36    |  |  |  |  |

| 6<br>7                                             | <b>Cor</b> 6.1 6.2 6.3                 | mpositional Reasoning - Supporting Single I/O Ports  Well-Formedness - Language Progressive | <b>35</b> 36 38    |  |  |  |  |

|                                                    | <b>Cor</b> 6.1 6.2 6.3                 | mpositional Reasoning - Supporting Single I/O Ports  Well-Formedness - Language Progressive | <b>35</b> 36 38 40 |  |  |  |  |

# S. Neumann and H. Giese

| 8  | Checking Well-Formedness on Example |                                                              |    |  |  |  |

|----|-------------------------------------|--------------------------------------------------------------|----|--|--|--|

|    | 8.1                                 | Checking Language Progressive Behavior - Application Example | 49 |  |  |  |

|    | 8.2                                 | Checking Language Receptive Behavior - Application Example   | 51 |  |  |  |

|    | 8.3                                 | Evaluation Results - Complexity                              | 51 |  |  |  |

| 9  | Abs                                 | traction                                                     | 54 |  |  |  |

|    | 9.1                                 | Automatic Abstraction for IP Protection                      | 54 |  |  |  |

| 10 | Con                                 | clusion and Future Work                                      | 55 |  |  |  |

| Re | References                          |                                                              |    |  |  |  |

| A  | Proc                                | ofs                                                          | 58 |  |  |  |

| В  | Deta                                | niled TIOA models                                            | 63 |  |  |  |

| С  | Deta                                | niled Models of Testbeds                                     | 64 |  |  |  |

| D  | Com                                 | abined Ports                                                 | 65 |  |  |  |

| Ε  | Dea                                 | dlock Semantics and Checks                                   | 65 |  |  |  |

### 1 Introduction

The proper composition of independently developed components of an embedded real-time system is complicated due to the fact that besides the functional behavior also the non-functional properties and in particular the timing have to be compatible. Nowadays related compatibility problems have to be addressed in a cumbersome integration and configuration phase that in the worst case may fail. Therefore, real-time models are employed to find and check upfront a proper decomposition into components and related interfaces such that as much as possible problems during the integration can be excluded (cf. [12]).

In particular formal approaches have been developed, which try to support the upfront planning and checking of the embedded real-time systems such that integration problems at the non-functional level can be excluded. Any upfront planning and checking of the decomposition of an embedded real-time system has to be compatible with a number of requirements to be applicable in practice: (R1) As the architectures for embedded real-time systems can be rather large and include a huge number of components, the modeling and checking must be scalable. (R2) To be further appropriate for embedded real-time systems, it must be possible taking into account that the resources, which can be employed to realize the components, are limited due to economical reasons. (R3) Moreover, a network of OEMs and suppliers often develops embedded real-time systems, as in the case of automotive systems. Therefore, the modeling and checking must be possible without disclosing intellectual properties (IPs)¹ that should remain hidden, e.g., in the case they are related to implementation details. (R4) A reasoning scheme has to be expressive enough such that complex architectures containing cyclic communication dependencies and mode-dependent component interactions are supported.

#### 1.1 State of the Art

Different approaches exist that are able to fulfill individual requirements related to (R1), (R2), (R3) or (R4). According to [2, 1] component-based approaches can be distinguish between input-universal resp. *pessimistic* approaches that allow the environment to behave arbitrarily, and input-existential interpretations resp. *optimistic* approaches that only require an environment to exist that behaves sufficiently helpful. Optimistic frameworks as described in [3] use timed automata as timed interfaces and check whether an environment exists that behaves helpful. They do only protect intellectual properties (R3) to a limited extent as the interface behavior reveals many implementation details. Furthermore, the required checks do not scale for larger architectures (R1) because all interfaces are analyzed at once or in form of combined interfaces. Any analysis needs to be applied using the combined interface and as a consequence during the analysis all relevant information of the overall architecture need to be provided, rarely allowing protecting IPs (R3). In contrast, pessimistic frameworks as in [16, 10] use conditions on the timed input/output automata (TIOA) such as progressive or input enabled behavior for ensuring that components can be safely used in an environment

<sup>&</sup>lt;sup>1</sup>Properties related to details that have an economical value.

that behaves arbitrarily.<sup>2</sup> A progressive or input enabled timed automaton is able to receive each and every input signal at any state. The conditions are further compositional such that the composition of two progressive, deadlock and zeno free TIOA is safe by resulting in a progressive, deadlock and zeno free TIOA. Due to its compositional nature, the approaches scale well (R1) and as the conditions are rather generic the IP is also well protected (R3). However, these generic conditions result in high resource requirements. For being able to fulfill the required property of progressive or input enabled behavior, such a component must be able to receive an arbitrary number of signals (e.g., 1, 1000, 1 million or even more) in any time period greater than 0. As a consequence nearly unlimited resources need to be assumed for processing received signals. Thus, requirement (R2) is difficult or even impossible to match in practice when requiring progressive behavior.

Another related direction is the timed interface approach for data-flow based architectures as proposed in [22], which focuses only on the load that the components can handle. In its basic form, these approaches scale (R1) and can take resource restrictions into account (R2), but require acyclic architectures and do not support mode-dependent behavior (R4).<sup>3</sup> Behavior, where different modes can become active during runtime, realizing a different timing behavior, are not directly supported.<sup>4</sup> Dependencies between the data-flow as well as system characteristics as in case of the used scheduling exist, resulting in limitations for the structure of the component-based architecture. As a result, requirement (R4) is not fully supported. Existing extensions permit to cover cycles to some extend [15] as well as components described by timed automata [17], but mode-dependent component interaction at the interface is still not covered. Furthermore, the load characteristics are sufficiently abstract such that the IP remains hidden (R3).

Behavior, Interaction, Priority (BIP) [6] is a framework for the component-based construction of real-time embedded system. BIP provides mechanisms for supporting a correctness-by-construction approach and creating hierarchical architectures composed of atomic components as well as tooling for analyzing the reachable state space using explorative techniques. Concerning (R1) holds that the original BIP approach does not scale, but in [20] it is shown how to apply an analysis in a modular fashion. For being able to apply a modular analysis, deterministic behavior is required and as a result only restricted types of timed automata can be used for verification purposes. While protecting IP is not addressed (R3), BIP is expressive enough to partially cover practical cases to some extend (R4), because hierarchical architectures and cyclic ones are supported.

Another approach supporting the modular verification of timed automata that scales (R1) can be found in [11]. Like in the case of [13] (extension of BIP) only deterministic behavior is allowed. We believe that allowing only deterministic TA is much too restrictive, due to the fact that nondeterminism often is related to parameters that can be configured during and not before composition (like in the case of execution orders of constituent parts of a component that need to fit to the order of incoming signals). Further, how to support cyclic architectures (R4) using deterministic frameworks in an analysis that scales is still an open issue. How to maintain protecting IPs (R3) is not considered in [11] and [13].

<sup>&</sup>lt;sup>2</sup>Only deadlocks and zeno behavior needs to be excluded for the environment.

<sup>&</sup>lt;sup>3</sup>Minimal and maximal arrival times are fix.

<sup>&</sup>lt;sup>4</sup>Such a mode dependent behavior can also be found in the used application example described in Sec. 3.

#### 1.2 Contribution

In this paper, an approach is represented based on timed automata that can provide the required guarantees (R1), (R2), (R3) and (R4) for the later integration, which does not require strong assumptions difficult to match in practice as in the case of progressive, deterministic or input enabled behavior. It can be seen as a compromise between the too pessimistic approaches that avoid any reliance on the characteristics of the environment, leading to arbitrary high resource requirements (R2), and the too optimistic approaches that rely too much on helpful environment characteristics, which do not scale (R1). The introduced reasoning scheme is expressive enough such that complex architectures containing cyclic communication dependencies and mode-dependent component interactions are supported (R4).

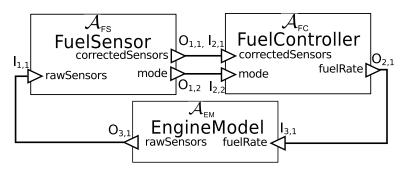

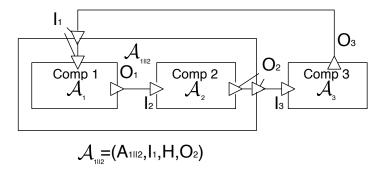

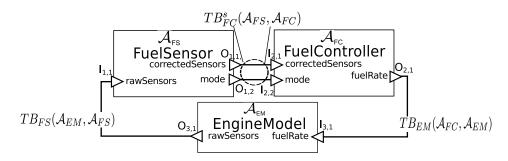

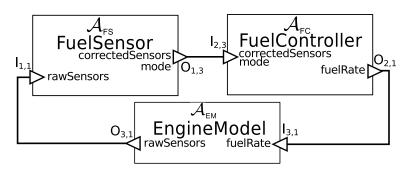

As an example, Figure 1 shows the composition of the three components *FuelSensor*, *FuelController* and *Engine-Model* realizing the fuel rate control of a combustion engine. This architecture contains cyclic communication dependencies. *FuelSensor* is responsible for the evaluation of sensor values from the engine. *FuelController* is responsible for calculating the desired fuel rate for the engine. The component *EngineModel* represents relevant behavior of the engine. In Sec. 3 this application example is discussed in more detail. For such an engine control system holds that in the domain of automotive systems only limited resource are available (R2). IPs (R3) related to implementation details of individual components often have to be protected in the case of a distributed development process. In the remainder of this work the framework of language progressive TIOA is introduced. Furthermore, it is shown how to address non-functional properties in case of the timing, for an architecture as depicted in Figure 1, such that requirements (R1), (R2), (R3) and (R4) are fulfilled.

Figure 1: Fuel-Rate-Control architecture for the control of a combustion engine.

The paper is organized as follows: In Section 2, preliminary definitions like in the case of timed (IO) automata are introduced. In Section 3 the application example of the fuel rate control, like depicted in Fig. 1, is described in more detail. We show in Sec. 4 that the existing approach of progressive and receptive behavior (cf. [16]) does not fulfill requirement (R2). In Section 5 a formal definition of language progressive and language receptive TIOA is given, in contrast to the approach described in [16], fulfilling requirement (R2). Further it is discussed how to automatically check whether the property of language progressive be-

<sup>&</sup>lt;sup>5</sup>The example is derived from an existing demo application shipped with the tool SystemDesk, a professional tool for designing component based architectures for real-time embedded systems (see http://www.dspace.com/systemdesk).

havior is fulfilled. Based on the defined property of language progressive timed automata, we present a reasoning scheme in Section 6. Well-formedness criteria are used building a framework for the component-based development of real-time embedded and resource restricted (R2) systems consisting of components with a single input and a single output port. How to overcome the limitation to be restricted to components with a single input/output port is shown in Sec. 7. A compositional reasoning scheme is described supporting the construction of components with multiple input/output ports and architectures containing cyclic communication dependencies (R4). In Sec. 8 the defined reasoning scheme is applied on the application example. It is shown that the created reasoning scheme scales and as a consequence fulfills requirement (R1). In Sec. 9 it is briefly discussed how existing abstraction techniques for timed automata fit into the developed approach, supporting requirement (R3). We close the paper with conclusions and an outlook on future work.

# 2 Prerequisites

Following the formal model of Alur-Dill style timed automata (TA, cf. [4]) is introduced. Further, the formal model of timed input/output automata (TIOA, cf. [16]) is introduced, which is the basis for the subsequently introduced class of TA.

#### 2.1 Timed Automata

In the following, the formal model of timed automata (TA) is recalled. TA are considered that distinguish explicitly between variables in form of so-called *clocks*, respectively attributes and in form of *locations*. In the following, let  $\mathbb R$  denote the set of reals,  $\mathbb R^+$  denote the set of non-negative reals and  $\mathbb N^+$  denote the set of non-negative natural numbers.

#### **Definition 1 (Attributed Timed Automaton)**

An attributed timed automaton (TA) is a tuple  $A=(\Sigma,\mathcal{L},\mathcal{L}^0,X,V,\mathcal{I},E)$  consisting of a finite set of signals  $\Sigma$ , which includes the empty signal  $\sigma_{\epsilon}\in\Sigma$ , a finite set of locations  $\mathcal{L}$ , a finite set of initial locations  $\mathcal{L}^0\subseteq\mathcal{L}$ , a finite set of clock variables  $X=\{x_1,\ldots,x_n\}$ , a finite set of attribute variables  $V=\{v_1,\ldots,v_m\}$ , a function  $\mathcal{I}:\mathcal{L}\to 2^{\mathcal{C}(X)}$  assigning to each location a set of clock invariants  $\mathcal{I}(l)\subseteq\mathcal{C}(X)$  and a set of edges  $E\subseteq\mathcal{L}\times\Sigma\times 2^{\mathcal{C}(X)}\times 2^{\mathcal{C}(V)}\times 2^X\times 2^V\times \mathcal{L}$ .  $\mathcal{C}(X)$  is the set of (clock) conditions over X and consists of all equations of the form  $x\sim c$  where  $v\in\{0,1]$  and  $v\in\mathbb{N}^+$  is a constant.  $v\in\mathbb{N}^+$  is the set of (attribute variable) conditions over  $v\in\mathbb{N}^+$  or  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  are  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  are  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  are  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  are  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  are  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  are  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  and  $v\in\mathbb{N}^+$  are  $v\in\mathbb{N}^+$  and  $v\in\mathbb$

An edge  $e \in E$  from location l to l' is defined by a tuple  $e = (l, a, \varphi, \lambda, l')$ , where  $a \in \Sigma$  is a signal,  $\varphi \subseteq \mathcal{C}(X) \cup \mathcal{C}(V)$  is a guard that must be enabled to fire the edge, and  $\lambda \subseteq 2^X \cup 2^V$ .  $2^X$  is a set of clock variables that are reset to the value 0 if the edge is taken.  $2^V$  is a set of all assignments of the form  $v \simeq n$  with  $v \in V$  and  $v \in \{+, -, :=\}$  and  $v \in V$  or  $v \in \mathbb{R}$ .

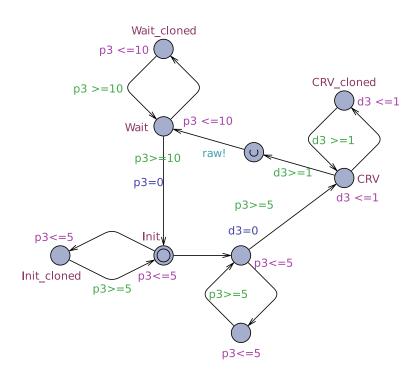

An example of a TA is shown in Fig. 3 on page 12. *Init* is an initial location with invariant  $p3 \le 4$  over clock variable p3. This invariant allows the TA to stay in the initial location for at most 4 time units. The edge from location *Init* to location *CRV* contains the clock reset d3 = 0 of the clock d3. The edge from location *CRC* to location *wait* contains the signal *raw*, which need to be synchronized when taking the edge. Further, the edge contains the guard  $d3 \ge 0$ , allowing taking the edge only if the clock d3 has a value greater or equal to 0.6 Following different types of locations are defined in case of *urgent* and *committed* locations. An urgent location of a TA is a location where time is not allowed to pass. A committed location is a location where time is not allowed to pass and, when being in a committed location, the next edge needs to be taken is an edge starting from a committed location.

#### **Definition 2 (Extended Timed Automaton)**

An extended timed automaton (TA), including urgent and committed locations is a TA  $A = (\Sigma, \mathcal{L}, \mathcal{UL}, \mathcal{CL}, \mathcal{L}^0, X, V, \mathcal{I}, E)$  according to Def. 1 with  $\mathcal{L}$  being divided into a set  $\mathcal{UL}$  of urgent locations and a set  $\mathcal{CL}$  of committed locations with  $\mathcal{UL} \cup \mathcal{CL} = \mathcal{L}$ . For an extended TA holds  $\mathcal{UL} \cap \mathcal{CL} = \emptyset$  and  $\{\mathcal{UL} \cup \mathcal{CL} \cup \mathcal{L}^0\} \subseteq \mathcal{L}$ .

Remark, an extended TA with  $\mathcal{UL} = \mathcal{CL} = \emptyset$  is equivalent to an attributed TA. Following the semantics of the composition of attributed as well as extended TA is defined.

## **Definition 3 (Parallel composition of TA)**

Let  $A_1 = (\Sigma_1, \mathcal{L}_1, \mathcal{L}_1^0, X_1, V_1, \mathcal{I}_1, E_1)$  and  $A_2 = (\Sigma_2, \mathcal{L}_2, \mathcal{L}_2^0, X_2, V_2, \mathcal{I}_2, E_2)$  be two timed automata. Their parallel composition  $A_1 \parallel A_2$  is defined as the timed automaton

$$A = (\Sigma_1 \cup \Sigma_2, \mathcal{L}_1 \times \mathcal{L}_2, \mathcal{L}_1^0 \times \mathcal{L}_2^0, X_1 \cup X_2, V_1 \cup V_2, \mathcal{I}, E)$$

where  $\mathcal{I}(\langle l_1, l_2 \rangle) = \mathcal{I}_1(l_1) \cup \mathcal{I}_2(l_2)$  for all  $l_1 \in \mathcal{L}_1$ ,  $l_2 \in \mathcal{L}_2$ , and  $(\langle l_1, l_2 \rangle, a, \varphi, \lambda, \langle l_1', l_2' \rangle) \in E$  if one of the following conditions holds:

- 1.  $a \in \Sigma_1 \setminus \Sigma_2$ ,  $l_2 = l_2'$  and there exists  $(l_1, a, \varphi, \lambda, l_1') \in E_1$ ,

- 2.  $a \in \Sigma_2 \setminus \Sigma_1$ ,  $l_1 = l'_1$  and there exists  $(l_2, a, \varphi, \lambda, l'_2) \in E_2$ ,

- 3.  $a \neq \sigma_{\epsilon} \land a \in \Sigma_1 \cap \Sigma_2$ , and there exist  $(l_1, a, \varphi_1, \lambda_1, l_1') \in E_1$ ,  $(l_2, a, \varphi_2, \lambda_2, l_2') \in E_2$  with  $\varphi = \varphi_1 \cup \varphi_2$ ,  $\lambda = \lambda_1 \cup \lambda_2$ .

Accordingly the parallel product of two extended timed automata is defined as follows. The only difference is, that edges leaving committed locations prevent edges leaving non-committed locations.

#### **Definition 4 (Parallel composition of extended TA)**

Let  $A_1 = (\Sigma_1, \mathcal{L}_1, \mathcal{UL}_1, \mathcal{CL}_1, \mathcal{L}_1^0, X_1, V_1, \mathcal{I}_1, E_1)$  and  $A_2 = (\Sigma_2, \mathcal{L}_2, \mathcal{UL}_2, \mathcal{CL}_2, \mathcal{L}_2^0, X_2, V_2, \mathcal{I}_2, E_2)$  be two extended timed automata. Their parallel composition  $A_1 \parallel A_2$  is defined as the timed automaton

$$A = (\Sigma_1 \cup \Sigma_2, \mathcal{L}_1 \times \mathcal{L}_2, \mathcal{L}_1^0 \times \mathcal{L}_2^0, X_1 \cup X_2, V_1 \cup V_2, \mathcal{I}, E)$$

<sup>&</sup>lt;sup>6</sup>An exclamation mark is used in case of the send signal. Exclamation marks, resp. question marks allow to graphically distinguishing between send and received signals.

<sup>&</sup>lt;sup>7</sup>Committed locations become more relevant in the context of the parallel product of two timed automata, where each can or cannot be in a committed location.

where  $\mathcal{I}(\langle l_1, l_2 \rangle) = \mathcal{I}_1(l_1) \cup \mathcal{I}_2(l_2)$  for all  $l_1 \in \mathcal{L}_1$ ,  $l_2 \in \mathcal{L}_2$ , and  $(\langle l_1, l_2 \rangle, a, \varphi, \lambda, \langle l_1', l_2' \rangle) \in E$  if one of the following conditions holds:

- 1.  $a \in \Sigma_1 \setminus \Sigma_2$ ,  $l_2 = l_2'$  and there exists  $(l_1, a, \varphi, \lambda, l_1') \in E_1$  and  $l_1 \notin \mathcal{CL}_1, l_2 \notin \mathcal{CL}_2 \vee l_1 \in \mathcal{CL}_1$ ,

- 2.  $a \in \Sigma_2 \setminus \Sigma_1$ ,  $l_1 = l_1'$  and there exists  $(l_2, a, \varphi, \lambda, l_2') \in E_2$  and  $l_1 \notin \mathcal{CL}_1$ ,  $l_2 \notin \mathcal{CL}_2 \vee l_2 \in \mathcal{CL}_2$ ,

- 3.  $a \neq \sigma_{\epsilon} \land a \in \Sigma_1 \cap \Sigma_2$ , and there exist  $(l_1, a, \varphi_1, \lambda_1, l_1') \in E_1$ ,  $(l_2, a, \varphi_2, \lambda_2, l_2') \in E_2$  with  $\varphi = \varphi_1 \cup \varphi_2$ ,  $\lambda = \lambda_1 \cup \lambda_2$ .

Further holds each  $l_i \in \mathcal{L}_1 \times \mathcal{L}_2$  with  $l_i = \langle l_j, l_k \rangle$  and  $l_j \in L_1$ ,  $l_k \in L_2$  is an urgent location, if  $l_j$  or  $l_k$  is an urgent location and both are not committed locations. Further holds  $l_i$  is a committed location if  $l_j$  or  $l_k$  is a committed location (committed locations dominate urgent locations under composition).

The semantics of a (extended) timed automaton is defined in terms of an induced timed system.

#### **Definition 5 (Timed system)**

A timed system is a tuple  $\mathcal{T}=(\Sigma,\mathcal{S},\mathcal{S}^0,T)$  consisting of a set of signals  $\Sigma$  with  $\Sigma\cap\mathbb{R}^+=\emptyset$ , a set of states  $\mathcal{S}$ , a set of initial states  $\mathcal{S}^0\subseteq\mathcal{S}$  and a transition relation  $T\subseteq\mathcal{S}\times(\Sigma\cup\mathbb{R}^+)\times\mathcal{S}$ .

A (extended) timed automaton  $A=(\Sigma,\mathcal{L},\mathcal{UL},\mathcal{CL},\mathcal{L}^0,X,V,\mathcal{I},E)$  induces the timed system  $\mathcal{T}_A=(\Sigma,\mathcal{S},\mathcal{S}^0,T)$  in the following way. A function  $v:X\to\mathbb{R}^+$  is called a *clock valuation*. For a duration  $\tau\in\mathbb{R}^+$ ,  $v+\tau$  is the clock valuation v'' with  $v''(x)=v(x)+\tau$  for all  $x\in X$ . Now, the set of states  $\mathcal{S}$  of the induced timed system  $\mathcal{T}_A$  is given by all pairs  $s=\langle l,v\rangle$  where  $l\in\mathcal{L}$  and v is a clock valuation for X as well as an attribute assignment for V. The set of initial states  $\mathcal{S}^0$  consists of all pairs  $s^0=\langle l^0,v^0\rangle$  where  $l^0\in\mathcal{L}^0$  and  $v^0$  is the clock valuation that assigns  $v^0$  to all  $v^0$  to all variables of  $v^0$ . The induced timed system  $v^0$  contains two types of transitions:

- 1. *discrete transitions*  $s \xrightarrow{\sigma} s'$  where  $\sigma \in \Sigma$  is a signal,

- 2. time transitions  $s \xrightarrow{\tau} s'$  where  $\tau \in \mathbb{R}^+$  is a duration.

Discrete transitions change the location parameter of a state and are induced by the edges of the TA. A subset of the clocks may be reset to 0 when taking the transition, as specified by the edge. Further, when taking an edge a potentially empty set of variables included in V is updated.

A discrete transition can only be taken in state s if an edge  $e=(l,a,\varphi,\lambda,l')$  of the underlying TA is enabled. An edge e of a TA is called enabled in state s, if the TA in state s is in a location l where an outgoing edge e, including the signal  $\sigma=a$  (including the empty signal), can be taken. This is only the case if the guard  $\varphi$  can be evaluated to true in state s.

Not reset clocks and not updated attributes remain the same. Time transitions do not modify the location, but increase the values of all clocks synchronously, i.e.  $\langle l,v\rangle \stackrel{\tau}{\longrightarrow} \langle l,v+\tau\rangle$ . This is possible only as long as the invariant of location l is satisfied and if l is not an urgent or committed location. Since the induced timed system of a TA is usually infinite, in practice symbolic representations of the clock valuations, such as  $clock\ zones\ [14]$ , are used to obtain a finite semantics.

The induced timed system  $\mathcal{T}_{A_1\parallel A_2}$  of the parallel product  $A_1\parallel A_2$  of the two TA  $A_1=(\Sigma_1,\mathcal{L}_1,\mathcal{U}\mathcal{L}_1,\mathcal{C}\mathcal{L}_1,\mathcal{L}_1^0,X_1,V_1,\mathcal{I}_1,E_1)$  and  $A_2=(\Sigma_2,\mathcal{L}_2,\mathcal{U}\mathcal{L}_2,\mathcal{C}\mathcal{L}_2,\mathcal{L}_2^0,X_2,V_2,\mathcal{I}_2,E_2)$  accordingly contains states of the form  $s=\langle l,v\rangle$  with  $l=\langle l_1,l_2\rangle$  and  $l_1\in\mathcal{L}_1,l_2\in\mathcal{L}_2$  and v being an assignment of all clocks included in the set  $X_1\cup X_2$  as well as variables in  $V_1\cup V_2$ . Discrete transitions accordingly include signals  $\sigma\in\Sigma_1\cup\Sigma_2$ .

The timed system of a given TA A is denoted by  $\mathcal{T}_A = (\Sigma_A, \mathcal{S}_A, \mathcal{S}_A^0, T_A)$ .  $T_A(s_A)$  denotes the set of transitions starting in state  $s_A \in \mathcal{S}_A$  of the induced timed system of TA A.

The observable behavior of a timed automaton A is defined by the set of traces observable on  $\mathcal{T}_A$ . A trace  $\alpha$  is a finite or infinite alternating sequence of signals and durations  $\alpha = \tau_1\sigma_1\tau_2\sigma_2\tau_3\ldots$  with  $\sigma_i\in\Sigma$  and  $\tau_i\in\mathbb{R}^+$  specifying the order and the delays between consecutive signals.  $signals(\alpha)$  denotes the set of signals that occur in  $\alpha$ . Furthermore, let  $traces\_to(s_1,A)$  denote all traces starting in an initial state and ending in state  $s_1$  and  $traces\_from\_to(s_1,s_2,A)$  denotes the set of all observable traces of the TA A when starting in state  $s_1$  and ending in state  $s_2$ . Let  $traces\_from(s,A)$  denote the set of all observable traces of a timed automaton A starting in state s and let traces(A) denote the union of all traces observable from all initial states. If a set of traces is given explicitly, it is also referred as a language and usually denoted by the letter  $\Upsilon$ .  $signals(\Upsilon)$  denotes the set of signals included in at least one trace  $\alpha \in \Upsilon$ . Attributes of a TA are defined to be internal and are not shared with other TA in a parallel product. As a consequence attributes do not occur in any trace or language of a TA.

With  $time(\alpha)$  the sum over all time delays included in  $\alpha$  is denoted. For trace  $\alpha=1.13~a~2.27~b~0$  it holds that  $time(\alpha)=3.4$ .

#### **Definition 6 (Time Length)**

Let t be either a transition  $t=s \xrightarrow{\tau} s_1'$  observable on a state s of the induced timed system of a TIOA or let  $t=\tau_1\sigma_1\tau_2\sigma_2\dots\tau_n\sigma_n$  be a trace. The function time-length time(t) over t is defined as follows:

- In case t is a transition, time(t) = 0 if t is a discrete transition and  $time(t) = \tau$  if t is a continuous transition.

- In case t is a trace  $t = \tau_1 \sigma_1 \tau_2 \sigma_2 \dots \tau_n \sigma_n$  with  $\tau_i$  being a delay and  $\sigma_i$  being a signal for  $0 \le i \le n$ , time(t) is equal to a such that  $\sum_{i=1}^n \tau_i = a$ .

Further, the language of a TA is defined as follows.

#### **Definition 7 (TA Language)**

The language  $\Upsilon$  of a (extended) TA A is defined as the set of traces  $\Upsilon = traces(A)$ . traces(A) includes all traces that can be observed on the TA A starting from an initial state.

For being able to distinguish between different sets of signals included in a TA at the level of its language, the restriction of a language is following defined.

## **Definition 8 (Language Restriction)**

Let  $\alpha$  be a trace and  $\sigma$  be a signal. The trace  $\alpha \setminus \sigma$  is derived from  $\alpha$  by replacing all occurrences of  $\tau \sigma \tau'$  in  $\alpha$  by  $(\tau + \tau')$  for all  $\tau, \tau' \in \mathbb{R}^+$ . Let  $\Sigma$  be a set of signals and  $\Sigma_{\Upsilon} = \{\overline{\sigma_1}, \ldots, \overline{\sigma_n}\} = signals(\Upsilon) \setminus \Sigma$  all signals included in  $\Upsilon$  but not in  $\Sigma$ . The trace  $\alpha \upharpoonright \Sigma$  is defined as  $\alpha \upharpoonright \Sigma = \alpha \setminus \overline{\sigma_1} \setminus \ldots \setminus \overline{\sigma_n}$ . For a given language  $\Upsilon, \Upsilon \upharpoonright \Sigma$  is equal to  $\{\alpha \upharpoonright \Sigma \mid \alpha \in \Upsilon\}$ .

Thus, for a language  $\Upsilon$ , the language  $\Upsilon \upharpoonright \Sigma$  is derived by restricting the set of included signals to  $\Sigma$ , formally by removing all signals that do not occur in  $\Sigma$  in all traces of  $\Upsilon$ . Note that when removing the occurrence of a signal in a trace, the delays before and after this occurrence are summed up in the derived trace.

Moreover, a trace  $\alpha$  is called a *prefix* of a trace  $\beta$ , written as  $\alpha \vdash \beta$ , if  $\alpha = \beta$  or  $\alpha$  is a finite trace  $\alpha = \tau_1 \sigma_1 \dots \tau_n \sigma_n$  and  $\beta$  is of the form  $\beta = \tau_1 \sigma_1 \dots \tau_n \sigma_n \tau_{(n+1)} \sigma_{(n+1)} \dots$ , i.e.,  $\beta$  begins with  $\alpha$ . Further, in a state s of an induced timed system an observable transition t is part of the observable trace  $\alpha$  starting from this state.  $t \vdash \alpha$  denotes that t contributes the first step of the observable trace  $\alpha$  starting from state s. Also two traces  $t_1$  and  $t_2$  can be related by the operator  $\vdash$ . As an example consider  $t_1 = s_1 \xrightarrow{a} s_1'$  and  $t_2 = s_2 \xrightarrow{b} s_2'$ . If s is a signal,  $t_1 \vdash t_2$  is fulfilled if t is time delay greater than zero,  $t_1 \vdash t_2$  is fulfilled if t is time delay with t is time delay with t is time delay.

$\alpha = \beta \circ \gamma$  denotes the concatenation of two traces and  $\alpha = \beta \circ t \circ \gamma$  denotes the concatenation of a trace  $\beta$ , a transition t and a trace  $\gamma$ .

The restriction operator is also defined for a TA.

### **Definition 9 (TA Restriction)**

Let  $A=(\Sigma,\mathcal{L},\mathcal{L}^0,X,\mathcal{I},E)$  be a TA and let  $\Sigma_{rem}$  be a set of signals.  $A \upharpoonright \Sigma_{rem} = A_2 = (\Sigma_{rem},\mathcal{L},\mathcal{L}^0,X,\mathcal{I},E_2)$ . Let  $\Sigma_2 = \Sigma \setminus \Sigma_{rem}$  be the set of removed signals. For each edge  $e \in E$ , with  $e=(l,a,\varphi,\lambda,l')$ , holds,  $e \in E_2$  if  $a \notin \Sigma_2$ . If  $a \in \Sigma_2$  an edge  $e_{rem}=(l,\sigma_\epsilon,\varphi,\lambda,l')$  is included in  $E_2$  containing the empty signal  $\sigma_\epsilon$ . Further holds there not exists an edge e in  $E_2$  if one of the following conditions holds:

1)

$$e = (l, a, \varphi, \lambda, l')$$

and  $a \in \Sigma_2$  with  $e \in E$ , or,

2)

$$e = (l, \sigma_{\epsilon}, \varphi, \lambda, l') \land \neg \exists e_2 : e_2 \in E \text{ with } e_2 = (l, a_2, \varphi, \lambda, l') \land a_2 \in \Sigma_2 \text{ and } e \notin E.$$

Informally a TA restricted to a set of signals  $\Sigma_{rem}$  is a TA where signals are removed from edges of the TA that are not included in  $\Sigma_{rem}$  (edges are preserved but signals are added).

#### Lemma 2.1 (Restriction Relation)

Given a TA A with  $traces(A) = \Upsilon$ . For any set of signals  $\Sigma_{rem}$  holds:  $traces((A \upharpoonright \Sigma_{rem})) = \Upsilon \upharpoonright \Sigma_{rem}$ .

#### Proof 2.1

(sketch) Assuming  $traces((A \upharpoonright \Sigma_{rem})) \neq \Upsilon \upharpoonright \Sigma_{rem}$ . This can only be the case if 1) a trace  $\alpha$  is included in  $traces((A \upharpoonright \Sigma_{rem}))$  that is not included in  $\Upsilon \upharpoonright \Sigma_{rem}$ , or, 2) a trace  $\alpha$  is not included

in  $traces((A \upharpoonright \Sigma_{rem}))$  that is included in  $\Upsilon \upharpoonright \Sigma_{rem}$ . Assuming 1): This can only be the case if a trace  $\alpha$  is observable on the induced time system of  $A \upharpoonright \Sigma_{rem}$  for that holds:  $\neg \exists \beta \in \Upsilon$  such that  $\beta \upharpoonright \Sigma_{rem}$  being equal to  $\alpha$ . If this is the case, the restriction operator  $\upharpoonright \Sigma_{rem}$  applied on A has enabled a transition in the induced time system of  $A \upharpoonright \Sigma_{rem}$  by removing a signal. Because A is an isolated TA which do not need to synchronize with other TA at all, this cannot be the case. Assuming 2): This can only be the case if a signal  $\sigma$ , included in an edge of A is removed by applying the restriction operator  $\upharpoonright \Sigma_{rem}$  on A, such that for at least one trace  $\beta$ , which is observable on the induced time system of A, no trace  $\alpha$  is observable on the induced time system of A is reachable because a transition is enabled only if synchronization with  $\sigma$  appears. Because in our model such synchronization of an isolated TA can only disable but not enable transitions, this cannot be the case.

Informally Theorem 2.1 states that an equivalence relation between the observable traces of a TA and the language of the TA concerning the restriction operator exists. Thus, it doesn't matter if first the TA is restricted to a set of signals or if the set of observable traces, of the induced timed system, is restricted to the same set of signals. Both methods lead to the same set of signals.

#### 2.2 Timed I/O Automata

The definition of a timed I/O automaton (TIOA) is obtained by explicitly distinguishing between input, output and internal signals contained in a timed automaton.

#### **Definition 10 (Timed I/O automaton)**

A timed I/O automaton (TIOA) is a tuple  $\mathcal{A}=(A,I,O,H)$  where A is a (extended) timed automaton and the set of signals  $\Sigma$  of A is partitioned into the disjoint sets I,O and H, respectively called the input, output and internal signals of A. Further holds that the empty signal is an internal signal:  $\sigma_{\epsilon} \in H$ .

Intuitively, a component modeled by a TIOA receives input signals, sends output signals and performs internal state changes using internal signals or delay transitions.

# **Definition 11 (Parallel composition of TIOA)**

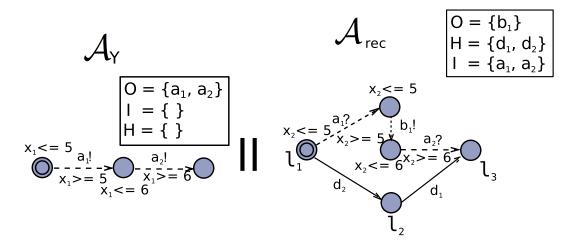

Given two timed I/O automata  $A_1 = (A_1, I_1, O_1, H_1)$  and  $A_2 = (A_2, I_2, O_2, H_2)$ . Their parallel composition is defined as  $A_1 \parallel A_2 = (A_1 \parallel A_2, I, O, H)$  where:

- $I = (I_1 \cup I_2) \setminus (O_1 \cup O_2)$ ,

- $O = (O_1 \cup O_2) \setminus (I_1 \cup I_2)$ ,

- $H = H_1 \cup H_2 \cup (I_1 \cap O_2) \cup (I_2 \cap O_1)$

if the following conditions hold:

- 1.  $I_1 \cap I_2 = O_1 \cap O_2 = \emptyset$

- **2.**  $H_1 \cap (I_2 \cup O_2 \cup H_2) = H_2 \cap (I_1 \cup O_1 \cup H_1) = \emptyset$ ,

- 3.  $X_1 \cap X_2 = \emptyset$  where  $X_1, X_2$  are the clock sets of  $A_1$  and  $A_2$ , respectively.

- 4.  $V_1 \cap V_2 = \emptyset$  where  $V_1, V_2$  are attribute variable sets of  $A_1$  and  $A_2$ , respectively.

Thus, two TIOA can be composed only if (1) their respective input and output signal sets are disjoint, (2) the internal signals of one automaton do not occur in the other automaton, (3) they do not share any clocks and (4) attributes. If these conditions are fulfilled the two TIOA are following called *compatible*. When modeling components using TIOA, the parallel composition of two components is only allowed if the associated TIOA holds: input ports are connected to output ports and vice versa. Internal signals sets need to be disjoint and variables (clocks and attributes) of different components, resp. TIOA also need to be disjoint. Moreover, connected ports become internal. In this way, parallel composition can be used to hierarchically structure a component-based system (see Sec. 6.2).

In this paper the focus is set on undesired behavioral properties of TIOA in the form of deadlocks and zeno-behavior. Formally, for a TIOA  $\mathcal{A}$ , a finite trace  $\alpha_d$  is called a *deadlock trace* if there exists a path for  $\alpha_d$  in  $\mathcal{T}_{\mathcal{A}}$ , the induced timed system of  $\mathcal{A}$ , that ends in a state  $s_d$  that contains no transition. A deadlock state is defined accordingly.

#### **Definition 12 (Deadlock)**

Let  $\mathcal{T}_A = (\Sigma, \mathcal{S}, \mathcal{S}^0, T)$  be the induced timed system of a TIOA  $\mathcal{A}$ . A state  $s_d \in \mathcal{S}$  is a deadlock state if  $\neg \exists t \in T$  with  $t = s_d \xrightarrow{\sigma} s_d'$  and  $\sigma \in \Sigma$  or  $t = s_d \xrightarrow{\tau} s_d'$  and  $\tau > 0 \land \tau \in \mathbb{R}^+$ .

Informally a deadlock state is a state where no outgoing transition can be taken including a signal or a delay greater than zero.

An infinite trace  $\alpha_z=\tau_1\sigma_1\tau_2\sigma_2\dots$  is called a *zeno trace* if there exists an  $\ell\in\mathbb{R}^+$  such that  $\sum_{i=1}^\infty \tau_i=\ell$ , i.e., if it has a finite time length. In contrast to a *deadlock*, for a *zeno trace* no associated state exists. As a consequence no definition of a zeno state is given.

# 3 Application Example - Engine Control

Now that required preliminary formal definitions for TA and TIOA have been given, the application example of the engine-control model shown in Fig. 1 is described in more detail. Like previously mentioned this application example is derived from an existing demo application shipped with the professional tool SystemDesk.<sup>8</sup> We first give a more detailed description of each included component. Afterwards we specify the timing behavior for each included component by an individual TIOA. This example is used in the remainder of this work to illustrate how the framework, which is introduced in the next sections, can be applied on typical applications in the domain of real-time embedded systems.

<sup>&</sup>lt;sup>8</sup>See http://www.dspace.com/systemdesk

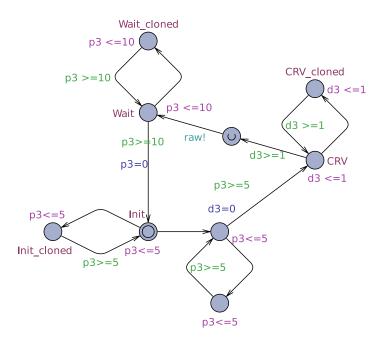

# 3.1 Component Engine-Model

The component *EngineModel* is an abstract representation of the behavior of the physical engine. It has two main functionalities: first, consuming the desired fuel rate and second, calculating appropriate raw output values. Within the raw output, information about the current throttle position, the actual speed value of the engine, the oxygen value as well as the actual pressure (e.g., of the combustion) is included. Because this information is always sent at the same point of time, only a single signal *raw* is considered within the subsequently introduced TIOA representing the timing-behavior of the component. Because in this work the focus is set on the non-functional and especially the timing-behavior, concrete values of send or received signals are following not considered.

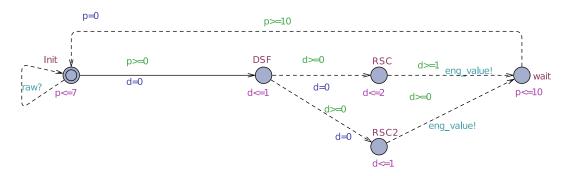

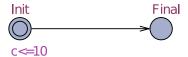

Figure 2: The component representing the physical behavior of the engine.

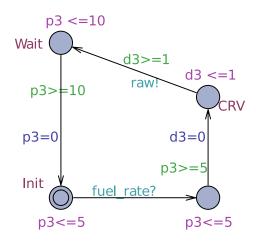

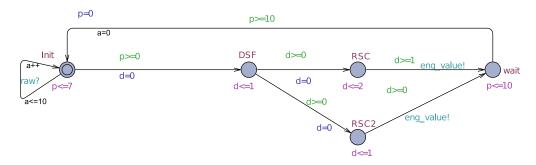

The associated TIOA is shown in Fig. 3. It consists of four locations. In the initial location *Init* the component is able receiving the current value of the fuel rate via the signal *fuel\_rate*. In the second location the TIOA waits for executing functionality and the third location (*CRV* as a shortcut for Calculate-Raw-Values) is associated with a state, where values received via the signal *fuel\_rate* are send to the real engine<sup>9</sup> and raw output values are read inside the component.<sup>10</sup> At this location the component is not able receiving arriving signals of type *fuel\_rate*. This is the case because in location *CRV* consistent values need to be send to the real engine. The fourth location *wait* is associated with the state where the component has finished its computation and is waiting for the next period to begin.

Following, the TIOA representing the timing behavior of component *EngineModel* is described in more detail. For graphically describing the structure of a TA, the same syntax like provided by the model checker UPPAAL (cf. [8]) is used. Each input signal is followed by a question mark and each output signal is followed by an exclamation mark. In such a manner, in the remainder of this work, input and output signals of a TIOA can be distinguished. The TIOA is allowed to stay in the initial location for at most five time units, according to the invariant of the form  $p3 \le 5$ , where p3 is a clock for measuring the progress of time in each period. Thus, location *Init* needs to be left at point in time five. The only outgoing edge need to receive the signal *fuel\_rate*. Thus, in the initial location the TIOA need to receive this signal within a time frame of five milliseconds (ms). After five ms the TIOA is required to leave the second location taking the edge to location *CRV* (Calculate Raw Values). When taking the edge to location *CRV*, clock d3 is reset to zero. The clock is used for measuring the amount of time spent for writing respectively reading sensor and actuator values when being in location *CRV*. The invariant  $d3 \le 1$  requires the TIOA leaving the location *CRV* at

<sup>&</sup>lt;sup>9</sup>This is realized by setting actuators of the real engine.

<sup>&</sup>lt;sup>10</sup>By reading and processing the output of analog-digital converters of the sensors of the real engine.

the latest after one time unit and the guard allows to leave the location also at the earliest after one time unit. When leaving location CRV, signal raw is send via the edge leading to location wait. The TIOA is required to stay in this location till the overall period of 10 time units is over (realized by the guard  $p3 \geq 10$  in combination with the invariant  $p3 \leq 10$ ). Afterwards, the edge to the initial location is taken, resetting the clock p3 to zero. The resulting TIOA  $\mathcal{A}_{EM} = (A_{EM}, I_{EM}, O_{EM}, H_{EM})$  consists of the input signal  $I_{EM} = \{fuel\_rate\}$ , the output signal  $O_{EM} = \{raw\}$ , an empty set of internal signals  $H_{EM} = \emptyset$  and the TA  $A_{EM}$  with constituent elements like described above.

Figure 3: The TIOA  $A_{EM}$  representing the engine model.

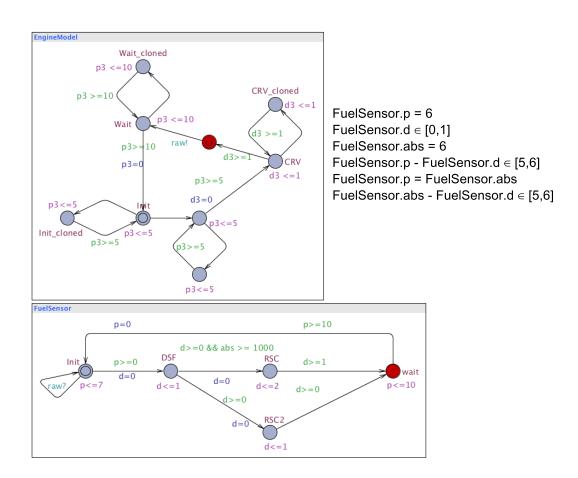

## 3.2 Component Fuel-Sensor

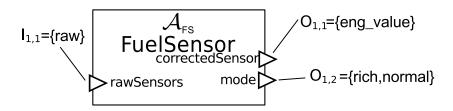

The component *FuelSensor* is responsible for evaluating the raw values provided by the component *EngineModel*. Depending on the current values and the absolute point of time in which they have been received, the mode of the engine is calculated and sent via a signal to the component *FuelController*. In case the engine is running for a short period (still in the warm up phase) or a failure is detected, the mode is set to *rich*. In this mode the component *FuelController* is responsible for calculating a fuel rate allowing the engine to run in a more robust way. In the case the engine is already warm and no failure is detected the mode is set to *normal*, requiring the component *FuelController* to calculate more optimized values for the fuel rate. Further, *FuelSensor* is responsible for realizing a post-processing of the raw values, allowing component *FuelController* more easily evaluating the raw value (e.g., removing sensor-failures if possible), resulting in the output signal *eng\_value*.

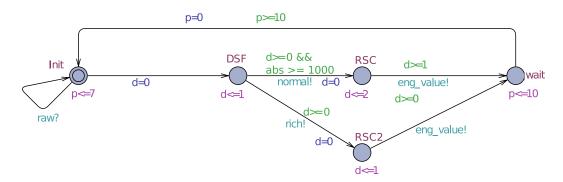

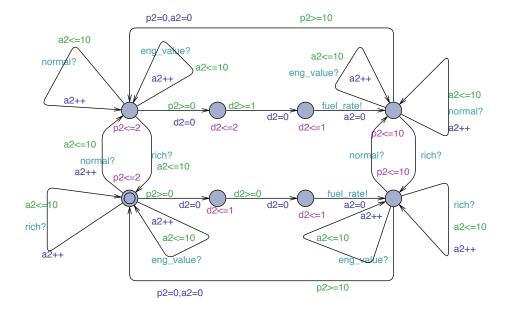

The associated TIOA is shown in Fig. 5. It contains the initial location *Init*. When being in this location, signals of type *raw* can be received by the component. In the successor location *DSF* (short for Detect-Sensor-Failures) the mode is derived. Depending on the absolute point in time and the received values the mode is set either to *normal* or to *rich* by sending the signal *normal*, resp. *rich*. When sending the signal *rich* or *normal*, the location with name *RSC*, respectively *RSC2* (Run-Sensor-Correction) is reached. The only difference between

Figure 4: The component representing functionality for processing raw sensor values.

these two locations is, that in case of being in mode *rich* a more simplified computation is used for processing the input values received via the signal *raw*. Accordingly, varying execution times are associated with both locations (RSC and RSC2). Afterwards the signal *eng\_value* is sent via the edge leading to location *wait*, where the component is waiting for the end of the period before taking the edge to the initial location. In the initial location, as well as in location *wait*, the component is able to receive incoming signals of type *raw*. In the remaining locations this is not allowed due to the fact that in locations *DSF* and *RSC* consistent data need to be provided when computing output signals.

Concerning the timing the associated TIOA  $A_{FS}$  behaves as follows.  $A_{FS}$  is allowed to stay in the initial location for at most seven time units reflected by the invariant  $p \leq 7$ , where p is a clock for measuring the current time of the overall period. When taking the edge to location DSF (Detect-Sensor-Failures) the clock d is reset to zero. Clock d is used for measuring the duration of the computation of each location (for locations associated with computations like described above). The computation of the error-detection takes at most one time unit reflected by the invariant  $d \leq 1$  in combination with the guard  $d \geq 0$ . In addition the outgoing edge to location RSC (Run-Sensor-Correction) has the guard  $abs \geq 1000$  for ensuring that the signal normal is only send if the engine is running for a longer time period. Depending on the current mode the successor location RSC resp. RSC2 is reached. In comparison to location RSC2, where a more simplified processing of the raw values is applied, location RSC requires more computation time (between 1-2 ms in contrast to 0-1 ms). The guards, invariants and resets, like shown in Fig. 5, realize this timing behavior. When leaving location RSC, resp. RSC2, the signal  $eng_{-}value$  is sent via the edge leading to location vait. At this location the TIOA is waiting till the overall period, measured by the clock vait vai

The resulting TIOA  $\mathcal{A}_{FS}=(A_{FS},I_{FS},O_{FS},H_{FS})$  consists of the input signal  $I_{FS}=\{raw\}$ , the output signals  $O_{FS}=\{rich,normal,eng\_value\}$ , an empty set of internal signals  $H_{FS}=\emptyset$  and the TA  $A_{FS}$  with constituent elements like described above. Zeno behavior in case of the incoming signals is prevented like previously described in the case of the TIOA representing the component EngineModel, using additional attribute variables. The complete resulting TIOA can be found in Appendix B.

Some of the components of the real application example, taken from the professional tool SystemDesk, allow receiving an arbitrary number of signals when not being in a state where signals are processed. This is also the case for component *FuelSensor* that is able to receive an arbitrary number of signals of type *raw* when being in location *Init*. This is the case because the last received value is considered to be the best value (last-value best-value

semantic). Unfortunately, allowing receiving an arbitrary number of signals introduces an undesired property of TIOA in form of zeno behavior. Also for any real implementation it cannot be considered that a component is able to receive an unbounded number of incoming signals in finite time. To avoid undesired behavior in case of zeno traces and to achieve a more realistic component behavior, it is only allowed to receive a limited number of signals when being in a location. For this purpose a dedicated single attribute variable *a* is used within the TIOA shown in Fig. 5. Each edge that receives signal *raw* has an additional guard ensuring that at most a maximal number of signals can be received while being in locations *Init*. Each time a signal *raw* is received the attribute variable is incremented by one. Only in case an edge is taken from a location not being able to receive signals to location *Init*, this attribute variable is reset to the value zero. For keeping the TIOA models simple and for allowing a better understanding, these additional variables and guards are not shown in Fig. 29. The complete TIOA models, including variables, guards and updates avoiding zeno behavior, can be found in Appendix B.

Figure 5: The TIOA  $A_{FS}$  representing the timing behavior of component *FuelSensor*.

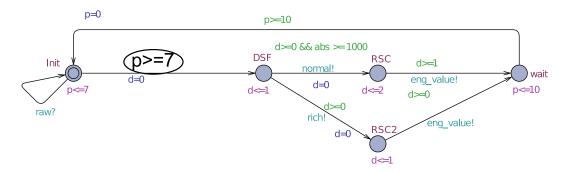

### 3.3 Component Fuel-Controller

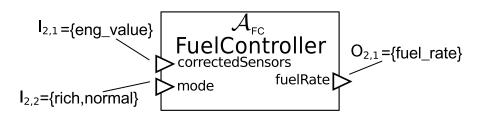

The component *FuelController* is responsible for calculating the appropriate fuel rate for the engine. Depending on the current mode as well as the current sensor values different computations are executed. In every case the approximate current airflow is calculated based on the input values received via the port *correctedSensor*. Depending on the current mode and the approximated airflow value the desired fuel rate is calculated, either for a more robust behavior when being in the mode *rich* or for a more optimized behavior when being in mode *normal*. In our model a mode-switch is indicated each time an appropriate signal is received via the port *mode*. Depending on the mode different functional parts are executed. When being in mode *rich*, a fuel rate appropriate for a more robust but less efficient engine operation is calculated. When being in mode *normal*, more optimized values for the fuel rate are derived.

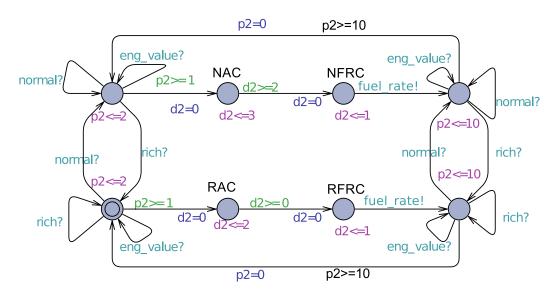

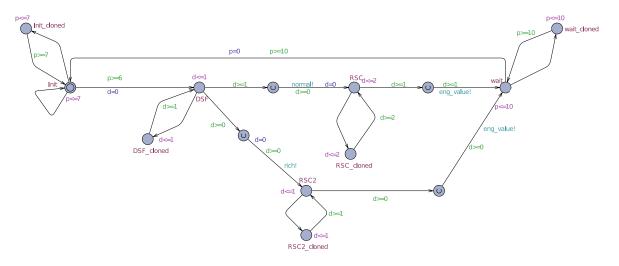

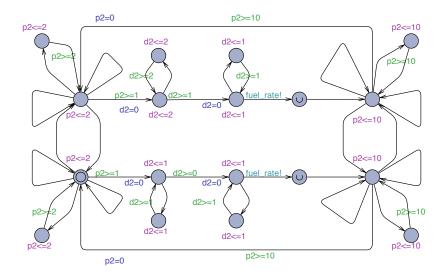

Fig. 7 shows an example how the state-based timing-behavior of the *FuelController* can be modeled using a TIOA. The TIOA basically describes two different behaviors, represented by the locations and edges at the upper respectively lower part of Fig. 7. Those located at the

Figure 6: The component representing the Fuel-Controller.

lower part do represent the behavior of the *FuelController* when being in mode *rich*. Those located at the upper part represent the behavior when being in mode *normal*. In the locations on the left as well as the locations on the right the component is able to receive incoming signals in case of signals *eng\_value*, *rich* and *normal*. When receiving signal *rich* or *normal*, the TIOA switches accordingly between the upper and lower locations, representing the different modes. In the upper part of the TIOA the location *NAC* (Normal-Airflow-Calculation) represents the state where the component *FuelController* calculates the airflow when being in mode *normal*.<sup>11</sup> In this mode, in contrast to mode *rich*, additional functionality for deriving a corrected and accurate value for the airflow is executed. This airflow is required for the successor location *NFRC* (Normal-Fuel-Rate-Calculation) where the optimized desired fuel rate is calculated. At the lower part of the TIOA shown in Fig. 7, locations and edges are shown representing the behavior parts for calculating the fuel rate when being in mode *rich*. In contrast to location *NAC*, location *RAC* (Rich-Airflow-Calculation) computes the resulting airflow without any correction. In location *RFRC* (Rich-Fuel-Rate-Calculation) a fuel rate is calculated allowing operating the engine in a more robust way.

The timing of the two different behavior parts, associated with the mode *rich* respectively *normal* like shown in Fig. 7, does only differ in case of locations *NAC* and *RAC*. Location *NAC*, associated with the normal execution mode can require more computation time for calculating the airflow compared to location *RAC*. The rest of the behavior is almost identical, starting in one of the locations on the left. Invariants require leaving these locations within the first two time units. The clock d2 is set to zero when taken the edge to location *NAC*, resp. *RAC*. The clock is used to reflect the execution times like described above by using appropriate guards and invariants. The timing behavior of the two different successor locations *NFRC* and *RFRC* is identical, again realized by an invariant ( $d2 \le 1$ ), indicating that the computation of the resulting output signal  $eng_{-}value$  is finished within one time unit. In the locations on the right the clock p2 is used to ensure that the TIOA will only switch back into the initial location when the overall period (10 time units) is over.

The resulting TIOA  $\mathcal{A}_{FC}=(A_{FC},I_{FC},O_{FC},H_{FC})$  consists of the input signals  $I_{FC}=\{rich,normal,eng\_value\}$ , the output signal  $O_{FC}=\{fuel\_rate\}$ , an empty set of internal signals  $H_{FC}=\emptyset$  and the TA  $A_{FC}$  with constituent elements like described above. Again, for avoiding zeno behavior an additional attribute variable is used. The resulting complete TIOA can be found in Appendix B.

<sup>11</sup> The airflow is not considered within the example. The airflow can be considered as an internal signal that is hidden for allowing a better understanding.

Figure 7: TIOA  $A_{FC}$  representing the timing behavior of component *Fuel-Controller*.

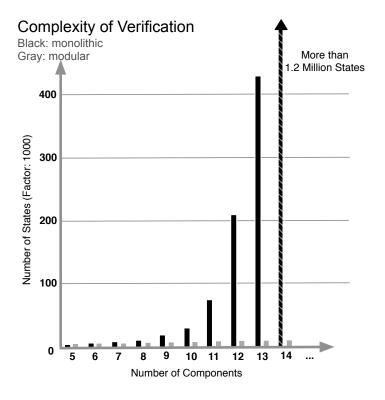

The introduced application example is rather small compared to real applications in the domain of embedded real-time systems, containing a huge number of components. Nevertheless, also in case of the introduced example major differences concerning the complexity of the analysis are shown in Sec. 8.3 when applying the subsequently introduced scalable reasoning scheme, compared to a monolithic approach where all involved TIOA are analyzed at once. Further, it can be seen that the application example, as a typical example for real-time embedded systems, provides components with restricted resources (R2), not being able to receive any amount of signals at any state. As an example see the TIOA shown in Fig. 7, not being able receiving signals when being in one of the locations NAC, NFRC, RAC and RFRC. Further, also in the case of this more simple application example non-deterministic behavior exists. This is the case because execution times of functional parts can only be expressed using upper and lower bound (associated with Best-Case and Worst-Case execution times) in form of invariants and guards of the associated TIOA. As a consequence, like in the case of the TIOA shown in Fig. 7, state-changes occur nondeterministically. As an example the transition between location NAC and NFRC cannot be predicted based on the observation of time and exchanged signals only. As a consequence, approaches that do require deterministic behavior for realizing a modular and scalable check (cf. [11]) seem to be too restrictive to be applied on such application examples. While the shown behavior models have been derived manually from a given architecture model, 12 such TA models can also be automatically derived like shown in [19].

<sup>&</sup>lt;sup>12</sup>In case of a given AUTOSAR model.

# 4 Progressive and Receptive TIOA

Following the notion of progressive and receptive behavior is introduced, like defined in [16]. It is shown that progressive and receptive behavior requires strong assumptions that are hard or even impossible to achieve for resource restricted embedded components. Based on the given property of progressive behavior a new property is defined as a relaxed condition of progressive and receptive behavior that does not require such strong assumptions. This relaxed property is used to verify the correctness of the previously introduced example.

In [16] desired properties, like in the case of the absence of deadlock and zeno traces, is captured by the notion of *progressive* TIOA. A TIOA  $\mathcal{A}=(A,I,O,H)$  is called *progressive* if the induced timed system does not allow to observe any zeno executions or deadlocks if the environment includes no deadlocks and zeno behavior. The definition of progressive behavior according to [16] is rather strong. Fulfilling the property of progressive behavior, according to [16], a TIOA is also I/O feasible, what means that in each state of  $\mathcal{A}$  an arbitrary trace  $\beta=\tau_1,\sigma_1,\tau_2,...$ , consisting of signals  $\sigma_i\in I$  and of arbitrary delays  $\tau_i$ , can be accommodated by  $\mathcal{A}$ . Thus, an I/O feasible TIOA automaton  $\mathcal{A}:=(A,I,O,H)$  is able to accommodate arbitrary input actions (signals) occurring at arbitrary time. For an I/O feasible TIOA  $\mathcal{A}$  holds that each trace  $\alpha:=\tau_1\sigma_1\tau_1\sigma_1...$ , consisting of signals  $\sigma_i\in I$ ,  $\alpha\in traces\_from(\omega,\mathcal{A})$  can be observed on  $\mathcal{A}$  starting in any state s of  $\mathcal{A}$ , respectively of the induced timed system.

However, the requirement of progressiveness of components is rather strong. According to [16] instead of progressive behavior also receptive behavior, as a weaker condition, can be used. Receptive behavior is based on the definition of a strategy. Therefore, first it is defined what a strategy is in the context of a TIOA. For being able to reason about a strategy the edges of a TA, and as result also of a TIOA are partitioned into *controllable* and *uncontrollable* once.

#### **Definition 13 (Disjoint Partitioned TA)**

A Disjoint Partitioned TA is defined as follows. Let  $A=(\Sigma,\mathcal{L},\mathcal{UL},\mathcal{CL},\mathcal{L}^0,X,V,\mathcal{I},E)$  be a (extended) TA where a disjoint partitioning of controllable edges  $E_n$  and uncontrollable edges  $E_c$  with  $E_n\cap E_c=\emptyset$  and  $E_n\cap E_c=E$  exists.  $A'=(\Sigma,\mathcal{L},\mathcal{UL},\mathcal{CL},\mathcal{L}^0,X,V,\mathcal{I},E')$  containing uncontrollable edges  $E_n\in E$  with  $E_n\in E'$  and controllable edges  $E'_c\cap E_n=\emptyset$  with  $E'_c\cup E_n=E'$  is a Disjoint Partitioned TA of A.

Based on the definition of a partitioning of the edges of a TA, now the semantics of a valid strategy is defined. In the reminder of this work, whenever a strategy is mentioned a valid strategy according to Def. 14 is meant.

### **Definition 14 (Valid Strategy)**

Given TA  $A=(\Sigma,\mathcal{L},\mathcal{UL},\mathcal{CL},\mathcal{L}^0,X,V,\mathcal{I},E)$ . Let  $A'=(\Sigma,\mathcal{L},\mathcal{UL},\mathcal{CL},\mathcal{L}^0,X,V,\mathcal{I},E')$  be a Disjoint Partitioned TA A' of A according to Def. 13, where  $E=E_c\cup E_n$  and  $E'=E'_c\cup E'_n$ . A' is a valid strategy for A if the following conditions are fulfilled: 1)  $E_n=E'_n$ . 2)  $\forall e=(l_1,a,\varphi,\lambda,l'_1)\in E'_c$  holds:  $\exists e_1=(l_1,a,\varphi',\lambda,l'_1)\in E_c$  and for all states s of the induced time system  $\mathcal{T}_{A'}$  of A', being in location l holds: if  $\varphi'$  is enabled also  $\varphi$  is enabled ( $\varphi'\implies\varphi$ ). Further, for a valid strategy holds that no deadlock state or zeno trace is observable on A'.

A strategy is valid if and only if controllable edges are removed or modified in such a way that the resulting observable behavior is a subset of the observable behavior of the original TA A. As a consequence each valid strategy A' realizes a subset of the observable behavior of the original TA A, like in the case of the induced timed system and the observable traces. As a consequence holds for each valid strategy A' of a TA A:  $traces(A') \subseteq traces(A)$ .

The notion of a strategy can be applied to the model of TIOA by simply allowing only edges including signals of the set of internal signals to be controllable. Thus, a valid strategy  $\mathcal{A}'=(A',I,H,O)$  of a TIOA  $\mathcal{A}=(A,I,H,O)$  is defined based on the TA A included in TIOA  $\mathcal{A}$  where an edge of A is only allowed to be controllable if only signals of H are included in this edge. In such a manner different strategies of different TIOA are kept independent from each other under composition. This is the case because only edges including internal signals are allowed to be controllable. Like also done in [16] strategies are used similar to winning strategies as in [5] for different types of games for timed automata. Defining strategies based on timed automata allows avoiding introducing extra mathematical machinery.

The definition of receptive behavior in [16] is based on progressive behavior and a timed I/O automaton  $\mathcal{A}$  is called *receptive* if there exists a strategy  $\mathcal{A}'$  for  $\mathcal{A}$  that is progressive. In other words, a TIOA is receptive if a strategy  $\mathcal{A}'$  exists that is able to resolve all nondeterministic choices in such a manner that  $\mathcal{A}$  is not able to generate infinitely many internal transitions in finite time, no matter how the environment behaves. Furthermore, for a receptive TIOA it is required that in the case  $\mathcal{A}$  is executed according to strategy  $\mathcal{A}'$ , time can always progress if the environment allows to do so. As a consequence no deadlock and no zeno behavior can occur for the strategy  $\mathcal{A}'$  of a receptive TIOA  $\mathcal{A}$ . For example, if a component in the environment decides to send no signal to  $\mathcal{A}$  within the time period t,  $\mathcal{A}$  under t0 allows to let time pass for at least t1 time units without receiving any signal.

Finding a strategy and thus determining whether a TIOA is receptive or not can be decided using timed two player games (see [9, 16]). For this purpose, edges of a TIOA need to be partitioned into *controllable* and *uncontrollable* according to Def. 13, depending on whether the observed signal  $\sigma$  is internal, i.e.  $\sigma \in H$ , or not.

In a timed two player game (cf. [9]) a player can choose controllable transitions and its opponent can choose the uncontrollable transitions. Depending on the winning condition, e.g., reaching or avoiding specific states, such a timed two player game eventually results in a strategy, indicating that a strategy  $\mathcal{A}'$  according to Def. 14 can exist, where the player is able to win the game no matter which choices its opponent makes.

Taking two compatible TIOA  $\mathcal{A}_1$  and  $\mathcal{A}_2$  into consideration while both on their own fulfill all required properties like in the case of progressive or receptive behavior. One reasonable question is if such properties are preserved under composition. In [16] this question has been answered for progressive TIOA.

#### Theorem 4.1

(from [16]) If  $A_1$  and  $A_2$  are compatible progressive TIOA, then their composition is also progressive.

Further it has been shown in [16] that the composition of two compatible receptive TIOA

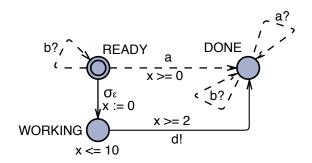

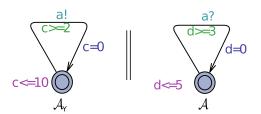

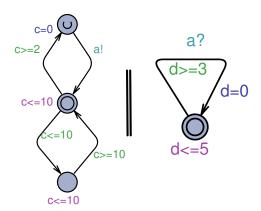

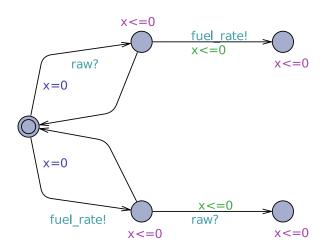

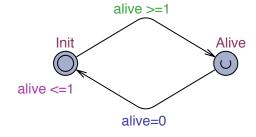

is also receptive. Thus, the property of progressive behavior is sufficient for preserving properties like deadlock freedom and absence of zeno behavior under composition. It is not required to compare the possible input, respectively output traces of the individual automata. Further holds that receptive behavior is preserved under composition, still allowing finding a strategy avoiding zeno and deadlock behavior for the composition. 13 Each progressive or receptive TIOA needs to be also I/O feasible (see [16]). In the following it is shown that even I/O feasibility is hard to achieve for embedded systems and as a result progressive and receptive behavior is even more unrealistic. An I/O feasible automaton A is at least capable to accommodate any sequence of arbitrary input signals occurring at arbitrary points of time. On the one hand, this property allows ignoring the input traces for the considered components, which are able to consume any sequence of signals when being composed. Therefore, it helps protecting IP (R3) as well as supports a modular, scalable analysis (R1). On the other hand, requiring an automaton to be I/O feasible is an unrealistic or at least very difficult to match property for a relevant portion of typical embedded real-time systems. This is the case because I/O feasibility does not allow specifying a concrete upper bound of signals that a receptive or progressive TIOA  $\mathcal A$  needs to be able to consume. If the property of I/O feasibility holds, A can consume any trace  $\alpha$  with time length n including m signals. Consider a time length of n=10,  $\mathcal{A}$  needs to be able to consume any amount of signals within this 10 time units, e.g., 10, 1000, 10000000 signals or even more. Only zeno traces, consisting of an infinite number of signals are not allowed. Obviously, such a property can rarely be achieved for a huge portion of resource restricted real-time embedded systems. This is the case because only limited resources can be assumed (requirement (R2)). Only for systems with unrestricted resources or system that are able to simply ignore signals (simply skip incoming signals without consuming resources when skipping signals), the property of receptive or progressive behavior seems to be realistic. As a result the existing TIOA framework can rarely support requirement R2. An example of a TIOA  $A_r$  is shown in Fig. 8.  $A_r$  consists of the tuple (A, I, H, O), with  $I = \{a, b\}$ ,  $O = \{d\}$ ,  $H = \{\sigma_{\epsilon}\}$  and the single clock x. The initial location READY has an outgoing edge leading to location Done. This edge includes the guard  $x \ge 0$  over the clock x. As a result the edge can be taken if the signal a is received and the guard is fulfilled. A second cyclic edge exists that can be taken if the signal b is received. A third edge exists leading to location WORKING. This edge contains the internal signal  $\sigma_{\epsilon}$  that do not need to synchronize with any other TIOA. Further, when taking this edge clock x is reset to zero. Location WORKING contains the invariant  $x \le 10$ , allowing staying in this location for at most 10 time units. For allowing a better understanding question marks are used for depicting input signal that are received and exclamation marks are used for depicting output signals that are send. Internal signals do not contain exclamation, resp. question marks. Solid lines depict controllable edges and dashed lines depict uncontrollable edges.

$\mathcal{A}_r$  is not progressive because each time  $\mathcal{A}_r$  enters location WORKING, no signal included in the input I is observable on  $\mathcal{A}_r$  for at least two time units. As a result  $\mathcal{A}_r$  is not progressive because a reachable state exists, when being in location WORKING, where traces of the form  $\alpha := 0a0a...$  are not observable. Nevertheless,  $\mathcal{A}_r$  is receptive because a strategy A' exists for which holds A' is progressive. Such a strategy exists, e.g., by disabling the

<sup>&</sup>lt;sup>13</sup>It is not required to compare the strategies. Strategies in [16], like also done in this work are defined to be orthogonal because different strategies of compatible TIOA do not share signals or variables (clocks or attributes) and controllable edges are restricted to those including internal signals.

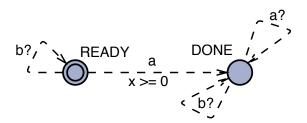

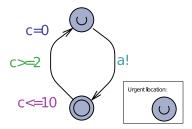

edge from *READY* to *WORKING*. Because the solid edges include only signals of H and all remaining edges are only enabled if the edges of the original TIOA are enabled, A' is a valid strategy according to Def. 14. This is the case because in each reachable state of A' any trace  $\alpha$ , consisting of arbitrary sequences of signals a and b as well as time delays can be observed while excluding deadlocks or zeno traces consisting of internal signals. As a result  $\mathcal{A}_r$  obviously is receptive. The previously discussed implications of progressive and receptive behavior can also be found in the example of Fig. 8. As soon as  $\mathcal{A}_r$  is able to reach a state where no signal of I can be consumed for longer than zero time units, the property of progressive behavior is violated. For the receptive TIOA  $\mathcal{A}_r$  holds that it can be refined by the strategy A', excluding all states where signals in I cannot be observed for more than zero time units, or in other words the example works fine (behaves progressive) when avoiding location WORKING (consuming time). The resulting progressive TA, resp. TIOA A' is shown in Fig. 9.

Figure 8: A TIOA  $A_r = (A, I, O, H)$  being receptive and not progressive with  $I = \{a, b\}$ ,  $O = \{d\}$ ,  $H = \{\sigma_{\epsilon}\}$ , and a single clock x.

Figure 9: A TA, resp. TIOA A' being progressive with  $I=\{a,b\},\ O=\{d\},\ H=\emptyset,$  and the single clock x.

# 5 Language Progressive and Language Receptive TIOA

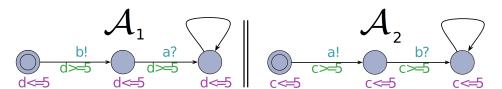

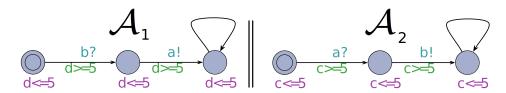

As discussed in Section 4, the properties of progressive and receptive behavior are too demanding and cannot be fulfilled by typical embedded real-time systems using restricted resources (requirement (R2)). This is also reflected by the application example introduced in Sec. 3, where states, respectively locations exist, not allowing receiving an input signal due to the fact that during processing already received signals, no new signals are allowed to arrive. As a consequence, based on the previously defined properties, which exclude deadlocks and zeno-behavior for any possible environment that allows time to diverge, now relaxed conditions are defined. Receptiveness and progressiveness of an automaton A is expected only w.r.t. the given input language \u00e1, and not for arbitrary sequences of input signals. The relaxed conditions do not require that a component need to be capable of receiving an arbitrary finite amount of signals in an arbitrary time frame, and as a result support systems with limited resources, fulfilling requirement (R2). Similarly to receptive resp. progressive behavior, it is required that the automaton has no undesired behavior in the form of deadlocks or zeno-behavior for those traces that are included in  $\Upsilon$ . Following only TIOA  $\mathcal{A}_{\Upsilon}$  with  $traces(\mathcal{A}_{\Upsilon}) \subseteq \Upsilon$  that do not include a deadlock state or zeno trace are considered to be a valid representation of input languages. In the reminder of this work a zeno and deadlock free TIOA is called a *valid* TIOA. In other words, A is not able to produce any internal zeno-behavior nor runs into a deadlock, if the environment sends an arbitrary sequence (trace) of signals to A that is included in  $\Upsilon$ .

# **Definition 15 (Language Progressive)**

A TIOA  $\mathcal{A} = (A, I, O, H)$  is called  $\Upsilon$ -progressive (written as  $\Upsilon pro \mathcal{A}$ ) for language  $\Upsilon$  with  $signals(\Upsilon) \subseteq I$  and  $\Upsilon$  not including a deadlock or zeno trace if for all compatible and valid TIOA  $\mathcal{A}_{\Upsilon}$  with  $traces(\mathcal{A}_{\Upsilon}) \subseteq \Upsilon$  holds:  $\mathcal{A}_{\Upsilon} \parallel \mathcal{A}$  does not include a deadlock or zeno trace.