# Efficient State Management with Persistent Memory

# **Lawrence Benson**

Universitätsdissertation zur Erlangung des akademischen Grades

doctor rerum naturalium (Dr. rer. nat.)

in der Wissenschaftsdisziplin IT-Systems Engineering

eingereicht an der Digital-Engineering-Fakultät der Universität Potsdam

**Datum der Disputation:** 09.11.2023

Unless otherwise indicated, this work is licensed under a Creative Commons License Attribution 4.0 International.

This does not apply to quoted content and works based on other permissions. To view a copy of this licence visit:

https://creativecommons.org/licenses/by/4.0

# **Betreuer**

**Prof. Dr. Tilmann Rabl**Hasso Plattner Institut, Universität Potsdam

# **Gutachter**

**Prof. Tianzheng Wang, PhD**Simon Fraser University

**Prof. Pinar Tözün, PhD**IT University of Copenhagen

Published online on the Publication Server of the University of Potsdam: https://doi.org/10.25932/publishup-62563 https://nbn-resolving.org/urn:nbn:de:kobv:517-opus4-625637

# **Abstract**

Efficiently managing large state is a key challenge for data management systems. Traditionally, state is split into fast but volatile state in memory for processing and persistent but slow state on secondary storage for durability. Persistent memory (PMem), as a new technology in the storage hierarchy, blurs the lines between these states by offering both byte-addressability and low latency like DRAM as well persistence like secondary storage. These characteristics have the potential to cause a major performance shift in database systems.

Driven by the potential impact that PMem has on data management systems, in this thesis we explore their use of PMem. We first evaluate the performance of real PMem hardware in the form of Intel Optane in a wide range of setups. To this end, we propose PerMA-Bench, a configurable benchmark framework that allows users to evaluate the performance of customizable database-related PMem access. Based on experimental results obtained with PerMA-Bench, we discuss findings and identify general and implementation-specific aspects that influence PMem performance and should be considered in future work to improve PMem-aware designs. We then propose Viper, a hybrid PMem-DRAM key-value store. Based on PMem-aware access patterns, we show how to leverage PMem and DRAM efficiently to design a key database component. Our evaluation shows that Viper outperforms existing key-value stores by 4-18× for inserts while offering full data persistence and achieving similar or better lookup performance. Next, we show which changes must be made to integrate PMem components into larger systems. By the example of stream processing engines, we highlight limitations of current designs and propose a prototype engine that overcomes these limitations. This allows our prototype to fully leverage PMem's performance for its internal state management. Finally, in light of Optane's discontinuation, we discuss how insights from PMem research can be transferred to future multi-tier memory setups by the example of Compute Express Link (CXL).

Overall, we show that PMem offers high performance for state management, bridging the gap between fast but volatile DRAM and persistent but slow secondary storage. Although Optane was discontinued, new memory technologies are continuously emerging in various forms and we outline how novel designs for them can build on insights from existing PMem research.

# Zusammenfassung

Die effiziente Verwaltung großer Zustände ist eine zentrale Herausforderung für Datenverwaltungssysteme. Traditionell wird der Zustand in einen schnellen, aber flüchtigen Zustand im Speicher für die Verarbeitung und einen persistenten, aber langsamen Zustand im Sekundärspeicher für die Speicherung unterteilt. Persistenter Speicher (PMem), eine neue Technologie in der Speicherhierarchie, lässt die Grenzen zwischen diesen Zuständen verschwimmen, indem er sowohl Byte-Adressierbarkeit und geringe Latenz wie DRAM als auch Persistenz wie Sekundärspeicher bietet. Diese Eigenschaften haben das Potenzial, die Leistung von Datenbanksystemen grundlegend zu verändern.

Aufgrund der potenziellen Auswirkungen, die PMem auf Datenverwaltungssysteme hat, untersuchen wir in dieser Arbeit ihre Verwendung von PMem. Zunächst evaluieren wir die Leistung von echter PMem-Hardware in Form von Intel Optane in einer Vielzahl von Konfigurationen. Zu diesem Zweck stellen wir PerMA-Bench vor, ein konfigurierbares Benchmark-Framework, mit dem Benutzer die Leistung von anpassbaren datenbankbezogenen PMem-Zugriffen untersuchen können. Auf der Grundlage der mit PerMA-Bench erzielten experimentellen Ergebnisse diskutieren wir unsere Erkenntnisse und identifizieren allgemeine und implementierungsspezifische Aspekte, die die PMem-Leistung beeinflussen und in zukünftigen Arbeiten berücksichtigt werden sollten, um PMem-fähige Designs zu verbessern. Anschließend präsentieren wir Viper, einen hybriden PMem-DRAM Key-Value-Store. Basierend auf PMem-bewussten Zugriffsmustern zeigen wir, wie PMem und DRAM effizient genutzt werden können, um eine wichtige Datenbankkomponente zu entwickeln. Unsere Evaluierung zeigt, dass Viper bestehende Key-Value-Stores bei Einfügungen um 4- bis 18-mal übertrifft, während er gleichzeitig vollständige Datenpersistenz bietet und ähnliche oder bessere Lookup-Leistung erzielt. Als nächstes zeigen wir, welche Änderungen vorgenommen werden müssen, um PMem-Komponenten in größere Systeme zu integrieren. Am Beispiel von Datenstromverarbeitungssystemen zeigen wir die Einschränkungen aktueller Designs auf und stellen einen Prototyp eines Systems vor, das diese Einschränkungen überwindet. Dadurch kann unser Prototyp die Leistung von PMem für die interne Zustandsverwaltung voll ausnutzen. Schließlich erörtern wir angesichts der Abkündigung von Optane, wie Erkenntnisse aus der PMem-Forschung am Beispiel von Compute Express Link (CXL) auf künftige mehrstufige Speicher-Setups übertragen werden können.

Insgesamt zeigen wir, dass PMem eine hohe Leistungsfähigkeit für die Zustandsverwaltung bietet und die Lücke zwischen schnellem, aber flüchtigem DRAM und beständigem, aber langsamem Sekundärspeicher schließt. Obwohl Optane eingestellt wurde, entstehen ständig neue Speichertechnologien in verschiedenen Formen, und wir skizzieren, wie neuartige Entwürfe für sie auf den Erkenntnissen aus der bestehenden PMem-Forschung aufbauen können.

# Contents

| Αl | bstra | ct     |                                       | iii  |

|----|-------|--------|---------------------------------------|------|

| Ζι | usamı | menfas | ssung                                 | v    |

| Co | onten | its    |                                       | vii  |

| Li | st of | Figure | S                                     | xi   |

| Li | st of | Tables |                                       | xiii |

| 1  | Intr  | oducti | on                                    | 1    |

|    | 1.1   | Motiv  | ration                                | 1    |

|    | 1.2   | Resea  | rch Contribution                      | 5    |

|    | 1.3   |        | ical Contributions and Impact         |      |

|    | 1.4   | Additi | ional Contributions                   | 8    |

|    | 1.5   | Thesis | s Outline                             | 9    |

| 2  | Bac   | kgrour | nd                                    | 11   |

|    | 2.1   | Persis | tent Memory                           | 11   |

|    |       | 2.1.1  | Types                                 | 11   |

|    |       | 2.1.2  | Intel Optane                          | 12   |

|    |       | 2.1.3  | Accessing Persistent Memory           | 15   |

|    |       | 2.1.4  | Atomicity and Durability              | 18   |

|    |       | 2.1.5  | Programming Interfaces and APIs       | 20   |

| 3  | Ben   | chmar  | king Persistent Memory Access         | 23   |

|    | 3.1   | Introd | luction                               | 23   |

|    | 3.2   | Introd | lucing PerMA-Bench                    | 25   |

|    |       | 3.2.1  | Runtime                               | 25   |

|    |       | 3.2.2  | Custom Workloads and Configuration    |      |

|    |       | 3.2.3  | Persist Instructions                  |      |

|    | 3.3   | PerM   | A-Bench Results                       | 29   |

|    |       | 3.3.1  | Setup And Methodology                 |      |

|    |       | 332    | Raw Performance Workloads – Bandwidth | 31   |

|   |      | 3.3.3    | Raw Performance Workloads - Latency        | 35 |

|---|------|----------|--------------------------------------------|----|

|   |      | 3.3.4    | Database-Related Workloads                 | 38 |

|   |      | 3.3.5    | Single Server Performance                  | 43 |

|   | 3.4  | Server   | Price-Performance                          | 47 |

|   | 3.5  |          | ssion                                      | 50 |

|   | 3.6  |          | d Work                                     | 51 |

|   | 3.7  |          | usion                                      | 52 |

| 4 | Vipo | er: An E | Efficient Hybrid PMem-DRAM Key-Value Store | 53 |

|   | 4.1  | Introdu  | uction                                     | 53 |

|   | 4.2  | Backgr   | round                                      | 55 |

|   | 4.3  | Viper:   | A Hybrid Key-Value Store                   | 55 |

|   |      | 4.3.1    | Hybrid Design                              | 56 |

|   |      | 4.3.2    | Architecture                               | 59 |

|   | 4.4  | Key-Va   | alue Store Operations                      | 62 |

|   |      | 4.4.1    | Viper Client                               | 63 |

|   |      | 4.4.2    | Put                                        | 64 |

|   |      | 4.4.3    | Get                                        | 66 |

|   |      | 4.4.4    | Update                                     | 67 |

|   |      | 4.4.5    | Delete                                     | 67 |

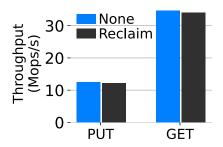

|   |      | 4.4.6    | Space Reclamation                          | 68 |

|   |      | 4.4.7    | Recovery                                   | 68 |

|   | 4.5  | Evalua   | ution                                      | 69 |

|   |      | 4.5.1    | Setup and Methodology                      | 69 |

|   |      | 4.5.2    | Other Systems                              | 69 |

|   |      | 4.5.3    | Micro Benchmarks                           | 70 |

|   |      | 4.5.4    | YCSB                                       | 79 |

|   | 4.6  | Related  | d Work                                     | 80 |

|   | 4.7  | Conclu   | asion                                      | 82 |

| 5 | Dar  | win: Sc  | cale-In Stream Processing                  | 83 |

|   | 5.1  | Introdu  | uction                                     | 83 |

|   | 5.2  | Backgr   | round                                      | 85 |

|   | 5.3  | Curren   | nt SPE Challenges                          | 86 |

|   |      | 5.3.1    | Focus of Existing Systems                  | 86 |

|   |      | 5.3.2    | State Management                           | 88 |

|   |      | 5.3.3    | Resource Inefficiency                      | 88 |

|   |      | 5.3.4    | Overall System Optimization                | 88 |

|    | 5.4   | Scale- | In Stream Processing                              | 89  |

|----|-------|--------|---------------------------------------------------|-----|

|    |       | 5.4.1  | Opportunities for State Management                | 90  |

|    |       | 5.4.2  | Opportunities for Resource Inefficiency           | 93  |

|    |       | 5.4.3  | Opportunities for System Optimization             | 94  |

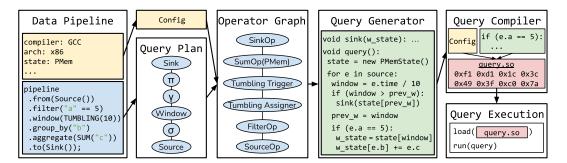

|    | 5.5   | Introd | lucing Darwin                                     | 95  |

|    |       | 5.5.1  | Darwin Architecture                               | 95  |

|    |       | 5.5.2  | Performance                                       | 97  |

|    | 5.6   | Concl  | usion                                             | 98  |

| 6  |       |        | Can Learn from Persistent Memory for CXL          | 99  |

|    | 6.1   | Introd | luction                                           | 99  |

|    | 6.2   | Comp   | ute Express Link                                  | 100 |

|    | 6.3   | Trans  | ferring Insights from PMem to CXL-Attached Memory | 100 |

|    | 6.4   | Concl  | usion                                             | 104 |

| 7  | Con   | clusio | n & Outlook                                       | 107 |

|    | 7.1   | Concl  | usion                                             | 107 |

|    | 7.2   | Resear | rch Outlook                                       | 108 |

| Re | efere | nces   |                                                   | 111 |

# List of Figures

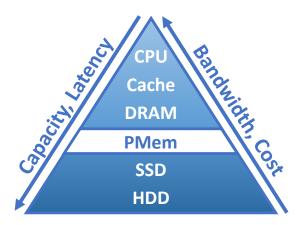

| 1.1  | PMem sits between SSDs and DRAM in the storage hierarchy 2      |

|------|-----------------------------------------------------------------|

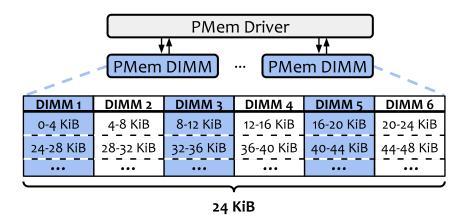

| 2.1  | Six interleaved Optane DIMMs span a continuous 24 KiB region 12 |

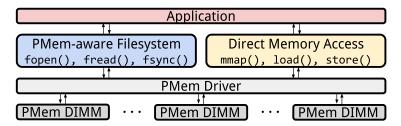

| 2.2  | Standard PMem access modes                                      |

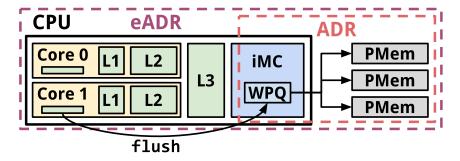

| 2.3  | Writing to NVDIMM-Ps from the CPU                               |

| 3.1  | Execution cycle of a benchmark in PerMA-Bench                   |

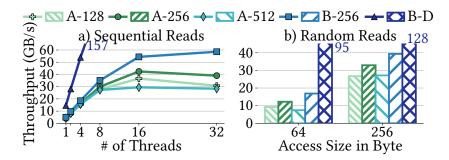

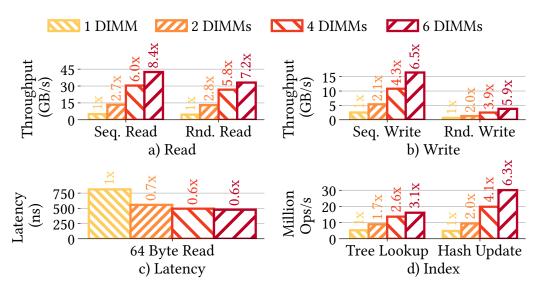

| 3.2  | Sequential and random read bandwidth                            |

| 3.3  | Thread and access size impact on sequential writes              |

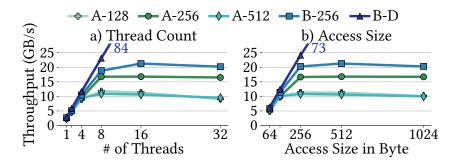

| 3.4  | Impact of persist instruction on write bandwidth                |

| 3.5  | 256 Byte random read + write latency                            |

| 3.6  | Double-flush latency                                            |

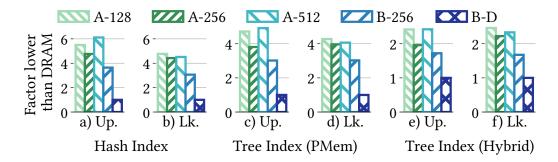

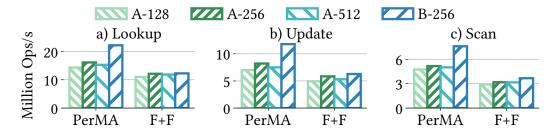

| 3.7  | PMem index workloads compared to DRAM                           |

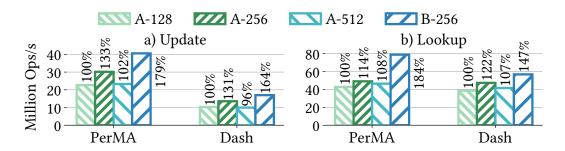

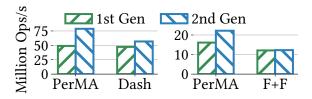

| 3.8  | Hash index in PerMA and Dash                                    |

| 3.9  | Tree index in PerMA and FAST+FAIR 41                            |

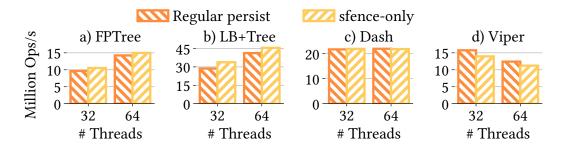

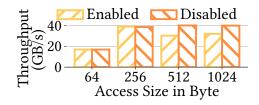

| 3.10 | Impact of eADR on write performance                             |

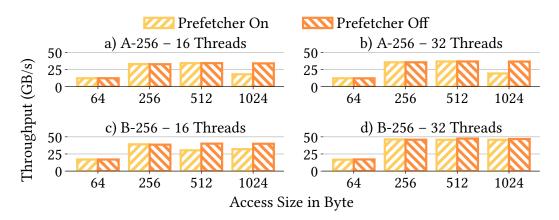

| 3.11 | Impact of prefetcher on random read bandwidth                   |

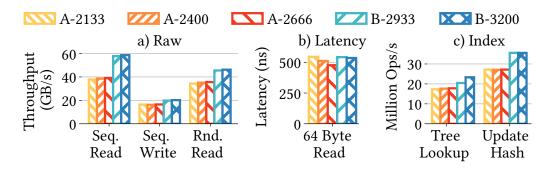

| 3.12 | Performance-impact of varying memory bus speeds                 |

| 3.13 | Impact of number of DIMMs in the server                         |

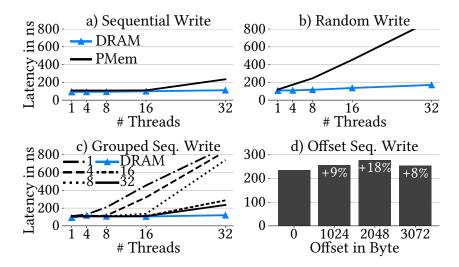

| 4.1  | Write latency for various write patterns to DRAM and PMem 57    |

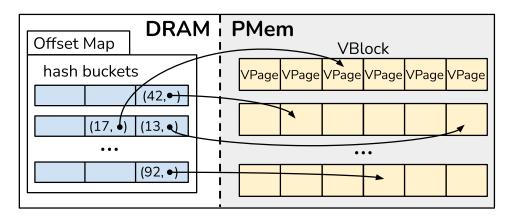

| 4.2  | Viper's storage aligned with 4 KB PMem layout                   |

| 4.3  | Viper's architecture                                            |

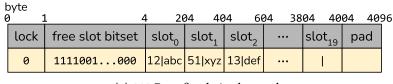

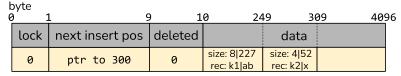

| 4.4  | VPage layout with example entries 61                            |

| 4.5  | Client requesting new VBlock 63                                 |

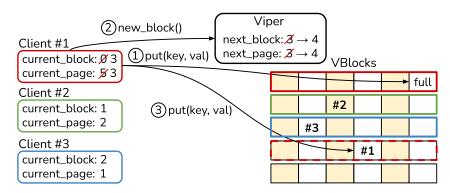

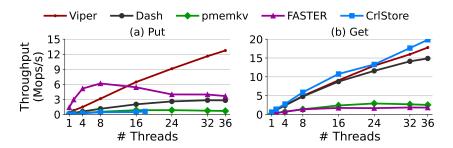

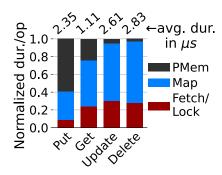

| 4.6  | Performance of core KVS operations                              |

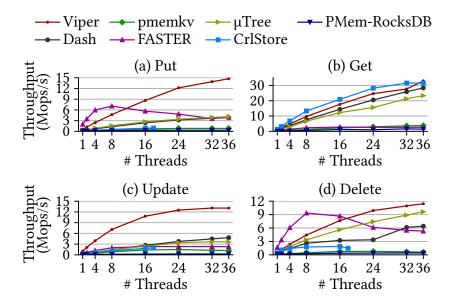

| 4.7  | Key-value size impact                                           |

| 4.8  | Variable-sized ~216 Byte records                                |

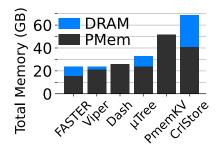

| 4.9  | Total memory                                                    |

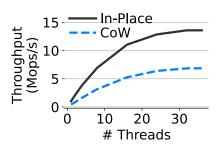

| 4.10 | Update strategy                                                 |

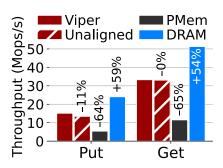

| 4.11 | Viper versions                                                  |

| 4.12 | Operation breakdown                                             |

| 4.13 | Space reclamation                                               |

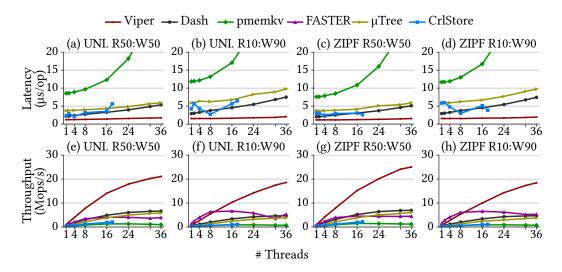

| 4.14 | YCSB latency and throughput                                     |

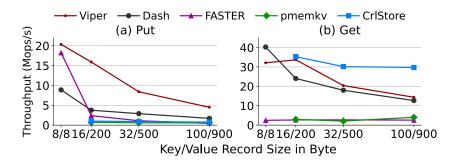

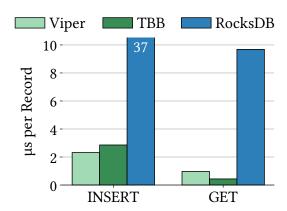

| 5.1 | Insert and get performance                            | 90  |

|-----|-------------------------------------------------------|-----|

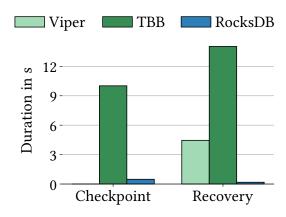

| 5.2 | Checkpoint and recovery duration.                     | 91  |

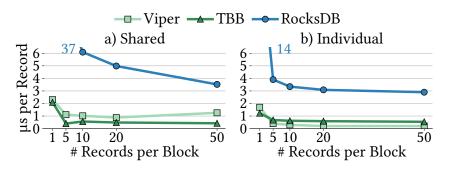

| 5.3 | Grouped state access performance                      | 92  |

| 5.4 | Darwin's architecture and execution flow              | 95  |

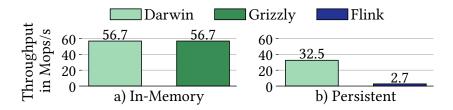

| 5.5 | Throughput of Darwin, Grizzly, and Flink              | 98  |

| 6.1 | Performance of PerMA and actual index implementations | 101 |

| 6.2 | Impact of prefetcher on PMem random read bandwidth    | 102 |

# List of Tables

| 2.1 | Maximum per-DIMM Optane performance per generation | 14  |

|-----|----------------------------------------------------|-----|

|     | Evaluated servers                                  |     |

| 5.1 | Feature set of existing SPEs                       | 87  |

| 6.1 | Price-performance of PMem and DRAM                 | 103 |

## 1.1 Motivation

For decades, data management systems were designed with a divide between data in main memory and data on secondary storage. While storage devices, such as HDDs and SSDs, have significantly lower access performance than DRAM, they are necessary to provide durability. Thus, systems that offer data persistence face a performance drop when durably writing data to storage and when retrieving it back for processing. In addition to providing durability, storage devices are significantly cheaper per GB than memory and offer much higher capacity. For economical reasons, systems often choose to reduce the amount of required DRAM and limit its use to processing and intermediate results, while the majority of the actual data is stored on HDDs or SSDs. However, limited DRAM may entail access to secondary storage for large intermediate results or even for auxiliary structures such as indexes.

To mitigate the storage access performance drop, various research areas focus on designing efficient storage solutions for data management systems. Such research areas are buffer management [34, 119], persistent indexes [11], and storage engines [35, 38]. For the majority of these, key design goals are to reduce storage access in the first place and to leverage efficient access patterns to storage whenever possible. Due to the high importance of these systems, they are continuously adapted to new hardware characteristics [89, 92].

After decades of established DRAM and storage database components, the announcement and arrival of large-scale persistent memory (PMem) technology in the form of Intel Optane [69] led to a rethinking of how persistence is achieved in data management systems. With byte-addressability and performance like DRAM as well as persistence like secondary storage, PMem as a new technology has the potential to cause a major performance shift in database storage and systems. In traditional designs, byte-addressable data is used for fast random access but is generally considered volatile, while persistent data layouts are optimized for slower storage, i.e., page-sized and/or sequential access. PMem blurs these lines, as it achieves fast random access on persistent data, removing the need for a clear distinction between memory and storage.

In Figure 1.1, we show how PMem fits between DRAM and SSDs in the classical

Figure 1.1: PMem sits between SSDs and DRAM in the storage hierarchy.

storage hierarchy. We present this based on four factors, *capacity*, *cost* (*GB/\$*), *latency*, and *bandwidth*. Due to its characteristics, PMem fits between SSDs and DRAM, both in anticipated performance before the commercial availability of Optane [123, 129] and with the actual performance of Optane [147].

With capacities of 128–512 GB per DIMM, Optane has a higher capacity than DRAM, which is currently available in  $\sim$  8–64 GB per DIMM. SSDs, on the other hand, are available with multiple TB per device. Based on these capacities, SSDs offer more GB/\$ than PMem [19], which in turn offers more GB/\$ than DRAM [15]. Modern SSDs are in the order of tens of cents per GB, Optane is in the order of dollars per GB, and DRAM ranges from dollars to low tens of dollars per GB.

With random access latency in the order of hundreds of nanoseconds, PMem's latency is very close to DRAM's [147], compared to tens or hundreds of microseconds latency to SSD [49]. The bandwidth of a single PMem DIMM is currently similar to that of modern NVMe SSDs, i.e., in the low GB/s [19]. Thus, PMem has more potential for latency-critical applications than for bandwidth-heavy ones.

Even before PMem was publicly available, the promise of these characteristics sparked research into how index structures [58, 123, 148], storage engines [6, 145], and buffer managers [129] can be redesigned for PMem. With the public availability of real PMem in the form of Optane, research in these areas shifted to Optane-specific designs [26, 91, 97, 155]. These systems raised the question of how to integrate PMem into data management systems and they led to an initial understanding of multi-tier memory in these systems. In this thesis, we address many remaining open questions on how to best design data management systems to fully leverage large-scale PMem as a new technology.

As Optane is currently the only instance of large-scale PMem and it was discontinued by Intel in 2022 [2], the technology's future is currently unclear. Two key aspects that influence the use of PMem are the underlying technology and the way this is connected to the CPU. On the technology side, various other PMem designs have been announced in the past decade [10, 48, 86, 100, 127, 154], but none of them are available yet. Intel's choice to discontinue Optane is mainly driven by economic factors [41], so a new technology with different properties might change the economics of PMem, making it more viable. On the connection side, Compute Express Link (CXL) is an emerging interconnect protocol that allows arbitrary memory to be attached to the CPU via PCIe instead of memory channels. With different types of memory on one server, and potentially even alternative PMem technologies, multi-tier memory setups face similar challenges as with a two-tiered DRAM/PMem setup. CXL may also alter the economics of PMem, as it does not require a high-end Intel CPU to use PMem. Regardless of the exact development of PMem, future technology will likely disrupt the classical storage hierarchy similarly to Optane. With each such technology, an open question remains how to integrate it best. While this thesis mainly covers various challenges around the integration of PMem, we also provide insights into challenges and opportunities for future multi-tier memory setups based on our learnings from PMem.

Driven by the promising results of pre-Optane designs and the potential impact that PMem has on database systems, in this thesis we explore the use of PMem in data management systems. We do this along four goals, starting with understanding its performance, over designing database components for PMem and their integration into larger systems, to transferring PMem insights to future research on multi-tier memory. We outline these four motivational challenges in the following.

Challenge 1: Understanding PMem performance. Before PMem became commercially available, research assumed a performance range that PMem may cover, i.e., experiments were often conducted in simulators that supported varying access latency [123, 148]. This led to a wide range of inconsistent performance numbers. With the arrival of Intel Optane, research shifted towards understanding the "actual" performance of PMem [47, 138, 147]. Based on these findings, designs specifically targeted towards Optane emerged, fully leveraging its intricacies and performance characteristics [26, 97, 101]. However, with limited hardware availability, different server configurations, and multiple hardware generations, it is not clear how consistently Optane performs in a wider range of setups. Because of this limited insight, it is also unclear whether the Optane-optimized designs generalize or if they are tailored only toward a single server.

Challenge 2: Designing PMem-aware storage systems. Key-value stores

#### **Chapter 1** Introduction

(KVSs) have become a foundation for state management in modern data-intensive applications and systems. Current designs are either based on secondary storage to offer persistence, e.g., in a storage layer [38], or are purely in-memory for fast access, e.g., for caching [128]. Regardless of the intended use, as a fundamental part of modern database stacks, the performance of KVSs is essential to the overall system performance. Due to their comparatively simple interface around put() and get() calls on individual records, most logic in a KVS is concerned with record access, i.e., storing and retrieving these records. Leveraging PMem and its characteristics has the potential to significantly improve this access and in turn, improve the performance of all systems building on such a PMem-aware KVS. Early work in this space shows that PMem shifts the performance from traditional KVSs based on slow secondary storage towards faster but volatile in-memory KVS, while still offering persistence [26, 91]. However, it is unclear how to best design such a PMem-aware KVS, especially concerning fundamental memory access patterns and the interaction between faster but limited DRAM and slower but ample PMem.

Challenge 3: Integrating PMem components into larger systems. While it is important to research and develop standalone database components for PMem, simply drop-in replacing these into existing systems does not necessarily yield the best results [19, 81]. It is important to understand the limitations of current systems to fully leverage PMem's potential by using it in the right places. In recent years, stream processing engines (SPEs), such as Apache Flink [21] or Spark Streaming [150], have become widely used in industry for low-latency processing of large data volumes. As SPEs commonly have high ingestion rates, they put a lot of pressure on the underlying storage system, making the potential performance gains from PMem-aware storage engines very high. Due to a wide range of SPE designs and goals, it is unclear which design choices must be made to integrate novel PMem storage engines and which performance can be achieved with the bandwidth and low latency that PMem promises.

Challenge 4: Implications of PMem research on multi-tier memory. Besides PMem, other approaches to and designs for multi-tier memory exist. The Compute Express Link (CXL) [30] interconnect is one of these approaches, which offers byte-addressability to and from arbitrary memory and storage via a PCIebased protocol. After Optane was discontinued by Intel in 2022 in favor of CXL [41], it is yet unclear which insights gained from PMem research can be transferred to future multi-tier memory setups as given with CXL.

## 1.2 Research Contribution

In this section, we present this thesis' research question and briefly outline our contribution to each of the individual goals on the path to answering this question. Combining all four motivational challenges described above (*Challenge 1–4*), in this thesis we discuss the following research question:

With the emergence of a fundamentally different memory technology in the form of persistent memory, how do data management systems need to be designed to leverage its unique properties for efficient state management and how can we extend these insights to future disruptive memory technologies?

To answer this question, we make the following contributions. Before analyzing PMem performance or designing novel systems, we provide an overview of PMem terminology and concepts in general and specifically for Optane (Chapter 2).

Contribution 1: Understanding PMem performance. In Chapter 3, we evaluate the performance characteristics of Optane PMem to answer the questions outlined in *Challenge 1*. We propose PerMA-Bench, a configurable benchmark framework that allows users to evaluate the bandwidth, latency, and operations per second for customizable database-related PMem access. Based on PerMA-Bench, we perform an extensive evaluation of PMem performance across four different server configurations, containing both first- and second-generation Optane, with additional parameters such as DIMM power budget and number of DIMMs per server. We validate our results with existing systems and show the impact of low-level design choices. We discuss our findings and identify eight general and implementation-specific aspects that influence PMem performance and should be considered in future work to improve PMem-aware designs. The content of Chapter 3 was published in PVLDB 15(11), 2022 [15].

Contribution 2: Designing PMem-aware storage systems. In Chapter 4, we investigate how to design a PMem-aware storage system in the form of a KVS, as motivated in *Challenge 2* above. We propose three PMem-specific access patterns and implement them in a hybrid PMem-DRAM KVS called Viper. We employ a DRAM-based hash index and a PMem-aware storage layout to utilize the random write speed of DRAM and the efficient sequential write performance of PMem. Our evaluation shows that Viper significantly outperforms existing KVSs for core KVS operations while providing full data persistence. The content of Chapter 4 was published in PVLDB 14(9), 2021 [14].

Contribution 3: Integrating PMem components into larger systems. In Chapter 5, we discuss open challenges and design goals for future SPEs that incor-

#### **Chapter 1** Introduction

porate fast PMem storage to overcome these challenges, as outlined in *Challenge 3*. To this end, we present Darwin, a novel SPE prototype that tailors its execution toward the target environment through adaptive storage backends and query compilation. Due to high ingestion rates, a key challenge in SPEs is the management of large state. The efficiency of inserting, retrieving, and checkpointing data heavily impacts the overall performance of SPEs. By integrating a PMem-aware state store, Darwin's adaptive execution leverages PMem's high performance while supporting larger-than-memory state as with traditional storage-based SPE state backends. Our early results show that this combination achieves an order of magnitude speed-up over current scale-out systems and matches processing rates of scale-up systems. The content of Chapter 5 was published at CIDR 2022 [16].

Contribution 4: Implications of PMem research on multi-tier memory. In Chapter 6, we give an outlook on how PMem research can be transferred to future multi-tier memory setups by the example of CXL (outlined in *Challenge 4*). We discuss how limited hardware availability impacts the performance generalization of new designs, how existing CPU components are not adapted towards different access characteristics, how multi-tier memory setups offer different price-performance trade-offs, and when explicit memory fences may still be needed. To support future CXL research in each of these areas, we discuss how our insights apply to CXL and which problems researchers may encounter along the way. The content of Chapter 6 was published at the NoDMC workshop 2023 [17].

# 1.3 Technical Contributions and Impact

Throughout our research towards this thesis, our contributions (Chapters 3 through Chapter 6) were published.

**Journal Papers**. Two chapters of this thesis (Chapter 3 and Chapter 4) were published in a top-tier journal.

- » Lawrence Benson, Leon Papke, Tilmann Rabl. PerMA-Bench: Benchmarking Persistent Memory Access. PVLDB, 15(11): 2463–2476, 2022.

In this publication, the author performed the conceptual work, as well as the majority of the implementation, analysis, and writing. Leon Papke assisted with the implementation and writing. Tilmann Rabl guided the conceptual work as the supervisor and aided with writing.

- » Lawrence Benson, Hendrik Makait, Tilmann Rabl. Viper: An Efficient Hybrid PMem-DRAM Key-Value Store. PVLDB, 14(9): 1544–1556, 2021.

In this publication, the author performed the conceptual work, as well as the majority of the implementation, analysis, and writing. Hendrik Makait assisted with the implementation. Tilmann Rabl guided the conceptual work as the supervisor and aided with writing.

**Conference Papers.** Two chapters (Chapter 5 and Chapter 6) were published in top-tier international and national conferences.

- » Lawrence Benson, Tilmann Rabl. Darwin: Scale-In Stream Processing. In Conference on Innovative Data Systems Research (CIDR), 2022.

In this publication, the author performed the conceptual work, the implementation, analysis, and the majority of the writing. Tilmann Rabl guided the conceptual work as the supervisor and aided with writing.

- » Lawrence Benson, Marcel Weisgut, Tilmann Rabl. What We Can Learn from Persistent Memory for CXL. In Datenbanksysteme für Business, Technologie und Web (BTW), 2023.

In this publication, the author performed the conceptual work, the analysis, and the majority of the writing. Marcel Weisgut assisted with the conceptual CXL parts as well as with writing. Tilmann Rabl guided the conceptual work as the supervisor and aided with writing.

**Open Source Contributions.** To allow for reproducibility and comparison, we have made the code of PerMA-Bench and Viper available. We also contributed patches to existing large open-source projects.

- » PerMA-Bench Code: github.com/hpides/perma-bench This repository contains the source code and results for our benchmarking framework PerMA-Bench (Chaper 3). Made available under MIT License. The PerMA-Bench code is used as the foundation of an ongoing benchmarking project by other members of the author's research group.

- » Viper Code: github.com/hpides/viper This repository contains the source code and results for our PMem-ware key-value store Viper (Chapter 4). Made available under MIT License. Based on our available code, Viper has been used as an evaluation baseline in various papers succeeding our work (e.g. [54, 140, 142]).

- » Added a NUMA feature to Intel's Persistent Memory Development Kit (PMDK). Pull Request: github.com/pmem/pmdk/pull/5067

» Submitted multiple patches to the LLVM compiler for more efficient vector instruction selection.

Commits: github.com/llvm/llvm-project/commits?author=lawben&since= 2023-01-01

## 1.4 Additional Contributions

In this section, we list additional publications that were made during the course of this thesis, but which are not part of it.

**First Authorship.** The author also explored SIMD vectorization in databases leveraging compilers' internal vector representations.

» Lawrence Benson, Richard Ebeling, Tilmann Rabl. Evaluating SIMD Compiler-Intrinsics for Database Systems. In Workshop on Accelerating Analytics and Data Management Systems (ADMS), 2023.

Source code: github.com/hpides/autovec-db

**Student Supervision.** During his PhD at HPI, the author supervised and worked with various students, which led to four publications at top-tier conferences and journals (in chronological order).

» Björn Daase, Lars Jonas Bollmeier, *Lawrence Benson*, Tilmann Rabl. Maximizing Persistent Memory Bandwidth Utilization for OLAP Workloads. In Proceedings of the International Conference on Management of Data (SIGMOD), 2021.

Source code: github.com/hpides/pmem-olap

- » Maximilian Böther, Otto Kißig, Lawrence Benson, Tilmann Rabl. Drop It In Like It's Hot: An Analysis of Persistent Memory as a Drop-in Replacement for NVMe SSDs. In Proceedings of the International Workshop on Data Management on New Hardware (DaMoN), 2021.

- Source code: github.com/hpides/pmem-nvme-dropin

- » Tobias Maltenberger, Till Lehmann, *Lawrence Benson*, Tilmann Rabl. Evaluating In-Memory Hash Joins on Persistent Memory. In Proceedings of the International Conference on Extending Database Technology (EDBT), 2022.

- » Maximilian Böther, Lawrence Benson, Ana Klimovic, Tilmann Rabl. Analyzing Vectorized Hash Tables Across CPU Architectures. PVLDB, 16(11): 2755 -2768, 2023.

Source code: github.com/hpides/vectorized-hash-tables

**Co-Authorship.** The author also co-authored the following paper:

» Wang Yue, Lawrence Benson, Tilmann Rabl. Desis: Efficient Window Aggregation in Decentralized Networks. In Proceedings of the International Conference on Extending Database Technology (EDBT), 2023.

Source code: github.com/wywclmqf/DESengine

## 1.5 Thesis Outline

The remainder of this thesis is structured as follows.

In **Chapter 2**, we introduce persistent memory as the key memory technology on which our contributions are based.

In **Chapter 3**, we present PerMA-Bench, a configurable benchmark framework to analyze bandwidth, latency, and operations per second for customizable database-related PMem access. Based on PerMA-Bench, we evaluate synthetic workloads and real systems on various PMem server configurations and perform a price-performance evaluation.

In **Chapter 4**, we introduce Viper, a hybrid PMem-DRAM key-value store designed for Optane. Based on access pattern microbenchmarks, we propose three key design choices for building a hybrid key-value store and show how they are implemented in Viper. We show that our design outperforms existing solutions at the time.

In **Chapter 5**, we discuss current challenges around high-performance stream processing systems. We outline how efficient state management, as a key challenge, can be improved using our PMem-aware state store Viper in our streaming engine prototype Darwin.

In **Chapter 6**, we discuss how our findings and insights from PMem research can be transferred to Compute Express Link. We do this in light of Intel discontinuing the Optane product line in favor of the emerging CXL interconnect.

In **Chapter 7**, we summarize this thesis and provide an outlook on how our work contributes to future research in this area.

This chapter is an extended version of content published in [14, 15].

# 2.1 Persistent Memory

In this chapter, we present the necessary background on persistent memory as the core technology used throughout this thesis. We cover various aspects of PMem in general and related to Intel's Optane PMem product line. We first discuss general PMem classification types (Section 2.1.1), followed by details specific to Intel's Optane product (Section 2.1.2). Then, we discuss how data is transferred between the CPU and PMem in two different API modes (Section 2.1.3) and how to ensure atomic writes and durability (Section 2.1.4). In Section 2.1.5, we present programming interfaces and APIs for PMem.

# 2.1.1 **Types**

The Storage Networking Industry Association (SNIA) defines persistent memory as a "storage technology with performance characteristics suitable for a load and store programming model" [134], i.e., as a technology that is *persistent* but can be used like regular *memory*. In this thesis, we use the term persistent memory or PMem to describe this technology, but over the years various other names have emerged. These are, e.g., non-volatile memory (NVM), storage-class memory (SCM), and non-volatile RAM (NVRAM). Alternative abbreviations for PMem include PMEM, PM, or PMM. For consistency, we use only PMem.

Large-scale persistent memory is currently based on one of two designs: 3D XPoint (NVDIMM-P) or DRAM + flash (NVDIMM-N). 3D XPoint, developed by Intel and Micron, is the underlying technology of Optane [60]. It is the only publicly available *true* PMem, in which a single storage medium allows for both byte-addressability and persistence. DRAM + flash storage designs are employed in PMem offered by, e.g., HPE [36]. These battery-backed NVDIMM-Ns flush their state to flash chips on power failure.

According to the JEDEC standards, NVDIMM-Ns are seen as regular DRAM by the server while NVDIMM-Ps are viewed as separate storage with additional changes

Figure 2.1: Six interleaved Optane DIMMs span a continuous 24 KiB region.

to the DDR4 protocol [72, 73]. Future PMem technology is expected to follow the NVDIMM-P standard, as this allows for larger capacity and extended functionality, while NVDIMM-Ns are limited by DRAM [74]. Currently, Optane PMem is the only available NVDIMM-P implementation. Various other PMem designs have been announced or are actively developed. These include Nano-RAM [100], phase change memory [86, 127, 154], resistive RAM [10], and magnetoresistive RAM [48].

While NVDIMM-Ns have been available for many years, they have not achieved widespread adoption. On the other hand, Optane, as a new technology, has received a lot of attention in academia and achieved initial adoption in industry, e.g., in SAP HANA [53]. As NVDIMM-Ns are essentially DRAM and have DRAM performance, we focus on NVDIMM-Ps in the form of Optane in this thesis.

# 2.1.2 Intel Optane

Intel Optane is currently the only commercially available NVDIMM-P implementation. It is based on Intel's 3D-XPoint media. While parts of the description in this section apply to all NVDIMM-P-compliant technology, certain aspects are Optane-specific. In this section, we cover some details of Optane that are not specified for NVDIMM-Ps and may be different in other implementations.

#### Interleaving

When installing Optane PMem in a server, users can choose between an *interleaved* and *non-interleaved* setup. With interleaving, data is striped across all available DIMMs, as shown in Figure 2.1. This setup is similar to RAID 0 for secondary storage. One stripe is 4 KiB, so in a common setup with six DIMMs, a continuous

24 KiB chunk of data is spread across all six DIMMs. With this layout, users get transparent parallelism due to a uniform distribution of data across DIMMs.

Without interleaving, each DIMM covers the continuous memory region given by its capacity. In this case, the application must handle parallelism for continuous access, as it is served from a only single DIMM. This layout is beneficial if the application on top explicitly handles data placement, as it gives developers full control over data locations.

#### **Access Modes**

Optane, in combination with Intel Xeon CPUs, offers two modes to run in, *Memory Mode* and *App Direct Mode*. In Memory Mode, PMem acts as a large volatile memory extension to regular DRAM. In this mode, memory is split into *near* and *far* memory, where near memory is DRAM and far memory is PMem. Users have no control over where memory is written to or accessed from, as this is handled by the OS. The OS treats DRAM as an "L4" cache, to which it first writes all data. Only when DRAM is full, does it write to PMem. As DRAM acts as a cache in front of PMem, the total memory capacity of the system is that of all PMem DIMMs without DRAM. For example, a system with 768 GB PMem and 96 GB DRAM has a total memory capacity of 768 GB and not 864 GB.

A key advantage of this mode is that legacy applications can use it without any code modification, as all memory is exposed as DRAM with a higher capacity. However, persistence is not guaranteed in this mode, i.e., users must treat all memory as volatile. Additionally, as DRAM acts as a cache, an L3 cache miss first results in an "L4" lookup to DRAM, which in turn leads to a PMem lookup on a miss. This increases latency by an additional DRAM access compared to direct access to PMem.

In App Direct Mode, memory is split into two explicit regions over which the developer has full control. The key advantage of this mode is that persistence is guaranteed if used correctly. However, existing applications must be adapted to explicitly access PMem. As memory is split into two regions, the system's capacity is combined, i.e., to 864 GB in the example above. As this mode offers more control as well as persistence, we focus on it in this thesis. The remainder of this section assumes that we run PMem in App Direct Mode.

#### **Access Granularity**

The internal physical media access size of Optane is 256 bytes. Conceptually, this is similar to a block device with a, e.g., 4 KiB page size. It is possible to load and

|       | 100 Series | 200 Series | 300 Series |

|-------|------------|------------|------------|

| read  | 1.75 GB/s  | 2.03 GB/s  | 5.28 GB/s  |

| write | 0.58 GB/s  | 0.79 GB/s  | 1.63 GB/s  |

**Table 2.1:** Maximum per-DIMM Optane performance per generation for random 64-byte reads and writes, as reported by Intel.

store individual 64-byte cache lines but this results in read and write amplification in the Optane DIMM. Most systems designed for Optane optimize for this 256-byte granularity, as access at this size yields the best performance. To mitigate write amplification, Optane employs a write combining buffer that tries to combine four adjacent 64-byte cache lines into a single 256-byte write.

#### **Optane Generations**

The Optane PMem product is available in three generations, the 100 Series (code name Apache Pass), the 200 Series (Barlow Pass), and the 300 Series (Crow Pass). All generations offer DIMMs with 128, 256, and 512 GB capacity. Each generation requires a new corresponding Intel Xeon CPU generation, i.e., the 100 Series requires at least a 2<sup>nd</sup> generation Xeon CPU (Cascade Lake), the 200 Series requires a 3<sup>rd</sup> generation Xeon CPU (Ice Lake), and the 300 Series requires a 4<sup>th</sup> generation Xeon CPU (Sapphire Rapids). Key differences between generations are that the 200 Series comes with eADR support (see Section 2.1.4) compared to ADR in the 100 Series and that the 300 Series supports Compute Express Link (CXL) 1.1.

As the Optane generations are tied to CPU generations, the maximum PMem capacity per generation is also tied to the CPU. With Cascade Lake, a single CPU has six memory channels, supporting a maximum of  $6 \times 512$  GB = 3072 GB. Ice Lake and Sapphire Rapids CPUs have eight channels, allowing for a total of 4096 GB per socket.

As Optane and DRAM share the same memory bus, the bus speed must be set equally. Optane is only supported in a 2 DPC (DIMM per channel) setup with one DRAM DIMM per Optane DIMM. Using Optane slightly decreases the maximum bus speed from a DRAM-only 1 DPC setup. For 100 Series Optane and Cascade Lake, 2 DPC is limited to 2666 MT/s [60, 64], compared to 2933 MT/s for a DRAM-only 1 DPC configuration. For 200 Series Optane and Ice Lake CPUs, the limit is 3200 MT/s for both 1 and 2 DPC [61, 65]. The third Optane generation and Sapphire Rapids CPUs support up to 4400 MT/s [66, 67] for 2 DPC, which is lower than Sapphire Rapid's 4800 MT/s limit for 1 DPC.

We perform an extensive evaluation of 100 and 200 Series Optane in Chapter 3, but this does not include the recent 300 Series. To provide a small performance overview, we show the 64-byte random access performance per DIMM as reported by Intel [60, 61, 66] in Table 2.1. In it, we see that each new generation brings a performance boost, especially from the 200 to 300 Series. Nominally, a common 100 Series setup with six Optane DIMMs supports  $6 \times 1.75$  GB/s = 10.5 GB/s random reads and 3.48 GB/s random writes. A 200 Series setup with eight DIMMs can achieve up to  $8 \times 2.03$  GB/s = 16.24 GB/s random reads and 6.32 GB/s random writes and a 300 Series setup can achieve up to  $8 \times 5.28$  GB/s = 42.24 GB/s random reads and 13.04 GB/s random writes. Due to Intel discontinuing Optane, we were not able to verify these numbers for the 300 Series. For the 100 and 200 Series, the performance aligns with our results as shown in Chapter 3.

## Optane in the Storage Hierarchy

To position Optane in the storage hierarchy, we briefly compare it to DRAM and SSDs. Due to widely different performance characteristics across devices, memory/storage technologies, and generations of the same technology, we provide only a rough performance outline of Optane in the "storage jungle" [56]. A single DDR-5 DRAM DIMM with 4800 MT/s achieves ~38 GB/s read bandwidth, which is 7× higher than the Optane 300 Series. Depending on the generation, a single Optane DIMM achieves comparable bandwidth to modern NVMe SSDs, which can read and write between 2 and 7 GB/s per device (with 4 KB page granularity). As multiple Optane DIMMs are commonly installed together, the accumulated bandwidth exceeds a single NVMe SSD. However, recent work shows that multiple NVMe SSDs combined in a RAID also achieve more than 50 GB/s, which is similar to a fully-stocked Optane server [50]. While the bandwidth is similar between Optane and modern NVMe SSDs, a key difference is access latency. Random PMem access is in the order of hundreds of nanoseconds, while SSDs require tens or hundreds of microseconds, i.e., one order of magnitude difference [50]. Thus, the potential of Optane over SSDs is greatest when used for workloads requiring low latency.

# 2.1.3 Accessing Persistent Memory

The Storage Networking Industry Association (SNIA) defines an NVM Programming Model (NPM) [134], which specifies a unified access model for PMem. This model allows for the integration of a wide range of storage technologies, beyond only Intel's Optane product. We show the two PMem access modes of this model in Figure 2.2. Applications either access PMem via regular filesystem interfaces (shown

Figure 2.2: Standard PMem access modes.

on the left side) using calls such as fopen, fread, fsync, or they access PMem via memory-mapping (shown on the right side) using calls such as mmap, and load and store instructions.

The filesystem interface allows existing applications to use PMem as a drop-in replacement for common disk-based interaction, while the second mode allows applications to use PMem identically to DRAM. The programming model allows for memory mapping of files, i.e., combining both modes. In this case, files are used to logically structure raw memory chunks but PMem is accessed directly without the overhead of regular file I/O.

#### File I/O

To use PMem as a drop-in replacement for secondary storage, users can access it via a regular filesystem. In this case, PMem is exposed as a block device, and a filesystem, e.g., ext4 or xfs, is created on top of it. From a user's perspective, this is identical to a regular disk-based filesystem.

Regular file I/O commonly goes through the operating system's page cache, i.e., a copy of the storage content is kept in DRAM for faster access and modification. Due to PMem's byte-addressability, this copy is not necessary but it consumes DRAM capacity. To avoid this copy, PMem-aware filesystems offer *direct access* (DAX). In a DAX filesystem, data is read directly from the PMem DIMM and modifications are written directly to it without an intermediate copy. However, due to the block-device characteristics, all access occurs at page granularity, i.e., 4 KiB. This does not leverage the byte-addressability of PMem and causes high read and write amplification for small reads and writes. To better utilize PMem bandwidth, the preferred access mode is via memory mapping and load/store semantics, which we cover in the following.

In previous work, we show that access via the filesystem has a 5–10% overhead compared to direct memory access to and from a character device due to memory zeroing on page faults [31]. Directly mapping memory from the character device

**Figure 2.3:** Writing to NVDIMM-Ps from the CPU.

avoids this overhead but access to the raw device requires full control of it without the advantages of a filesystem, e.g., structuring data or fine-grained access control.

#### Load/Store

To leverage the byte-addressability of PMem, developers can memory-map PMem directly from the PMem DIMM into their application's virtual address space. To do this, they issue an mmap call to the PMem-aware DAX filesystem or the PMem character device directly. Due to DAX, every byte that is accessed in the memory-mapped virtual address range is read and written directly from and to PMem via regular CPU load and store instructions, allowing for access at cache line granularity. This enables developers to create complex data structures in PMem as in DRAM.

For data modifications in DRAM, in most cases, it is not important when and how data is actually moved from the CPU to memory, as an application crash or power loss results in all data being lost. To ensure persistence with PMem, modified data in the CPU's current cache line must be explicitly written back (or flushed) to PMem, as data in the caches is not necessarily persisted. We outline how data is moved from the CPU to PMem in Figure 2.3. This model is based on Intel's Xeon processors [62] and Optane.

A CPU contains one or more *integrated memory controllers* (iMCs), which are directly connected to PMem via memory channels. To write data to PMem, the CPU must flush cache lines to a *write pending queue* (WPQ) within an iMC. Once data is in the WPQ, it is in the *Asynchronous DRAM Refresh* (ADR) Domain, which is guaranteed to be persisted, even on power loss. The WPQ then issues the write to the correct PMem device. On Intel CPUs, available instructions to flush a cache line are:

» clflush (cache line flush): Flushes the cache line and invalidates it, i.e., the next access to this cache line must fetch data from PMem. This is mainly a

legacy instruction that should not be used. Instead, developers should use clwb. clflush can be called via, e.g., \_mm\_clflush(addr).

- » clwb (cache line write back): Flushes the cache line but does not invalidate it, i.e., data is written to PMem but it still remains valid in the cache hierarchy. The next access to this cache line can be answered from cache if it was not evicted otherwise in the meantime. This is the recommended instruction to write data to PMem. clwb can be called via, e.g., \_mm\_clwb(addr).

- » ntstore (non-temporal store): For data with low or no temporal locality, i.e., it will not be accessed in the near future, Intel also offers a non-temporal store. This completely bypasses the cache hierarchy, offering better performance than the other instructions, which perform additional cache-related operations. This instruction is useful, e.g., for large sequential writes or logging. A non-temporal store can be issued via, e.g., \_mm512\_stream\_si512(destination, data).

A read request to PMem is posted to a read pending queue (RPQ) at cache line granularity. Following a request, data is also returned from the DIMM at cache line granularity, irrespective of the underlying physical granularity, e.g., 256-byte for Optane. While WPQs and RPQs are Intel-specific, they are based on the NVDIMM-P standard that describes a write buffering mechanism. Future PMem is likely to work similarly.

Communication via the DRAM memory bus (DDR) is synchronous [75]. This is not the case for a shared DRAM and PMem memory bus, as PMem is slower than DRAM. To overcome the varying latency in Optane, Intel uses a modified DDR4 protocol called DDR-T to support asynchronous communication between the WPQ and Optane. While DRR-T is Optane-specific, synchronous memory buses are a general problem that vendors need to solve when supporting different memory types. Compute Express Link (CXL) is emerging as an industry-wide solution to handle larger memory capacity with slower access [30]. We discuss the implications of PMem research for future CXL-aware designs in Chapter 6.

# 2.1.4 Atomicity and Durability

An important distinction between memory-mapped files on disk and PMem is that traditionally data is copied to a page cache in DRAM, which is then modified and flushed back. When memory mapping PMem, it is accessed directly (via DAX) and not copied to a DRAM page cache. Any modification to the data, if flushed correctly, is directly performed in *persistent* memory. This changes the failure granularity of

data modification compared to file-backed memory. For traditional files, developers must consider various failure cases, such as torn writes, but at the granularity of, e.g., a 4 KiB page write at an explicit point in the application. For PMem, developers must explicitly control data persistence and handle low-level crash consistency for *every* write to PMem.

As data in the caches is not persisted, developers must issue explicit flush instructions (see Section 2.1.3). However, in addition to explicit flushes, data might be randomly evicted from the cache, resulting in unexpected data persistence. Even if the developer does not issue an explicit flush, some data modifications might be written to PMem. As current CPUs provide only 8-byte atomic writes, random 64-byte cache line evictions may cause an inconsistent state after a crash for modifications larger than 8 byte. Thus, programmers must carefully design fine-grained PMem data access to ensure application correctness.

Additionally, programmers have to ensure correct store ordering. Modern compilers and CPUs may re-order instructions to improve performance, e.g., through better pipelining. However, this may lead to re-ordering of persist instructions, resulting in correctness bugs [99]. We show an example of this in the code below.

```

void insert_item(vector& vec, int x) {

vec[vec.size] = x;

// Flush cache line to PMem

_mm_clwb(&vec[vec.size]);

vec.size++;

}

```

In his example, we append an integer to a vector and then increase the current size of the vector. Depending on the compiler, this may first store a copy of the size in a register r, update the vector's size, then write x to the position stored in r, and finally flush it. For data in DRAM, this execution order makes no difference to the user as all data is lost after a crash. For data in PMem, this order may not be correct. Due to out-of-order execution in the CPU, the change to the size may be observed by later instructions, which then assume that data has been written and, e.g., report a successful operation to the user. However, if the application crashes before x was actually flushed to PMem, the execution was not successful. When restarting after the crash, x cannot be recovered and the application is in an inconsistent state.

To avoid such reordering, programmers must explicitly issue memory fences, e.g., via an sfence instruction on x86 [63]. This ensures that all modifications issued before the fence are globally visible before later modifications become visible, i.e., they can be observed by other threads. A common pattern when programming for

#### Chapter 2 Background

PMem is to *i*) perform the data modification, *ii*) flush it, and *iii*) perform a *store fence* to ensure that no later instruction is executed before the flush is completed. After the store fence, *iv*) metadata is updated to indicate the modification's validity. In our example, this would be done as shown below.

Correctly moving data from CPU caches to PMem burdens programmers due to these correctness issues. It also incurs performance penalties due to additional CPU instructions. However, solutions exist to mitigate the correctness issues and performance penalties. Intel's 3<sup>rd</sup> Generation Xeon processors (Ice Lake) introduce an *enhanced* ADR (eADR) [61]. This includes all caches in the ADR, i.e., ensuring the persistence of all cached data in case of power loss (see Figure 2.3). This new design removes the necessity of explicit flushing. However, it still requires store fences for correct ordering and data can still be randomly and/or partially evicted, requiring careful data structure designs. A recent study finds that missing flushes are a common mistake in various PMem applications and libraries [116]. An eADR protects the user from this class of bugs.

# 2.1.5 Programming Interfaces and APIs

As PMem is commonly mapped into the application's virtual address space, developers can interact with it the same way they interact with DRAM. However, we show that they must pay attention to flushing, store ordering via fences, and crash consistency to write correct applications. This complexity results in numerous bugs that are hard to detect [116]. To aid developers with PMem programming, various PMem libraries have been created under the Persistent Memory Development Kit<sup>1</sup> (PMDK) [124]. These contain, among others, general purpose utilities for persistent memory development (libpmem<sup>2</sup>), transactional objects and memory allocations

- 1 Due to Intel discontinuing Optane, most projects in PMDK have been deprecated as of 2023.

- 2 https://pmem.io/pmdk/libpmem/

(libpmemobj<sup>3</sup>), C++ bindings (libpmemobj-cpp<sup>4</sup>), or logging utilities (libpmemlog<sup>5</sup>). To have more explicit control over PMem access, we do not rely on PMDK libraries in this thesis.

<sup>3</sup> https://pmem.io/pmdk/libpmemobj/

<sup>4</sup> https://pmem.io/libpmemobj-cpp/

<sup>5</sup> https://pmem.io/pmdk/libpmemlog/

# Benchmarking Persistent Memory Access

The majority of this chapter has been published in [15].

#### 3.1 Introduction

Both research and industry have awaited the arrival of persistent memory (PMem) as a new layer in the storage hierarchy for many years. PMem promises byte-addressability and persistency at DRAM-like speed with SSD-like capacity. These characteristics have the potential to cause a major performance increase in storage systems, such as databases and key-value stores. Thus, research on system design incorporating PMem was published long before real PMem hardware was available, based on simulations [7, 123, 141]. Now that byte-addressable, persistent memory is finally available commercially, Intel's Optane DC Persistent Memory has received a lot of attention in initial performance evaluations [31, 47, 130, 147]. These evaluations provide valuable insights into the general performance and unique characteristics of first-generation Optane.

Research on data structures [25, 97, 101] and storage systems [14, 26, 91] that incorporate these insights often have to perform additional hardware-specific micro benchmarks to understand the specific nuanced PMem behavior for their expected workloads. Initial research shows that Optane's performance is highly dependent on the workload with major differences between read and write behavior.

Due to limited availability and high prices, researchers often have access to only one PMem server. Thus, new systems built for PMem are designed, implemented, and optimized on a single server with a single combination of PMem, DRAM, and CPU. However, many factors impact PMem performance that are not yet well understood, e.g., the DIMMs' size and power budget or the number of DIMMs in the server. As PMem is a new technology, it is unclear how well these initial designs generalize across PMem configurations. On top of various configurations, with the availability of second-generation Optane, new performance characteristics are introduced.

Based on the configuration space and workload-tailored micro-benchmarks of previous work, we identify the need for a comparable workload-driven analysis of PMem. We propose PerMA-Bench, a configurable benchmark framework

that analyzes the bandwidth, latency, and operations per second for customizable database-related PMem access. In PerMA-Bench, we pre-define various workloads that cover the maximum achievable performance of core access patterns (sequential/random reads/writes), as well as a wide range of realistic, database-related access patterns, such as updates, lookups, and scans in tree and hash indexes. These complex patterns include pointer-chasing loads, mixed read/write access, and hybrid PMem/DRAM access. Additionally, PerMA-Bench allows users to run custom workloads tailored toward their design choices. With PerMA-Bench, we propose a tool that provides insight into the performance of PMem at a general and workload-specific level. Users can explore the performance of new access patterns but also validate existing designs. Based on these findings, users can validate their design choices without having to write their own benchmark application and find areas of improvement in existing designs.

Based on PerMA-Bench, we perform the first extensive evaluation of Optane for database workloads across various DIMM sizes of the first and second generation. We compare the performance of all three DIMM sizes of 100 Series Optane and one DIMM size of the 200 Series. Additionally, we show the impact of varying the number of DIMMs, DIMM power budgets, and memory bus speeds.

We validate our results with existing implementations and show that they do not fully utilize the performance improvements across Optane generations. We show that the choice of persist instruction has a high performance impact and that avoiding explicit flushes in eADR does not always yield the best results. Based on our results, we identify and discuss eight aspects that future work should take into account when designing PMem-aware systems. With the availability of more PMem hardware, research has to consider more than one setup to achieve general PMem-optimized designs.

In addition to PMem's performance, its price-performance is important to determine whether PMem is suitable for users' needs. In this chapter, we perform a price-performance comparison of various server configurations. Our comparison shows that PMem's price-performance is competitive with that of DRAM and is often even better. Thus, in addition to providing persistence, PMem can act as a larger, cost-effective general memory when used correctly. In summary, we make the following contributions:

- 1) We propose PerMA-Bench, a configurable benchmark framework to analyze bandwidth, latency, and operations per second for customizable database-related PMem access.

- 2) We perform an extensive evaluation of PMem performance across four PMem

servers and additional per-server configurations to show the impact of individual server setups on bandwidth utilization and latency.

- 3) We compare the price-performance for key workloads across all servers and show that while there are large differences across Optane, PMem is generally competitive with DRAM.

- 4) We discuss eight general and implementation-specific aspects that influence the performance of PMem and need to be taken into account for the design of future PMem-aware systems.

The remainder of the chapter is structured as follows. In Section 3.2, we introduce the PerMA-Bench framework. In Section 3.3, we present PerMA-Bench results on various hardware configurations, which we then use in Section 3.4 to discuss the price-performance of PMem. Finally, we discuss our findings (Section 3.5) and related work (Section 3.6), before concluding in Section 3.7.

# 3.2 Introducing PerMA-Bench

In this section, we introduce PerMA-Bench, a benchmark framework for persistent memory access. When designing new systems or database components, it is important to know the performance of the underlying memory access. This understanding allows users to tune their system towards better PMem utilization. PerMA-Bench supports *basic* and *complex* memory access patterns to evaluate the performance of PMem. Basic access patterns determine the maximum achievable bandwidth utilization and latency by repeatedly executing the same operation, i.e., a simple read or write. Complex patterns allow users to evaluate specific designs via chained read/write access from/to DRAM and PMem with varying persist instructions and access sizes. Based on these complex patterns, users can model, e.g., new index structure designs and gain insight into their memory performance before implementing them.

We present the runtime of PerMA-Bench in Section 3.2.1. Then, we present options for workload customization in Section 3.2.2 and briefly discuss supported memory store semantics in Section 3.2.3.

#### 3.2.1 Runtime

PerMA-Bench is designed as a standalone benchmark executable. Users interact with PerMA-Bench via configuration files and command line arguments. Based on

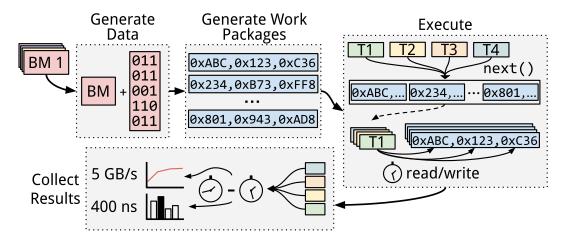

**Figure 3.1:** Execution cycle of a benchmark in PerMA-Bench.

these specified configuration parameters, individual benchmarks are created. We show the execution cycle of PerMA-Bench in Figure 3.1. For each benchmark (BM) that is created, PerMA-Bench performs four steps.

First, all data files are prepared and filled with random data. The files can be located in PMem or DRAM to allow for hybrid setups, which are common in current PMem research. Next, individual work packages are generated, which contain a pointer for each operation that is to be executed on the data. Work packages of, e.g., a random read benchmark with 100 operations contain 100 pointers to random offsets in the data file. For sequential access, packages contain 100 pointers to contiguous addresses. This allows for execution in a tight loop instead of requiring logic per benchmark type. For raw performance benchmarks, all work packages are pre-generated to avoid the overhead of generation during execution.

During the execution, N threads are spawned (N=4 in Figure 3.1). Each thread then continuously pulls a new work package from a shared queue and executes the requested operations on that work package. PerMA-Bench adopts this work package approach for two reasons. First, to avoid stragglers when statically assigning work to threads. During our evaluation, we observed that hyperthreading often leads to very unbalanced execution times, skewing the final results. Second, as the general concept of work-stealing is employed in many databases exactly to avoid execution skew, PerMA-Bench represents a common execution model where workers operate on small work packages, e.g., via morsels [88]. To avoid long-running packages and the skew this entails, work packages contain 64 MB worth of operations by default, which execute in less than 100 ms in most cases. All threads are synchronized via a barrier before the execution starts to ensure concurrent execution.

**Listing 3.1:** Example config YAML file.

```

1 hash_index_update:

2 matrix:

3   number_threads: [ 1, 4, 16 ]

4 args:

5   custom_ops: "r_256, w_64_cache_128, w_64_cache_-128"

6   total_memory_range: 10G

7   number_operations: 100000000

```

We find that results are not impacted by a warm-up phase within workloads, as they exceed cache and queue sizes. However, as pre-faulting pages before writing to them avoids kernel page zeroing during execution [68], we provide a "warm-up" pre-fault flag.

After all work packages have been processed, PerMA-Bench collects the results of all threads to calculate the final benchmark results. PerMA-Bench determines the total execution time as the time between all threads' earliest begin timestamp and latest end timestamp. This captures the entire execution duration but may underestimate the actual performance slightly, as some threads are already idle while others are finalizing their work. However, in PerMA-Bench, we perform workload-driven performance evaluation and from a higher-level perspective, this approach captures the total time it takes to complete a given workload. Based on the total number of processed bytes or operations and the total execution time, PerMA-Bench calculates the overall throughput in GB/s or operations/s. If specified by the user, PerMA-Bench also samples the latency of individual operations. The sampled values are added to a histogram and presented in the form of minimum, maximum, average, and multiple percentile latencies.

# 3.2.2 Custom Workloads and Configuration

Besides the pre-defined workloads, custom benchmarks can be configured via YAML files and command line arguments. In this section, we present configuration options provided by PerMA-Bench with which users can express their specific workloads' access patterns.

**Configuration Files.** Benchmarks in PerMA-Bench are configured via YAML files. This format allows users to specify workloads manually and programmatically. We show an example configuration in Listing 3.1. Each configuration file consists of two main parts, the matrix arguments and the general arguments. The matrix

block (Lines 2–3) describes which dimensions should be evaluated in the benchmark. Each matrix argument is provided as a list, from which PerMA-Bench creates a benchmark for each combination in the cross product, i.e., three benchmarks in this example. The args block (Lines 4–7) describes which general arguments should be used for every combination. In this example, we configure a hash index update workload and evaluate it for 1, 4, and 16 threads.

**Custom Operations.** In Line 5, we show the definition of a custom operation. These model complex, pointer-chasing memory access patterns instead of simple, independent reads or writes. They are created in a chain in which each operation op is responsible for calling the next operation op' once complete. When op has read the random data d, it passes d to op', which then determines the next address based on d. By requiring data from op in op', PerMA-Bench ensures that op' is not executed before op was completed.

In the example, PerMA-Bench reads 256 Byte ( $r_256$ ), e.g., a hash bucket, at a random location  $r_a$  within the allocated data range. Then, two 64 Byte *Cache* write instructions ( $w_64_cache$ ) are executed. The first is performed with an offset of 128 Byte ( $_128 = r_a + 128$ ), e.g., to store data in a hash bucket. The next write operation jumps back 128 Byte to the start of the bucket ( $_{-128} = r_a$ ) to update metadata. This pattern of storing data in a node and updating metadata afterwards is common in PMem data structures [14, 97, 101, 123]. As 64 Byte cache line flushes are combined to 256 Byte in Optane, it is important to model adjacent writes correctly instead of simulating them with writes to the same cache line while supporting different persist instructions. Varying these sizes also gives users insight into the impact of prefetching in PMem. Additionally, PerMA-Bench supports mixing DRAM and PMem for hybrid access, as used, e.g., in PMem B-Trees [25, 97, 123, 148].

**Benchmark Parameters.** PerMA-Bench currently offers 19 configuration parameters that allow users to define a wide range of individual benchmarks without having to write C++ code for each of them. Users can specify, e.g., PMem/DRAM memory ranges, access size, sequential/random execution, number of partitions and threads (for data parallelism), custom operations, work package size, runtime, and file pre-faulting.

**Other Features.** PerMA-Bench supports running different workloads as task-parallel benchmarks. Concurrent workloads might impact each other as one benefits from caching, while the other fills the cache with unwanted data. Users can also specify *NUMA-aware execution* of benchmarks on *far* or *near* CPUs to explore how data placement impacts their workloads and whether NUMA must be considered in their design. PerMA-Bench additionally allows users to run all benchmarks in DRAM as a performance reference.

#### 3.2.3 Persist Instructions

PerMA-Bench supports four persist instructions, *Cache*, *CacheInvalidate*, *NoCache*, and *None*. *Cache* represents a temporal store (clwb), *CacheInvalidate* represents a temporal store that invalidates the cache line (clflushopt), *NoCache* represents a non-temporal store (ntstore), and *None* performs no explicit flush instruction. Temporal refers to the inclusion of data in the cache hierarchy with the assumption of future access, i.e., temporal locality is likely. When temporal locality is unlikely, non-temporal instructions can bypass the cache completely, avoiding cache pollution. Not explicitly flushing is useful when persistence is not required, e.g., when storing intermediate results in PMem or when eADR ensures persistence. For *Cache, CacheInvalidate*, and *NoCache*, we add a store fence (sfence) afterwards to guarantee correct write ordering. PerMA-Bench uses Intel's AVX512 extension to write an entire cache line, i.e., 64 Byte or 512 Bits, in one instruction using SIMD-registers [63].

## 3.3 PerMA-Bench Results

In this section, we present the results of various PerMA-Bench workloads on multiple PMem server configurations. Our results give insight into both raw and workload-specific PMem performance to better understand PMem's use in database-inspired workloads. We evaluate various configurations to show how comparable previous results are across PMem setups, as they are often run on only one configuration, e.g., on one DIMM size or with a partially stocked server. These configurations allow us to draw more general conclusions about PMem as well as provide insight into how previously published systems and results apply to other setups.

We describe our evaluation servers in Section 3.3.1. We then show the bandwidth and latency results of PerMA-Bench's raw performance workloads in Section 3.3.2 and Section 3.3.3 to gain an understanding of the maximum performance of current PMem hardware. In Section 3.3.4, we discuss the results of database-related workloads and index structures to gain insight into the performance of PMem for more complex access patterns in actual systems and implementations. Finally, we investigate the impact of configurations affecting a single server in Section 3.3.5, i.e., by varying the number of DIMMs or the memory bus speed, as well as by disabling the prefetcher.

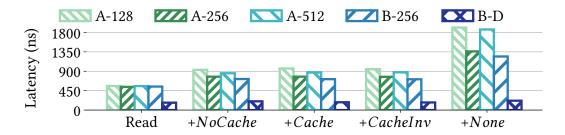

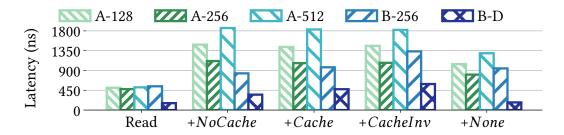

**Table 3.1:** Evaluated servers (single socket). Apache/Barlow refer to the code names of 100/200 Series Optane. All CPUs are Intel Xeon, all PMem is Optane.

| Name (Plot Label)             | CPU                                | PMem                                          | DRAM     | os                           |

|-------------------------------|------------------------------------|-----------------------------------------------|----------|------------------------------|

| <b>Apache-128</b> (A-128)     | Cascade Lake<br>18 Cores (2.7 GHz) | 6x 128 GB 100 Series<br>@ 2666 MT/s   15 Watt | 6x 16 GB | Ubuntu 20.04<br>(5.4 kernel) |

| <b>Apache-256</b> (A-256)     | Cascade Lake<br>18 Cores (2.6 GHz) | 6x 256 GB 100 Series<br>@ 2666 MT/s   18 Watt | 6x 16 GB | Ubuntu 20.04<br>(5.4 kernel) |

| <b>Apache-512</b> (A-512)     | Cascade Lake<br>24 Cores (2.4 GHz) | 6x 512 GB 100 Series<br>@ 2666 MT/s   15 Watt | 6x 64 GB | Ubuntu 20.04<br>(5.4 kernel) |

| <b>Barlow-256</b> (B-256/B-D) | Ice Lake<br>32 Cores (2.2 GHz)     | 8x 256 GB 200 Series<br>@ 3200 MT/s   15 Watt | 8x 32 GB | Ubuntu 20.04<br>(5.4 kernel) |

### 3.3.1 Setup And Methodology