# Methodology for Standard Cell-based Design and Implementation of Reliable and Robust Hardware Systems

**Oliver Schrape**

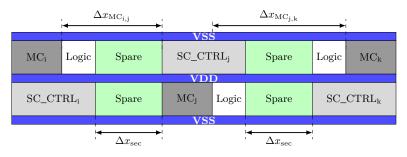

Dissertation

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften (Dr.-Ing.)

in der Wissenschaftsdisziplin "Rechnerarchitektur und Fehlertoleranz"

eingereicht an der Mathematisch-Naturwissenschaftlichen Fakultät Institut für Informatik und Computational Science der Universität Potsdam und IHP Leibniz-Institut für innovative Mikroelektronik

Ort und Tag der Disputation: Universität Potsdam, am 17. Februar 2023 Unless otherwise indicated, this work is licensed under a Creative Commons License Attribution 4.0 International.

This does not apply to quoted content and works based on other permissions.

To view a copy of this licence visit:

https://creativecommons.org/licenses/by/4.0

| Hauptbetreuer: | Prof. Dr. Miloš Krstić                                        |

|----------------|---------------------------------------------------------------|

|                | (Universität Potsdam und IHP)                                 |

| Betreuer:      | Prof. DrIng. habil. Michael Hübner                            |

|                | (Brandenburgische Technische Universität Cottbus-Senftenberg) |

| Gutachter 1:   | Prof. Dr. Miloš Krstić                                        |

|                | (Universität Potsdam und IHP)                                 |

| Gutachter 2:   | Prof. DrIng. habil. Michael Hübner                            |

|                | (Brandenburgische Technische Universität Cottbus-Senftenberg) |

| Gutachter 3:   | Prof. Ney Laert Vilar Calazans                                |

|                | (Pontifical Catholic University of Rio Grande do Sul (PUCRS)) |

Published online on the

Publication Server of the University of Potsdam: https://doi.org/10.25932/publishup-58932 https://nbn-resolving.org/urn:nbn:de:kobv:517-opus4-589326 "Ausdauer wird früher oder später belohnt – meistens aber später."

— Wilhelm Busch

... for my wife and my daughters

# Contents

| $\mathbf{C}$ | onter | nts            |                                               | i    |

|--------------|-------|----------------|-----------------------------------------------|------|

| A            | bstra | nct            |                                               | vii  |

| Zι           | usam  | menfas         | sung                                          | ix   |

| A            | crony | $\mathbf{yms}$ |                                               | xi   |

| 1            | Intr  | oducti         | on                                            | 1    |

|              | 1.1   | Motiva         | tion                                          | . 1  |

|              | 1.2   | Reliabl        | le and Robust Hardware Systems                | . 3  |

|              | 1.3   | Contri         | bution of this Work                           | . 5  |

|              | 1.4   | Publica        | ations Related to this Work                   | . 6  |

|              | 1.5   | Structu        | ure of the Thesis                             | . 8  |

| <b>2</b>     | Bac   | kgroun         | d                                             | 11   |

|              | 2.1   | Semico         | nductor Technologies                          | . 11 |

|              | 2.2   | Standa         | rd Cell Library Development                   | . 12 |

|              |       | 2.2.1          | View Generation Procedure                     | . 12 |

|              |       | 2.2.2          | Physical View                                 | . 13 |

|              |       | 2.2.3          | Standard Cell Characterization                | . 15 |

|              | 2.3   | Digital        | Design Flow                                   | . 17 |

|              | 2.4   | Design         | -for-Testability and Low-Power Digital Design | . 20 |

|              |       | 2.4.1          | Structural Test – Scan-Test                   | . 21 |

|              |       | 2.4.2          | Clock-Gating                                  | . 22 |

|              | 2.5   | Signal         | Integrity Effects                             | . 22 |

|              | 2.6   | Differe        | ntial Logic and Signaling                     | . 24 |

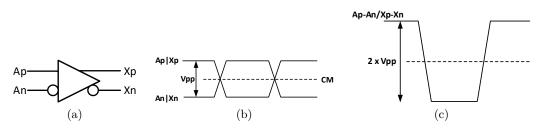

|              |       | 2.6.1          | Differential Signaling                        | . 24 |

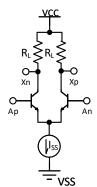

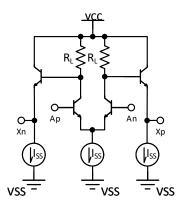

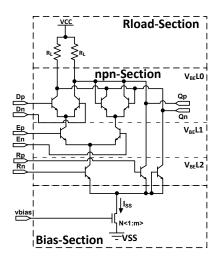

|              |       | 2.6.2          | Current-Mode Logic/Emitter-Coupled Logic      | . 26 |

|              |       | 2.6.3          | Limitation                                    | . 27 |

|              |       | 2.6.4          | Comparison of CML and CMOS Inverter           | . 28 |

|              | 2.7   | Radiat         | ion-Induced Effects                           | . 29 |

|   |     | 2.7.1                              | Total Ionizing Dose                                    | 29 |  |

|---|-----|------------------------------------|--------------------------------------------------------|----|--|

|   |     | 2.7.2                              | Single-Event Effects                                   | 30 |  |

|   |     |                                    | 2.7.2.1 Hard-Errors – Single Event Latchup and Burnout | 31 |  |

|   |     |                                    | 2.7.2.2 Soft-Errors – Single Event Transient and Upset | 31 |  |

|   |     | 2.7.3                              | Charge Generation and Linear Energy Transfer (LET)     | 32 |  |

|   |     | 2.7.4                              | Circuit Cross-Section                                  | 33 |  |

|   |     | 2.7.5                              | Charge-Sharing                                         | 34 |  |

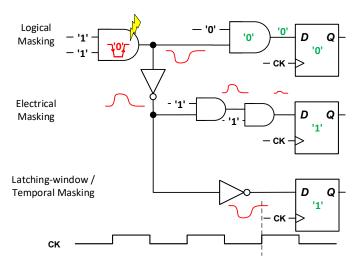

|   |     | 2.7.6                              | Transient Masking                                      | 34 |  |

|   |     | 2.7.7                              | Single Event Transient Quenching and Broadening        | 35 |  |

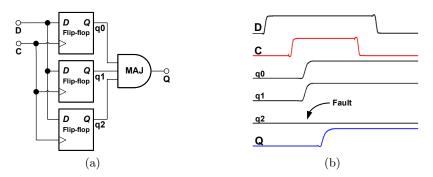

|   | 2.8 | Fault-                             | Tolerant Circuits                                      | 35 |  |

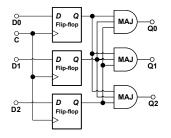

|   |     | 2.8.1                              | Triple Modular Redundancy (TMR)                        | 35 |  |

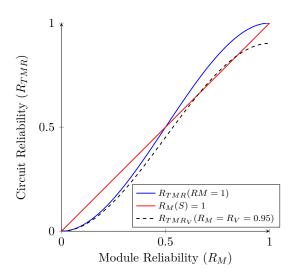

|   |     | 2.8.2                              | Reliability of TMR Circuits                            | 37 |  |

|   | 2.9 | Tempo                              | oral Redundancy/Temporal Sampling                      | 38 |  |

| 3 | Rel | ated V                             | Vork                                                   | 41 |  |

|   | 3.1 | Desigr                             | Automation of Differential Circuits                    | 41 |  |

|   |     | 3.1.1                              | Secure Digital Design Flow                             | 42 |  |

|   |     | 3.1.2                              | Via-Programmable Flow                                  | 43 |  |

|   |     | 3.1.3                              | Fat-Wire Approach                                      | 44 |  |

|   | 3.2 | Differe                            | ential CML-based Standard Cell Library Concepts        | 45 |  |

|   |     | 3.2.1                              | MCML Library Generation with Footprints                | 45 |  |

|   |     | 3.2.2                              | ECL Standard Cell Libraries                            | 45 |  |

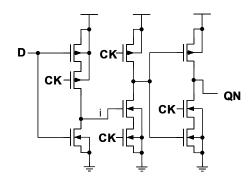

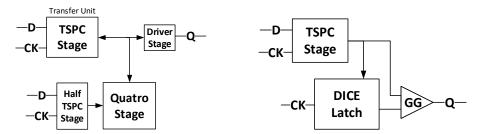

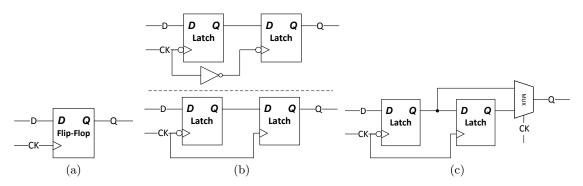

|   | 3.3 | 3 Standard Flip-Flop Architectures |                                                        |    |  |

|   | 3.4 |                                    |                                                        |    |  |

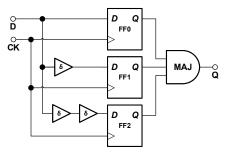

|   | 3.5 | Single                             | Event Transient Mitigation                             | 49 |  |

|   |     | 3.5.1                              | General Transient Mitigation                           | 49 |  |

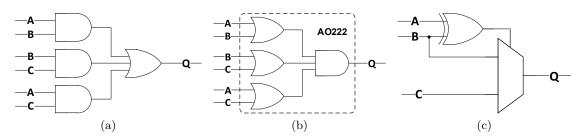

|   |     | 3.5.2                              | Filtering Transient with Guard-Gates/C-elements        | 49 |  |

|   |     | 3.5.3                              | Transient Filters on Data Paths in TMR Circuits        | 51 |  |

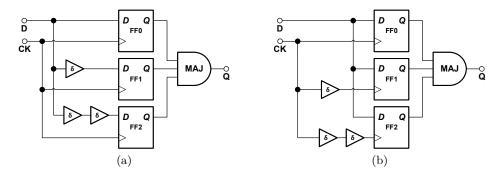

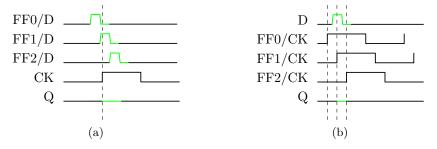

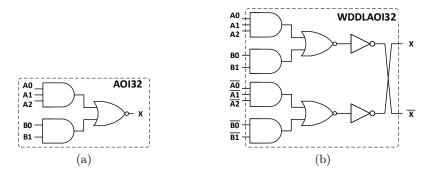

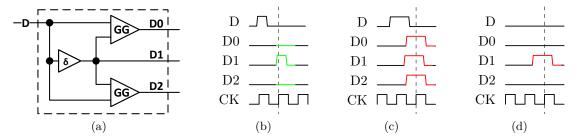

|   |     | 3.5.4                              | Transient Mitigation in TMR Circuits with Clock Delays | 52 |  |

|   | 3.6 | Harde                              | ning by Structural Modification                        | 53 |  |

|   | 3.7 |                                    | tion-Hard Flip-Flop Architectures                      | 53 |  |

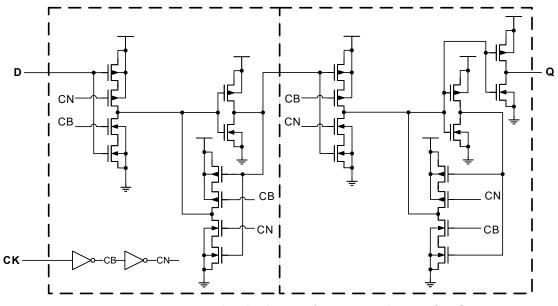

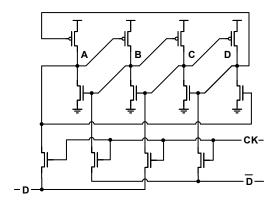

|   |     | 3.7.1                              | Dual Interlocked Storage Cell                          | 53 |  |

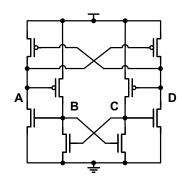

|   |     | 3.7.2                              | Quatro Cell                                            | 54 |  |

|   |     | 3.7.3                              | Heavy Ion Tolerant Flip-Flop                           | 55 |  |

|   |     | 3.7.4                              | Further Hardened Flip-Flop Compositions                | 55 |  |

|   | 3.8 | Radia                              | tion-Hardening-by-Design (RHBD) Flip-Flops             | 56 |  |

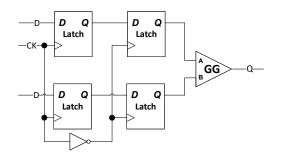

|   |     | 3.8.1                              | Built-in Soft Error Resilient (BISER)                  | 56 |  |

|   |     | 3.8.2                              | Dual/Double Modular Redundancy Extensions              | 57 |  |

|   |     | 3.8.3                              | Full-Triple Modular Redundancy (FTMR) Flip-Flop        | 57 |  |

|   |     | 3.8.4                              | Robust Triple Modular Redundancy Flip-Flop             | 58 |  |

|   |     | 3.8.5                              | Self-Correction Function                               | 60 |  |

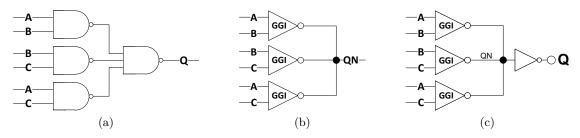

|   |     | 3.8.6                              | Voter Architectures for TMR                            | 61 |  |

|   | 3.9 | Addre                              | essed Open Issues in this Thesis                       | 62 |  |

|   |     | 3.9.1  | Addressed Issues for Differential Logic Design                          |

|---|-----|--------|-------------------------------------------------------------------------|

|   |     | 3.9.2  | Addressed Issues for Radiation-Hardening-by-Design Circuits $\ldots$ 65 |

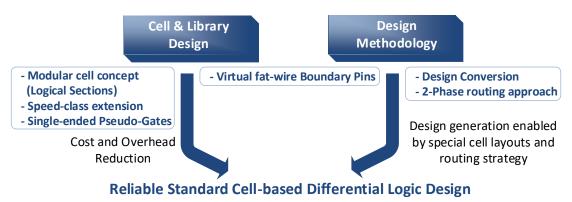

| 4 | Cor | ncepts | and Methodology for Differential Logic Design 65                        |

|   | 4.1 | -      | uction $\ldots$                                                         |

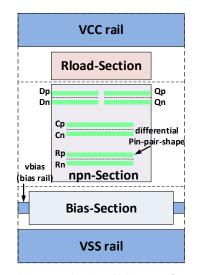

|   | 4.2 |        | ard Cell Concept                                                        |

|   |     | 4.2.1  | Specification                                                           |

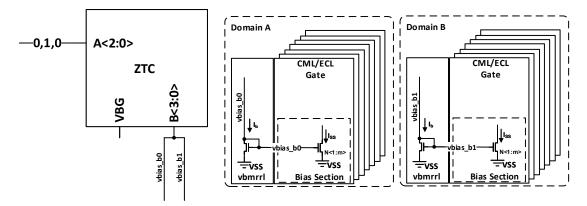

|   |     | 4.2.2  | Supported Bias Concept                                                  |

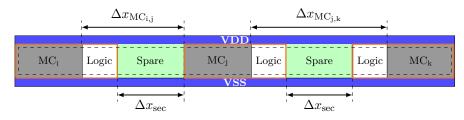

|   |     | 4.2.3  | Modular Standard Cells – Logical Sections                               |

|   |     | 4.2.4  | Cell Configurations – Speed-Classes                                     |

|   |     | 4.2.5  | Speed-Class Extension                                                   |

|   |     | 4.2.6  | Level-Shifter                                                           |

|   | 4.3 | Librar | y Aspects for Differential Logic Design                                 |

|   |     | 4.3.1  | Standard Cell Set                                                       |

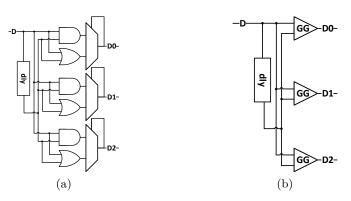

|   |     | 4.3.2  | Single-ended Pseudo-Gates                                               |

|   |     | 4.3.3  | Fat-wire Specification                                                  |

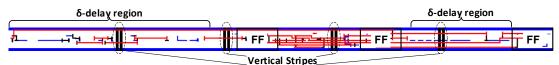

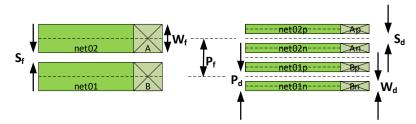

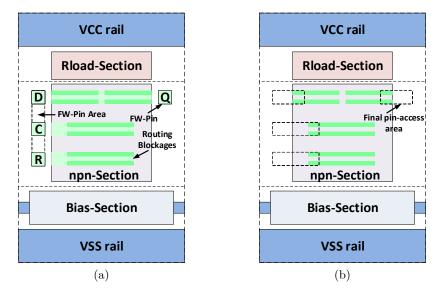

|   |     | 4.3.4  | Fat-wire Compatible Differential Standard Cell Layouts 80               |

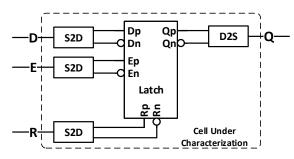

|   |     | 4.3.5  | Characterization of Differential Standard Cells                         |

|   |     | 4.3.6  | Physical View Generation                                                |

|   | 4.4 | Design | Methodology for Differential Logic Design                               |

|   |     | 4.4.1  | Design Flow for Differential Standard Cell-based Design 85              |

|   |     | 4.4.2  | Limitations and Features for RTL Design                                 |

|   |     | 4.4.3  | Gate-Level Synthesis                                                    |

|   |     | 4.4.4  | Placement and First Routing-Phase                                       |

|   |     | 4.4.5  | Design Conversion                                                       |

|   |     | 4.4.6  | Second Routing-Phase                                                    |

|   | 4.5 | Summ   | ary                                                                     |

| 5 | Cor | icepts | and Methodology for RHBD Circuits 95                                    |

| 0 | 5.1 | -      | uction                                                                  |

|   | 5.2 |        | ard Cell Library                                                        |

|   |     | 5.2.1  | Additional Cell Set                                                     |

|   |     | 5.2.2  | Robust Driver Cells                                                     |

|   |     | 5.2.3  | Transient Filter Cells                                                  |

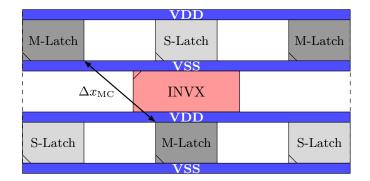

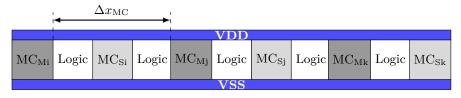

|   |     | 5.2.4  | Robust Memory Cells – $\Delta$ TMR Cells                                |

|   | 5.3 | RHBD   | 0 TMR Cells – Logical Sections                                          |

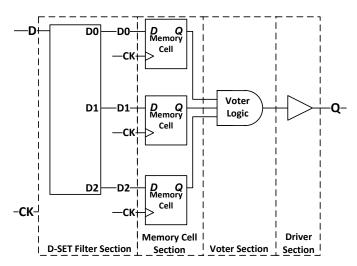

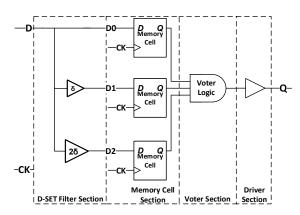

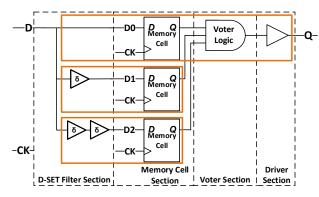

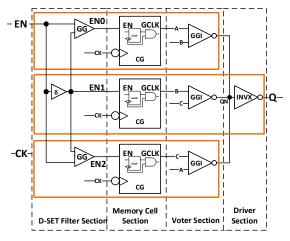

|   |     | 5.3.1  | D-SET Filter Section                                                    |

|   |     | 5.3.2  | Memory Cell Section                                                     |

|   |     | 5.3.3  | Voter Section                                                           |

|   |     | 5.3.4  | Driver Section                                                          |

|   | 5.4 | Specia | l RHBD TMR Cells                                                        |

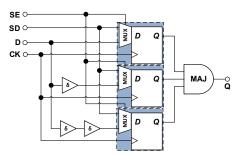

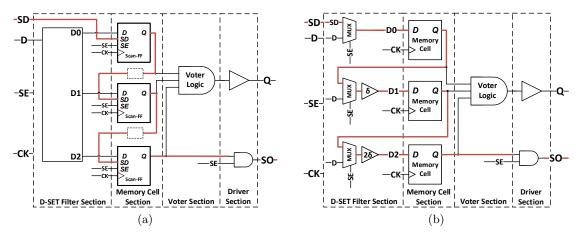

|   |     | 5.4.1  | RHBD TMR Scan-Flip-Flops                                                |

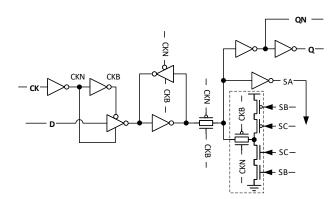

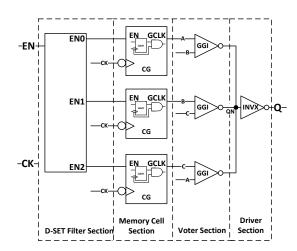

|   |     | 5.4.2  | RHBD TMR Clock-Gating Cells                                             |

| Bi            | Bibliography 171                    |                 |                                                                                      |          |

|---------------|-------------------------------------|-----------------|--------------------------------------------------------------------------------------|----------|

| $\mathbf{Li}$ | List of Listings 169                |                 |                                                                                      |          |

| $\mathbf{Li}$ | List of Figures163List of Tables167 |                 |                                                                                      | 167      |

| Li            |                                     |                 |                                                                                      | 163      |

| Appendix 162  |                                     |                 | 162                                                                                  |          |

| 7             | Con                                 | clusio          | n                                                                                    | 155      |

| _             | ~                                   |                 | *                                                                                    |          |

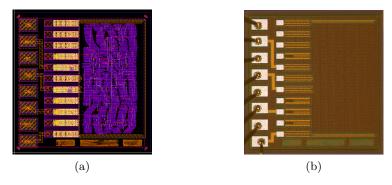

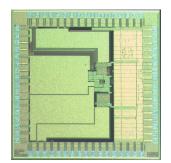

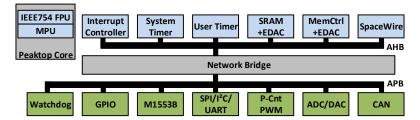

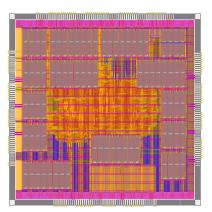

|               |                                     | 6.3.2           | Microcontroller Chip                                                                 |          |

|               | 0.0                                 | 6.3.1           | ation of the Design Flow for Realistic ApplicationsA 7.5-15.5 MSPS 14-bit ADC Core   |          |

|               | 6.3                                 | 6.2.8<br>Evolue | Results and Discussion                                                               |          |

|               |                                     | 6.2.7           | Irradiation Campaigns                                                                |          |

|               |                                     | 6.2.6           | Shift Register Test Vehicles                                                         |          |

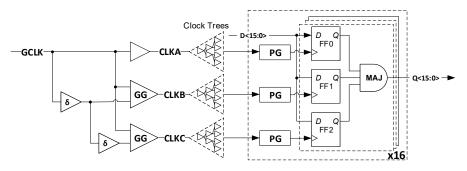

|               |                                     | 6.2.5           | Development of robust clock-gate $CG-\Delta TMR$                                     |          |

|               |                                     | 6.2.4           | Development of robust T- $\Delta$ TMR cells                                          |          |

|               |                                     | 6.2.3           | Development of robust S- $\Delta$ TMR and SC- $\Delta$ TMR cells                     |          |

|               |                                     | 6.2.2           | Development of robust L- $\Delta$ TMR and LM- $\Delta$ TMR cells                     |          |

|               |                                     | 6.2.1           | Development of robust $\Delta$ TMR cells $\ldots \ldots \ldots \ldots \ldots \ldots$ | . 132    |

|               | 6.2                                 | Develo          | opment and Evaluation of Radiation-Hardened $\Delta$ TMR Standard Cé                 | ells 132 |

|               |                                     | 6.1.3           | Results and Discussion                                                               | . 130    |

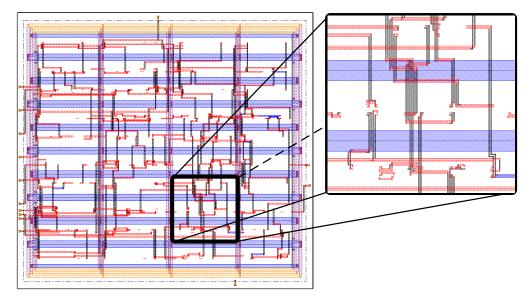

|               |                                     | 6.1.2           | Implementation                                                                       | . 129    |

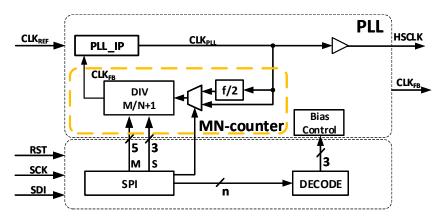

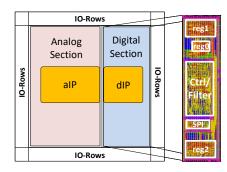

|               |                                     | 6.1.1           | Architecture Overview                                                                |          |

|               | 6.1                                 |                 | iable Digitally-Designed Differential Logic Design                                   |          |

| 6             | Eva                                 | luatior         | n of the Concepts                                                                    | 127      |

|               | 5.8                                 | Summ            | ary                                                                                  | . 126    |

|               |                                     | 5.7.4           | Place and Route                                                                      |          |

|               |                                     | 5.7.3           | Scan-Test – Pattern Generation                                                       | . 124    |

|               |                                     | 5.7.2           | Gate-Level Synthesis                                                                 | . 123    |

|               |                                     | 5.7.1           | Handling of Critical Nets                                                            | . 122    |

|               | 5.7                                 |                 | 1 Methodology for Radiation-Hardening-by-Design                                      |          |

|               | 5.6                                 |                 | t Aspects for RHBD TMR Cells                                                         |          |

|               | 5.5                                 | Chara           | cterization of RHBD TMR Cells                                                        |          |

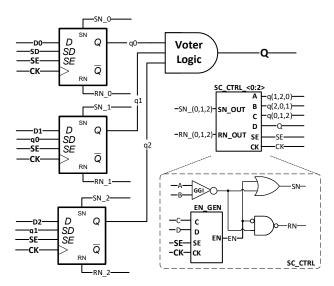

|               |                                     | 5.4.3           | Self-Correcting TMR Flip-Flops                                                       | . 114    |

## Acknowledgement

First of all, I would like to thank my loved ones, my wife and my two daughters. Thank you so much for the encouragement, the patience, and not-too-loud-grumbling about my non-presence, even though I was actually physically there ...

A special thanks also goes to my parents for not deviating in many things & decisions.

Frank – Thank you for everything and for guiding me through my first steps at IHP.

Gerald, Daniel S.– You triggered my interests for differential logic design – and I really tried to forget, but I could not give it up ;)

Florian, Stephan, and Manuel – Thanks for your support!

Daniel M. – Thanks for your time while bringing these crazy analog things closer to me. I learned a lot and still benefit from it.

Steffen, Pinky, Anselm, Marko, Junchao, Marcus, Goran, Carsten, Klaus, Philip, and Alexey – Everyone needs an own "Quietscheentchen" for small-talk, discussion and brainstorming. Apparently, I have more than one. So, thanks for being mine and never complaining about my (sometimes same) questions, not well-thought out ideas, and also – confusion!

I would also like to thank the whole IHP and the colleagues not announced by name. Many thanks to all of you!

Special thanks go also to Prof. Ney Laert Vilar Calazans for the criticism, the hints and the comments that have greatly contributed to the improvement of this Thesis.

Miloš - thank you so much ... for your time, for the new challenges, the confidence but also the patience, and especially, the discussions and hints – always served with healthy, valuable and friendly criticism ;)

### Abstract

Reliable and robust data processing is one of the hardest requirements for systems in fields such as medicine, security, automotive, aviation, and space, to prevent critical system failures caused by changes in operating or environmental conditions. In particular, Signal Integrity (SI) effects such as crosstalk may distort the signal information in sensitive mixed-signal designs. A challenge for hardware systems used in the space are radiation effects. Namely, Single Event Effects (SEEs) induced by high-energy particle hits may lead to faulty computation, corrupted configuration settings, undesired system behavior, or even total malfunction.

Since these applications require an extra effort in design and implementation, it is beneficial to master the standard cell design process and corresponding design flow methodologies optimized for such challenges. Especially for reliable, low-noise differential signaling logic such as Current Mode Logic (CML), a digital design flow is an orthogonal approach compared to traditional manual design. As a consequence, mandatory preliminary considerations need to be addressed in more detail. First of all, standard cell library concepts with suitable cell extensions for reliable systems and robust space applications have to be elaborated. Resulting design or improve the radiation-hardness. In parallel, the main objectives of the proposed cell architectures are to reduce the occupied area, power, and delay overhead. Second, a special setup for standard cell characterization is additionally required for a proper and accurate logic gate modeling. Last but not least, design methodologies for mandatory design flow stages such as logic synthesis and place and route need to be developed for the respective hardware systems to keep the reliability or the radiation-hardness at an acceptable level.

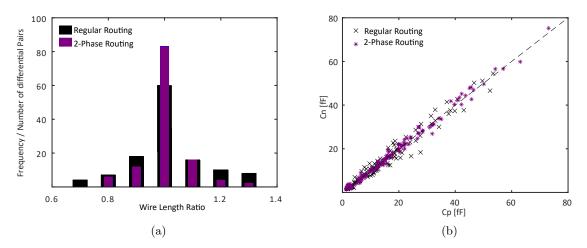

This Thesis proposes and investigates standard cell-based design methodologies and techniques for reliable and robust hardware systems implemented in a conventional semiconductor technology. The focus of this work is on reliable differential logic design and robust radiation-hardening-by-design circuits. The synergistic connections of the digital design flow stages are systematically addressed for these two types of hardware systems. In more detail, a library for differential logic is extended with single-ended pseudo-gates for intermediate design steps to support the logic synthesis and layout generation with commercial Computer-Aided Design (CAD) tools. Special cell layouts are proposed to relax signal routing. A library set for space applications is similarly extended by novel Radiation-Hardening-by-Design (RHBD) Triple Modular Redundancy (TMR) cells, enabling a one fault correction. Therein, additional optimized architectures for glitch filter cells, robust scannable and self-correcting flip-flops, and clock-gates are proposed. The circuit concepts and the physical layout representation views of the differential logic gates and the RHBD cells are discussed. However, the quality of results of designs depends implicitly on the accuracy of the standard cell characterization which is examined for both types therefore. The entire design flow is elaborated from the hardware design description to the layout representations. A 2-Phase routing approach together with an intermediate design conversion step is proposed after the initial place and route stage for reliable, pure differential designs, whereas a special constraining for RHBD applications in a standard technology is presented.

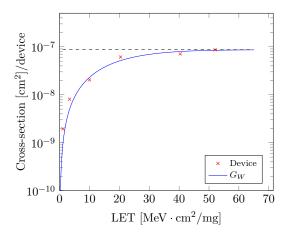

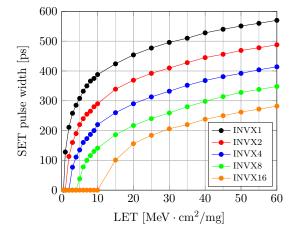

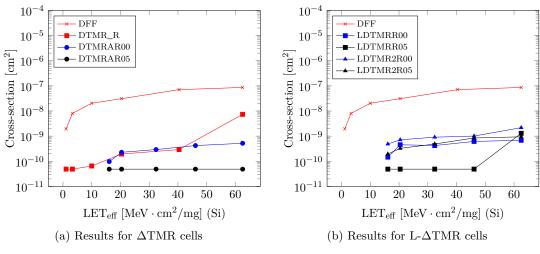

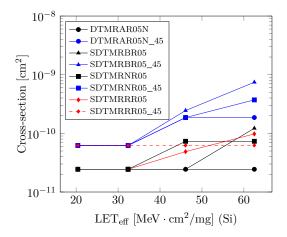

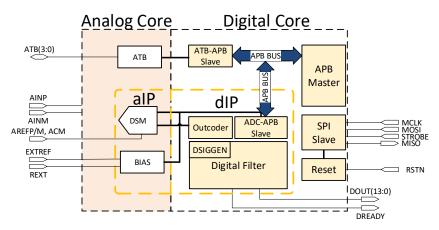

The digital design flow for differential logic design is successfully demonstrated on a reliable differential bipolar CML application. A balanced routing result of its differential signal pairs is obtained by the proposed 2-Phase-routing approach. Moreover, the elaborated standard cell concepts and design methodology for RHBD circuits are applied to the digital part of a 7.5-15.5 MSPS 14-bit Analog-to-Digital Converter (ADC) and a complex microcontroller architecture. The ADC is implemented in an unhardened standard semiconductor technology and successfully verified by electrical measurements. The overhead of the proposed hardening approach is additionally evaluated by design exploration of the microcontroller application. Furthermore, the first obtained related measurement results of novel RHBD- $\Delta$ TMR flip-flops show a radiation-tolerance up to a threshold Linear Energy Transfer (LET) of 46.1, 52.0, and 62.5 MeV cm<sup>2</sup> mg<sup>-1</sup> and savings in silicon area of 25-50 % for selected TMR standard cell candidates.

As a conclusion, the presented design concepts at the cell and library levels, as well as the design flow modifications are adaptable and transferable to other technology nodes. In particular, the design of hybrid solutions with integrated reliable differential logic modules together with robust radiation-tolerant circuit parts is enabled by the standard cell concepts and design methods proposed in this work.

#### Zusammenfassung

Eine zuverlässige und robuste Datenverarbeitung ist eine der wichtigsten Voraussetzungen für Systeme in Bereichen wie Medizin, Sicherheit, Automobilbau, Luft- und Raumfahrt, um kritische Systemausfälle zu verhindern, welche durch Änderungen der Betriebsbedingung oder Umweltgegebenheiten hervorgerufen werden können. Insbesondere Signalintegritätseffekte (Signal Integrity (SI)) wie das Übersprechen und Überlagern von Signalen (crosstalk) können den Informationsgehalt in empfindlichen Mixed-Signal-Designs verzerren. Eine zusätzliche Herausforderung für Hardwaresysteme für Weltraumanwendungen ist die Strahlung. Resultierende Effekte, die durch hochenergetische Teilchentreffer ausgelöst werden (Single Event Effects (SEEs)), können zu fehlerhaften Berechnungen, beschädigten Konfigurationseinstellungen, unerwünschtem Systemverhalten oder sogar zu völliger Fehlfunktion führen.

Da diese Anwendungen einen zusätzlichen Aufwand beim Entwurf und der Implementierung erfordern, ist es von Vorteil, über Standardzellenentwurfskonzepte und entsprechende Entwurfsablaufmethoden zu verfügen, die für genau solche Herausforderungen optimiert sind. Insbesondere für zuverlässige, rauscharme differenzielle Logik, wie der Current Mode Logic (CML), ist ein digitaler Entwurfsablauf ein orthogonaler Ansatz im Vergleich zum traditionellen manuellen Entwurfskonzept. Infolgedessen müssen obligatorische Vorüberlegungen detaillierter behandelt werden. Zunächst sind Konzepte für Standardzellbibliotheken mit geeigneten Zellerweiterungen für zuverlässige Systeme und robuste Raumfahrtanwendungen zu erarbeiten. Daraus resultierende Entwurfskonzepte auf Zellebene sollten die logische Synthese für den differenziellen Logikentwurf ermöglichen oder die Strahlungshärte eines Designs verbessern. Parallel dazu sind die Hauptziele der vorgeschlagenen Zellarchitekturen, die Verringerung der genutzten Siliziumfläche und der Verlustleistung sowie den Verzögerungs-Overhead zu minimieren. Zweitens ist ein spezieller Aufbau für die Charakterisierung von Standardzellen erforderlich, um eine angemessene und genaue Modellierung der Logikgatter zu ermöglichen. Nicht zuletzt müssen für die jeweiligen Hardwaresysteme Methoden für die Entwurfsphasen wie Logik-Synthese und das Platzieren und Routen (Place and Route (PnR)) entwickelt werden, um die Zuverlässigkeit beziehungsweise die Strahlungshärte auf einem akzeptablen Niveau zu halten.

In dieser Arbeit werden standardisierte Zellen-basierte Entwurfsmethoden und -techniken für zuverlässige und robuste Hardwaresysteme vorgeschlagen und untersucht, welche in einer herkömmlichen Halbleitertechnologie implementiert werden. Dabei werden zuverlässige differenzielle Logikschaltungen und robuste strahlungsgehärtete Schaltungen betrachtet. Die synergetischen Verbindungen des digitalen Entwurfs werden systematisch für diese beiden Hardwaresysteme behandelt. Im Detail wird eine Bibliothek für differentielle Logik mit Single-Ended-Pseudo-Gattern für Zwischenschritte erweitert, die die Logiksynthese und Layout-Generierung mit heutigen Entwicklungswerkzeugen unterstützen. Ein spezieller Rahmen für das Layout der Zellen wird vorgeschlagen, um das Routing der Signale zu vereinfachen. Die Bibliothek für Raumfahrtanwendungen wird in ähnlicher Weise um neuartige Radiation-Hardening-by-Design (RHBD)-Zellen mit dreifacher modularer Redundanz (Triple Modular Redundancy (TMR)) erweitert, welche eine 1-Bit-Fehlerkorrektur erlaubt. Zusätzlich werden optimierte Architekturen für Glitch-Filterzellen, robuste abtastbare (scannable) und selbstkorrigierende Flip-flops und Taktgatter (clock-gates) vorgeschlagen. Die Schaltungskonzepte, die physische Layout-Repräsentation der differentiellen Logikgatter und der vorgeschlagenen RHBD-Zellen werden diskutiert. Die Qualität der Ergebnisse der Entwürfe hängt jedoch implizit von der Genauigkeit der Standardzellencharakterisierung ab, die daher für beide Typen untersucht wird. Der gesamte Entwurfsablauf wird von der Entwurfsbeschreibung der Hardware bis hin zur generierten Layout-Darstellung ausgearbeitet. Infolgedessen wird ein 2-Phasen-Routing-Ansatz zusammen mit einem zwischengeschalteten Design-Konvertierungsschritt nach der initialen PnR-Phase für zuverlässige, differentielle Designs vorgeschlagen, während ein spezielles Constraining für RHBD-Anwendungen vorgestellt wird.

Der digitale Entwurfsablauf für Differenziallogik wird erfolgreich an einer zuverlässigen bipolaren Differenzial-CML-Anwendung demonstriert. Durch den 2-Phasen-Routing-Ansatz wird ein ausgewogenes Routing-Ergebnis differentieller Signalpaare erzielt. Darüber hinaus werden die erarbeiteten Standardzellenkonzepte und die Entwurfsmethodik für RHBD-Schaltungen auf den digitalen Teil eines 7.5-15.5 MSPS 14-bit Analog-Digital-Wandlers (ADC) und einer komplexen Mikrocontroller-Architektur angewandt. Der ADC wurde in einer nicht-gehärteten Standard-Halbleitertechnologie implementiert und erfolgreich durch elektrische Messungen verifiziert. Der Mehraufwand des Härtungsansatzes wird zusätzlich durch Design Exploration der Mikrocontroller-Anwendung bewertet. Ferner zeigen erste Messergebnisse der neuartigen RHBD- $\Delta$ TMR-Flip-flops eine Strahlungstoleranz bis zu einem linearen Energietransfer (Linear Energy Transfers (LET)) Schwellwert von 46.1, 52.0 und 62.5 MeV cm<sup>2</sup> mg<sup>-1</sup> und eine Einsparung an Siliziumfläche von 25-50 % für ausgewählte TMR-Standardzellenkandidaten.

Die vorgestellten Entwurfskonzepte auf Zell- und Bibliotheksebene sowie die Änderungen des Entwurfsablaufs sind anpassbar und übertragbar auf andere Technologieknoten. Insbesondere der Entwurf hybrider Lösungen mit integrierten zuverlässigen differenziellen Logikmodulen zusammen mit robusten strahlungstoleranten Schaltungsteilen wird durch die in dieser Arbeit vorgeschlagenen Konzepte und Entwurfsmethoden ermöglicht.

# Acronyms

ADC Analog-to-Digital Converter. **ALU** Arithmetic Logic Unit. **AMS** Analog Mixed-Signal. **APB** Advanced Peripheral Bus. ASCII American Standard Code for Information Interchange. ASIC Application Specific Integrated Circuit. ATPG Automatic Test Pattern Generation. **BiCMOS** Bipolar CMOS. **BISER** Built-In Soft Error Resilience. **BTS** Buffer Tree Synthesis. **CAD** Computer-Aided Design. CG Clock-Gating [Cell]. **CML** Current-Mode Logic. CMOS Complementary Metal-Oxide Semiconductor. CQFP Ceramic Quad Flat Package. CT Clock Tree. **CTS** Clock Tree Synthesis. **CUT** Cell Under Test. CZ Characterization. **D2S** differential-to-single-ended. **DDF** Digital Design Flow. **DEF** Design Exchange Format (DEF/.deffile). **DfT** Design-for-Testability.

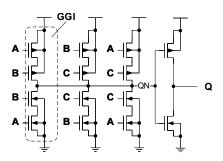

**DICE** Dual Interlocked Storage Cell. **DIFF** differential. **DLG** differential logic gate. **DMR** Dual/Double Modular Redundancy. **DRC** Design Rule Check. **DRV** Design Rule Violation. **DSP** Digital Signal Processing. **ECL** Emitter-Coupled Logic. EGR Enhanced Guard Rings. **ELT** Enclosed Layout Transistor. **ERC** Electrical Rule Check. FF Flip-Flop. FFT Fast Fourier Transform. FPU Floating Point Unit. FTMR full-TMR. FW fat-wire. **GDS** Graphic Database System II. GG Guard-Gate. **GGB** Guard-Gate Buffer. **GGI** Guard-Gate Inverter. **GLS** Gate-Level Synthesis. HBT Hetero Junction Bipolar Transistor [device]. HDL Hardware Description Language. HIT Heavy Ion Tolerant. **IC** Integrated Circuit. ICG Integrated Clock-Gating [cell].

IO Input/Output (e.g. pads, pins, or ports).

**IP** Intellectual Property.

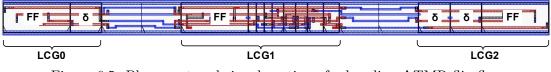

LCG Logically-Connected Group.

LEAP Layout Design through Error-Aware Transistor Positioning.

LEF Layout Exchange Format.

LET Linear Energy Transfer.

LUT Lookup Table.

LVDS Low Voltage Differential Signaling.

LVS Layout versus Schematic.

MBU Multiple-Bit Upset.

MCML MOS Current-Mode Logic.

MNCC Multiple Node Charge Collection.

MOS Metal-Oxide Semiconductor.

MPU Memory Protection Unit.

MS mixed-signal.

NM Noise Margin.

NMOS N-channel metal-oxide semiconductor.

NMR N-Modular Redundancy.

NRE Non-Recurring Engineering [costs].

**OPC** Operating Current.

PA Power Analysis.

PDK Process Design Kit.

PDN Power Distribution Network.

PGA Pin Grid Array.

PLL Phase-Locked Loop.

PMOS P-channel metal-oxide semiconductor.

PnR Place and Route.

PVT Process, Voltage and Temperature.

RF radio frequency.

RHBD Radiation-Hardness/Hardening-by-Design.

**RHBP** Radiation-Hardening-by-Process.

**RISC** Reduced Instruction Set Computer. **RnR** reliable and robust [[hardware] system]. **RnRS** reliable and robust [hardware] system(s). **RTL** Register Transfer Level. S2D single-ended-to-differential. SCL Source-Coupled Logic. SDC Synopsys Design Constraint Format. **SDF** Standard Delay Format. **SE** single-ended. **SEB** Single Event Burnout. **SEE** Single Event Effect. **SEL** Single Event Latchup. SEPG Single-ended Pseudo-Gate. **SET** Single Event Transient. **SEU** Single Event Upset. SI Signal Integrity. SoC System-on-[a]-Chip. SotA State-of-the-Art. **SPI** Serial Peripheral Interface. **STA** Static Timing Analysis.

TCL Tool command language.

TID Total Ionizing Dose.

TMR Triple Modular Redundancy.

TR Temporal Redundancy.

TSPC True Single-Phase Clock.

VHDL Very High Speed Integrated Circuit Hardware Description Language.

${\bf VLSI}$  Very Large Scale Integration.

- **WDDL** Wave Dynamic Differential Logic.

- **XML** Extensible Markup Language.

- **ZTC** Zero Temperature Coefficient (Current).

"Holzhacken ist deshalb so beliebt, weil man bei dieser Tätigkeit den Erfolg sofort sieht." — Albert Einstein

## Chapter 1

# Introduction

This Chapter introduces the motivation of this Thesis, the definition of a reliable and robust hardware system, the contribution, and an overview of the first-author publications and patents related to this work. Finally, the structure of the thesis is listed at the end of this Chapter.

#### 1.1 Motivation

Very Large Scale Integration (VLSI) circuits or System-on-[a]-Chip (SoC) for critical applications in the fields of medicine, security, automotive, aviation, and space have to operate reliably under all circumstances. They require a specific, *fault-tolerant* implementation in order to prevent system failures caused by changes in operating conditions, environmental conditions or component malfunctions. If the system parameters are out of specification, low quality of signals, uncovered functional states or total system failure may result.

One of the root causes of faults in the application fields of aviation and space is radiation leading to bit-flips in memory cells, voltage glitches, displacement damage, or ionizing dose effects [1]. These *radiation-induced* effects can result in structural damages in the semiconductor devices, in long-term device performance degradation or in temporal logical errors. One recent example is the loss of up to 40 SpaceX Starlink satellites due to solar storm [2]. Furthermore, an Airbus 330 was nearly losing the control in 2008 by pitching downward twice in rapid succession [3]. The cause of this malfunction of onboard computer was later traced to errors induced by cosmic rays. Another sad example closely-connected to malfunction of sensors and control in critical systems are the two plane crashes of Boeing 737 MAX 8 in 2018 and 2019 [4, 5, 6].

Other sources that reduce the systems' reliability are issues related to Signal Integrity (SI) which degrade the quality of signals. Among them the most important effects for SoC designers are signal crosstalk, voltage drop, and noise [7, 8]. In addition, noise is also a serious concern in security applications. The secret keys of crypto-cores can be

extracted by analyzing the generated switching noise on the power supply in hardware designs [9, 10].

However, signal integrity and radiation-induced effects reduce the reliability of hardware systems. They increase criticality and may bring the system to an undesirable, uncovered functional state. Therefore, there is a high demand for hardware systems that are able to tolerate faults and errors, mitigate, or manage these kinds of effects. Moreover, when VLSI circuits are targeted, the digital design approach with its standard cell-based design flow is immediately addressed. Any proposed cell concept and design methodology to obtain Reliable and Robust Hardware Systems (RnR/RnR-Systems (RnRS)) for such critical applications is closely-connected to the digital standard cell-based design flow.

Depending on the application field of RnR-Systems, different development approaches can be selected. The use of *differential logic design* with standard cell gates is a wellknown solution to obtain *reliable* hardware systems and to improve the designs' SI with respect to power supply noise [11]. Similarly, fast differential bipolar current-switchbased logic gates are used in [12] also to achieve the target speed requirements for computation with a low impact on noise performance.

For the field of space applications, special radiation-hard standard cell libraries and IPs are offered for some popular CMOS technology nodes, e.g., [13, 14]. They allow to develop robust hardware systems with the use of the conventional standard cell-based design flow. The alternative approach is known as *Radiation-Hardness/Hardening-by-Design (RHBD)* with the use of commercial, unhardened semiconductor technologies, and standard logic gates together with additional design techniques to achieve the target robustness [15]. Moreover, additional *hardware redundancy* can be added to a design to increase its robustness and fault-tolerance. As can be seen, the standard cell-based design approach is an attractive and popular solution to develop reliable and robust hardware systems (RnRSs).

The scope of this Thesis is related to two types of RnR-Systems, i.e., reliable differential logic design and robust radiation-hardening-by-design circuits. Nevertheless, when standard cell-based RnRS are targeted, the following aspects have to be considered.

First of all, any new cell, highly-required for RnR circuits, has to be developed as a standard cell. Several essential views such as circuit schematic, layout view, functional model, timing and power model have to be generated to enable an effective use of the standard digital design flow. As a consequence, the *compliance* to the standard cell-based design process is one of the most important requirements. In particular for RHBD circuit design, compatible concepts for mandatory low-power and Design for Testability (DfT) features have to be considered.

However, reliability and robustness go hand in hand with design overhead. Larger robust cells, complex differential logic gates, or hardware redundancy and introduced modification at design-level result in penalties in silicon *area* occupation, an increase in *power* or energy consumption, or in additional *delay* overhead. Thus, these three criteria have

to be strictly considered for new cell concepts and for interactions during the different design phases.

Furthermore, alternative circuit concepts and design techniques which increase the reliability or robustness of a circuit may require a deep understanding and knowledge in circuit design. Thus, RnR-cells and standard cell libraries with a more modular construction-kit-like development approach are preferable. They abstract the internal circuit complexity and may reduce the Non-Recurring Engineering costs (NRE) of the development phase.

Finally, concepts and methodologies restricted to one technology are not valuable and limit their usage. Thus, a more generic and portable approach for the design of RnRS is more beneficial and also increases the attractiveness for the industry. This could be transferred to other standard semiconductor technology nodes. Moreover, when the concepts of both systems are developed coherent to each other, a new type of RnR hardware systems can be obtained: a *hybrid* system as a reliable and robust mixed signal SoC. It could consist of circuit parts of complex RHBD IP and reliable differential logic designs on the same die in the same semiconductor technology.

### 1.2 Reliable and Robust Hardware Systems

Every system has to operate functionally properly within its specification under welldefined operating conditions. Among them are temperature ranges, voltage level definitions for power supply and data signals, and target timing requirements in terms of operating speed. These conditions are referred to in this Thesis as *first-order conditions* for hardware systems. They are individually specified for each system and have to be fulfilled without any degradation under each condition.

In addition to this group, significant changes in the environmental condition may simultaneously affect the performance of such a hardware system. They may occur during operation by effects of the environment, by nature, or be caused by, e.g., noise of components inside a system in package, or by on-chip components in a SoC. There can be many reasons causing malfunctions. Probably the most relevant among them are self-heating, vibration, humidity, electromagnetic, or functional errors by radiation-induced effects. However, when a hardware system is additionally specified for operations under such conditions, the system must be even more reliable and robust in addition to its electrical specifications. Hence, these conditions are called *second-order conditions* of a hardware system in this work.

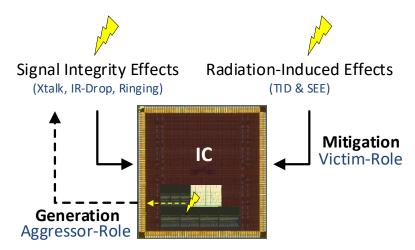

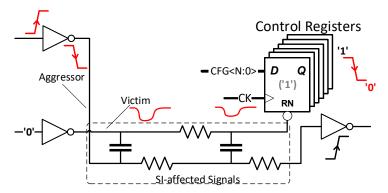

Nevertheless, every system or integrated circuit (IC) can generally assume two different acting roles. On the one hand, a system can suffer from the induced effects bringing the overall system into a defensive, *victim* role (see Figure 1.1). The closest example for such a scenario is radiation a circuit may be exposed to. Resulting Single Event Effects (SEEs) such as glitches on the signal paths, or bit-flips of storage cells can corrupt the data processing or control. On the other side, systems can also take on the opposite,

i.e., the offensive role of an *aggressor*. As an example, the quality of an electrical signal of a sensitive Analog Mixed-Signal (AMS) design may be affected by large noisy digital parts with high switching activity. This could also lead to noise on the signal or power supply, glitches, crosstalk between signals or total loss of signals in the worst case.

Figure 1.1: Possible effects and acting roles general ICs have to deal with

In principle, any system designed to meet the target requirements imposed by *first-order* conditions may still be vulnerable to *second-order* conditions. Furthermore, while a common IC would be completely at the mercy of these additional effects, a reliable and robust hardware system (RnRS) is capable to cope them. These kinds of systems have to ensure the illustrated two key actions in Figure 1.2 simultaneously to their basic function (under first-order conditions). As can be seen in the figure, the first action decreases the fact of an RnR acting as an *aggressor*, whereas the second one works against the *victim*-role, respectively.

Figure 1.2: Key actions of an RnR-System (RnRS)

However, two groups of effects are considered in this work that require additional reliability and robustness of a system, which are defined by the *second-order* conditions. The first group of effects are signal integrity effects, i.e., SI effects. The second group are radiation-induced effects, i.e., Total Ionizing Dose (TID), and SEE in particular, such as latchups, transients, and upsets as a result from energetic particle hits in the silicon.

Thus, within the scope of this Thesis, an RnRS can be generally defined as follows:

A reliable and robust hardware system (RnRS) is capable to adapt to changes of *second-order conditions*. It is able to perform the following two key actions, a) minimizing effect generation, and b) maximizing effect mitigation. These systems are able to cope any effect by implemented mechanisms and design techniques inside the hardware system. An RnRS itself is realized in a standard semiconductor technology.

#### **1.3 Contribution of this Work**

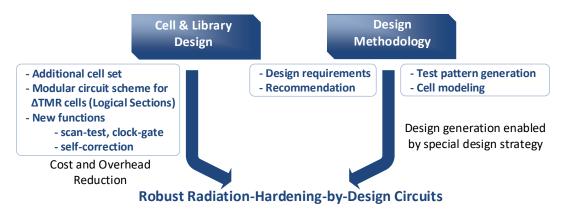

In this Thesis, cell concepts and design methodologies are presented to obtain reliable and robust hardware systems. Two types of systems are addressed: reliable differential logic designs and robust radiation-hardening-by-design circuits. The proposed solutions for cell design and standard cell libraries are applicable to the standard digital design flow. Thus, a VLSI standard cell-based RnR system can be developed. However, since reliability and robustness at the hardware level always involve additional effort in design and resources, the focus is also set on the reduction of the introduced overhead in terms of area, power, and delay independent of the application field. Moreover, the modeling aspect of new cells is additionally covered by the introduction of the characterization presented in this work.

#### **Contribution to Reliable Differential Logic Design**

This work proposes standard cell concept and a design flow for bipolar Current Mode Logic (CML)-based standard cell applications. The presented circuit concepts for differential logic gates are restricted to the CMOS design approach and comply with the standard cell design flow. The respective design flow extension enables the layout generation of such circuits. A standard cell-based solution is proposed to obtain in-parallel routes of differential signal pairs for technologies with a low number of usable routing layers (here: three). Moreover, NRE costs for cell and library design are kept as low as possible by a more modular development approach.

#### **Contribution to Robust Radiation-hardened Circuits**

The Thesis proposes new circuit concepts for radiation-tolerant cells, robust Triple Modular Redundancy (TMR)-based gates and discusses the corresponding impact on the design flow during design generation. The novel cells are based on the initial idea and circuit arrangement of  $\Delta$ TMR presented in [16]. Therein, these memory cells are equipped with integrated filters ( $\Delta$ ) for transient mitigation on the data path. The circuit proposals in this work present many novel distinctive  $\Delta$ TMR flip-flop configurations with significant improvements in performance (power, area, and delay), functionality, and robustness against radiation. These cells are essential for a portfolio when radiation-hardeningby-design Application Specific Integrated Circuit (ASIC) design is targeted. They have complementary features, allowing to meet various requirements in realistic applications.

The following cell developments are proposed:

- robust transient filter standard cells for critical net protection

- novel baseline  $\Delta$ TMR flip-flops with:

- high-density layouts for area savings

- an improved robustness to heavy ions up to  $62.5\,\mathrm{MeV\,cm^2\,mg^{-1}}$

- low-area overhead and a short propagation delay

- novel robust  $\Delta$ TMR clock-gate to enable clock-gating function to save power

- novel  $\Delta$ TMR flip-flops with:

- full scan-test support to improve the testability of a design

- self-correction function to correct internal errors without clock activity.

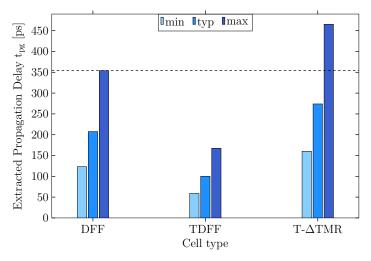

All new  $\Delta$ TMR flip-flops are characterized by better quality of results in terms of power, area, and delay overhead compared to recent existing solutions in the same 130 nm technology. The configurations have been developed with the use of their internal logical scheme divided into separate sections. Moreover, the robustness of selected candidates is finally confirmed by irradiation measurements.

#### **1.4 Publications Related to this Work**

In the context of this work, six papers have been published with the author of this Thesis as first author in recent years. The publications listed below already give an overview of the entire picture of this Thesis.

A design methodology for standard cell-based CML circuits together with the proposed 2-Phase routing approach is published in [17]. It allows to generate digitally-designed differential bipolar-based circuits with in-parallel routed differential signaling.

[17] O. Schrape, M. Herrmann, F. Winkler, and M. Krstić, "Routing Approach for Digital, Differential bipolar Designs using Virtual fat-wire Boundary Pins," in 20th IEEE International Symposium on Design and Diagnostics of Electronic Circuits & Systems, DDECS 2017, Dresden, Germany, April 19-21, 2017, pp. 122–126, 2017.

The challenges with respect to characterization of the proposed  $\Delta$ TMR flip-flop standard cell gates are discussed in [18].

[18] O. Schrape, A. Breitenreiter, S. Zeidler, and M. Krstić, "Aspects on Timing Modeling of Radiation-Hardness by Design Standard Cell-Based  $\Delta$ TMR Flip-Flops," in 2019 22nd Euromicro Conference on Digital System Design (DSD), pp. 639–642, Aug 2019.

An example for demonstration purposes of the applicability of the design methodology for RHBD circuits is published in [19]. The proposed methodology is described and applied to the digital part of an AMS design.

[19] O. Schrape, A. Breitenreiter, L. Lu, E. P. Garcia, and M. Krstić, "Mit konventioneller Technologie zum strahlungsharten AMS-Design," in *Workshop Testmethoden* und Zuverlässigkeit von Schaltungen und Systemen, 2021.

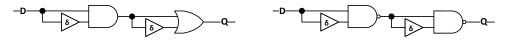

An alternative circuit concept for radiation-hardened D-flip-flops with the use of D-latchbased standard cell gates is published in [20]. The radiation-hardness is confirmed by irradiation measurements.

[20] O. Schrape, A. Breitenreiter, C. Schulze, S. Zeidler, and M. Krstić, "Radiation-Hardness-by-Design Latch-based Triple Modular Redundancy Flip-Flops," in 2021 12th IEEE Latin American Symposium on Circuits and Systems, 2021.

The performance of a  $\Delta$ TMR -based flip-flop is significantly improved with the use of fast True Single-Phase Clock (TSPC) flip-flops. The TSPC cells are used for triplication inside the  $\Delta$ TMR cell as proposed in [21]. Thus, the introduced delay by  $\Delta$ TMR and its area overhead are reduced.

[21] O. Schrape, M. Andjelković, A. Breitenreiter, A. Balashov, and M. Krstić, "Design Concept for Radiation-Hardening of Triple Modular Redundancy TSPC Flip-Flops," in 2020 23rd Euromicro Conference on Digital System Design (DSD), Aug 2020.

One of the recent key papers was published on the IEEE Transaction on Circuits and Systems I Journal. It summarizes the main contribution of the design methods and the evaluation of radiation-hardened TMR standard cell flip-flops.

[22] O. Schrape, M. Andjelković, A. Breitenreiter, S. Zeidler, A. Balashov, and M. Krstić, "Design and Evaluation of Radiation-Hardened Standard Cell Flip-Flops," *IEEE Transactions on Circuits and Systems I: Regular Papers*, pp. 1–14, 2021.

Finally, two patents and one pending patent application are closely connected to this Thesis. They are mentioned here in order to underline commercialization aspects of two out of three proposed circuit concepts for self-correction in RHBD TMR-based memory cells.

One solution for data recovery is achieved by open slave latch compositions, which form the self-corrected feedback together with the evaluated output of the voter. In addition, this feedback is connected to an internal second transient filter.

[EP3965296A1/US11527271B2] O. Schrape, A. Breitenreiter, F. Vater, and M. Krstić, "Self-correcting Modular-Redundancy-Memory Device," Sep. 2022/Dec. 2022.

Alternatively, the feedback is formed by distributed Guard-Gate (GG) components which realize the voter function and calculate the required internal feedback signals in parallel.

[EP20194684.5] O. Schrape, M. Andjelković, A. Breitenreiter, and M. Krstić, "Corrigible Comparator for Triple Modular Redundancy Cell," filed in Sep. 2020.

### 1.5 Structure of the Thesis

The structure of the thesis is as follows:

**Chapter 2** summarizes the technical background related to this Thesis. It starts with a technology overview, the main tasks for standard cell library development and for the digital design of VLSI circuits. Moreover, an overview of signal integrity, radiation effects, differential signaling, and hardware redundancy is given.

**Chapter 3** presents the related work for differential logic design and RHBD circuit solutions. The design flow, and cell concepts are presented therein. Moreover, concepts of single-event effect mitigation and the recent robust flip-flop circuit concepts are presented. The chapter concludes with a discussion of the open issues addressed in this Thesis to obtain RnRSs.

**Chapter 4** introduces the library concept and the respective modular standard cell concepts for differential logic design. The related design methodology with its standard digital design flow extension for reliable applications with differential-signaling is presented. The focus is set on the library development, from cell design and modeling enabling a compliant usage within the standard design flow tool chain. Another aspect is the reduction of the power consumption during design generation. A third one is the objective to enable the in-parallel routing of the differential signal pairs for reliability purpose.

Chapter 5 presents novel standard cell concepts and discusses the proposed design methodology in order to obtain RHBD circuits with the use of a standard semiconductor technology. Both traces together enable the robustness of later applications by radiation effect mitigation. Architectures for transient mitigation cells and novel more complex RHBD- $\Delta$ TMR standard cell flip-flops are proposed to be robust against radiation-induced resulting bit-flips. The circuit schemes and the introduced overhead in terms of area occupation, power and delay are discussed in detail.

**Chapter 6** presents the experimental results from the evaluation of the concepts for both types of hardware systems. The applicability of the methodology for reliable differential logic design is demonstrated on a high-speed part of a clock generator circuitry with the use of the proposed cell concepts and design methodology. The results are extracted from the implementation of the obtained routing solution of this differential design. Afterwards, the novel  $\Delta$ TMR cell concepts are evaluated in test vehicles for electrical verification and irradiation campaigns. The radiation-hardness of the new cells is confirmed by irradiation measurement tests. Selected  $\Delta$ TMR cell configurations are compared to the unhardened reference cells in terms of the key criterion, such as area, power/energy, and delay overhead. This Chapter then concludes with the implementations of two realistic design examples for space applications. They have gone through the proposed design flow for standard cell-based RHBD circuit design. The usability of the methodology and the introduced overhead by the hardening-approach is also discussed.

Chapter 7 summarizes the main results and gives an outlook on future work.

## Chapter 2

# Background

This Chapter is about the closely-related technical background important for this work. In particular, standard cell development, the standard cell-based digital design flow, and an overview of signal integrity and radiation-induced effects are given.

### 2.1 Semiconductor Technologies

Semiconductor foundries provide technologies in different nodes for various application fields. They offer Process Design Kits (PDKs) which contain the essential information and technology-related data for ASIC design with the use of modern CAD tools. A PDK typically consists among other things of parametrized cells (PCells) for active and passive devices, technology data and different views of the cells (e.g., layout representation), verification decks with respective rule files, devices models, and often several metal-stack options. Moreover, standard cell libraries or special IPs are provided to benefit from design reuse to enable the design of more complex VLSIs and SoCs. In addition, some of nowadays silicon CMOS technology foundries also offer radiation-hardened technologies or libraries as a platform for space application development [13], or [14]. This approach is also referred to as Radiation-Hardening-by-Process (RHBP), which is a commercially attractive design solution to cope with radiation effects. On the other side, special RF-PDKs are also available on the market which offer additional devices and/or models to improve the performance of the RF or mixed-signal (MS) circuit.

As an alternative, standard semiconductor technologies can be used instead for the design of reliable and robust hardware systems. They do not offer special devices or process features and are therefore also attractive with respect to design costs. For the evaluation of the proposed concepts and design methodologies in this work, the following standard technologies are selected:

**SGB25V** The implementations and experimental analyses for the differential logic design concepts and design methodology are evaluated with the SGB25V technology of IHP. This is a low-cost 250 nm BiCMOS process. The metal stack of this technology

offers three thin and two thick metal layers. This is a larger-scaled process with 2.5 V core logic and 3.3 V IO-logic CMOS devices. The performance of the devices of the bipolar module is for  $f_T=75$ , and for  $f_{max}=95 \text{ GHz}$  respectively.

**SG13S** The evaluation for RHBD applications is done with the use of IHP's highperformance 130 nm silicon-germanium SG13S technology. It is characterized by 1.2 V low-power core logic CMOS transistors and 3.3 V IO-CMOS devices. The bipolar module of this technology offers npn-HBTs with cut-off frequencies up to an  $f_T$  of 250 GHz and an  $f_{max}$  of 340 GHz. The metal stack allows to use five thin and two thick metal layers for implementation. The technology is commercially-qualified and radiation-assessed [23]. Moreover, the provided digital standard cell library is robust against Single Event Latchup (SEL) up to a Linear Energy Transfer (LET) of 67 MeV cm<sup>2</sup> mg<sup>-1</sup> [24].

### 2.2 Standard Cell Library Development

The Thesis is closely related to the design of standard cell-based ICs. As a consequence, the main design steps of the standard cell library development are discussed in this Section. An overview of the general procedure, the generation of abstract layout representations, and the standard cell characterization are addressed. The result of this task is a standard cell library with all essential views (e.g., layout, timing and behavioral models), ready to use for the design generation using the standard digital design flow. This development process is discussed in the context of Cadence Design Systems CAD tools.

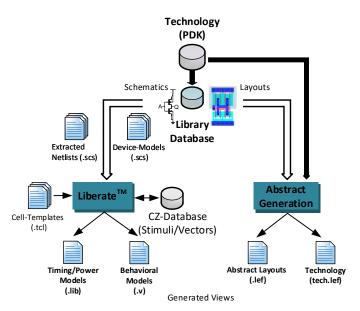

#### 2.2.1 View Generation Procedure

The initial input for the view generation procedure are the layout view and the transistorlevel circuit scheme (i.e., schematics in the following) of every cell of the library to be prepared. The cell layouts of the library database are verified to the design rules, i.e., Design Rule Check (DRC), defined by the selected technology and rule files provided by the PDK. Moreover, the netlist of the cell schematics is compared to the respective layout representation counterparts in a layout versus schematic (LVS) check. Afterwards, all devices, the parasitic capacitances and resistances are extracted for each cell to an analog simulation netlist (here: Spectre .scs-file). These files contain the connectivity of the cells at transistor-level. Together with the models of all devices, more accurate power and timing values can be obtained from later standard cell characterization.

Similarly, as for the schematics, an abstract physical representation view of the detailed layout of every cell has to be generated. These views contain the essential information used by Place and Route (PnR) tools for digital layout design generations. The result is an abstract layout view generated as a human-readable ASCII Layout Exchange Format (LEF) file (.lef) [25].

Both processes for the generation of necessary models/views are introduced in the next two subsections following the chart depicted in Figure 2.1.

Figure 2.1: Chart for standard cell library model/view generation

#### 2.2.2 Physical View

Place and route tools for digital design require layout information of all used cells and macros together with the provided technology information (e.g., tech.lef-file). In this file, all routing metal layers, vias (i.e., the "stairs" between two neighboring layers of the metal stack) and a subset of master layers (such as wells, or implants) are defined with their electrical and technology-related characteristics. This includes the capacitances, resistances, heights and current densities of all layers and vias. The layer definitions follow a strict routing grid G obtained by the respective routing pitch P, i.e., the distance between the centerlines of two adjacent wires. Thus, the pitch P is given by the metal layer width W and the *same-net* spacing S.

$$P_{layer} = W_{layer} + S_{layer}$$

(2.1)

Moreover, all layers are declared with preferred routing directions in the tech.lef-file. Based on the relation given in Eq. 2.1, several routing grids can be generated with the use of the minimum pitch or a multiple layer pitch definition. As a result, available routing tracks with preferred directions and empty routing channels can be derived and considered for routing solutions in later circuit implementations. In addition to the routing grids, the placement grid is defined as a multiple of the pitch in X and Y direction which is referred to a SITE in the LEF context. A *site* is the minimum possible step in micrometer a cell can be moved in X and Y direction. A LEF example for such a SITE definition for core cells is shown in Listing 2.1 on page 14.

All cells assigned to *site* CoreSite will be placed in the pre-defined rows in the core area of the chip. In the given example, they can be moved by  $0.5 \,\mu\text{m}$  in X direction and by  $3.78 \,\mu\text{m}$  in Y direction. Moreover, the cells can be flipped by default in both directions to improve the placement. This site definitions and many other technology

parameters (e.g., layer height and width) can be extracted in this technology LEF file, directly exported by the design environment used for the selected PDK.

Listing 2.1: A 1-row standard cell SITE definition

```

1 SITE CoreSite

CLASS CORE ;

SYMMETRY X Y ;

SIZE 0.5 BY 3.78 ;

END CoreSite

```

Similarly, the abstract layout information must be generated for every individual standard cell gate including the signal shape definitions of every used metal layer. Thus, the PnR tool is capable to find an efficient placement location of the cells and a suitable routing solution. The generation of this information is done with the use of a commercial abstract generation tool (see Figure 2.1).

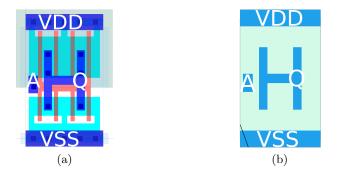

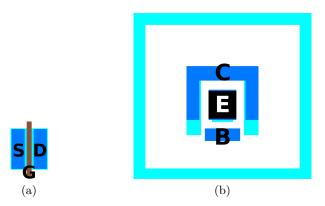

As an example, the detailed layout of an inverter is depicted in Figure 2.2 (a). It consists of shapes for gate drawings, contacts, metals, vias, wells, and active region. Based on this geometrical structure, the abstract view illustrated in Figure 2.2 (b) is generated.

Figure 2.2: Layout views of an inverter: (a) mask layout, (b) abstract layout

The shapes of all pins are extracted, i.e., the blue shapes in Figure 2.2 (a) for the signal A and Q, and for the special nets VSS and VDD respectively. A resulting H-structure is generated for pin Q, whereas a small rectangle shape is extracted for pin A. Particularly, both special nets have larger rectangles on the north and south side of the cell frame. These shapes limit the total cell width. They act as horizontal supply rails, immediately connected when the standard cells are placed next-to-next to each other in a row. Furthermore, the signal extraction can be controlled to consider the entire pin-shape connection below a pin or the individual pin-shape itself. This implicitly allows to control region and blockage definitions to prevent routing in these areas during implementation. Moreover, as indicated by a small triangle in the corner of the cell frame in Figure 2.2 (b), the default orientation of the standard cell is also specified. This is an essential information for cell flipping and rotation during the placement phase. For illustration purpose, an appropriate LEF representation of the inverter of Figure 2.2 is shown in Listing 7.1 in the Appendix on page 159.

However, with respect to the standard cell library preparation, the abstract layout views are generated from the detailed layout database of all standard cell library gates. As a consequence, a standard cell library is properly prepared for use in place and route phase with tools such as [26] during standard digital design generation. Nevertheless, even though cells can be placed and signals can be physically connected by the router, all cells have to be modeled similarly for their timing and power characteristics. Moreover, a behavioral model for every standard cell gate, which is taken as an input file for timing simulation in later design stages, has to be generated. Thus, the respective development tasks to obtain these essential views are introduced in the next section.

#### 2.2.3 Standard Cell Characterization

The standard cell characterization (CZ) is a high-effort task, which is the left branch of the view generation chart illustrated in Figure 2.1. This step can be manually done by scripting or by the use of commercial standard cell characterization tools or environments, such as, e.g., Synopsys PrimeLib solution [27], or Cadence Liberate<sup>TM</sup> [28]. The discussed procedures in this Section are aligned to the last tool.

Two of the main results of this step are timing/power models in terms of so called .libfiles (also known as Liberty<sup>TM</sup> files) and behavioral models in, e.g., Verilog<sup>®</sup> (.v) format. The .lib-files contain essential timing, power, area information, and logical function of each standard cell gate. They are used by other CAD tools for design tasks such as logic synthesis, and place and route. Their information is considered also during design and timing extraction for power analysis (PA) and Static Timing Analysis (STA). Thus, the design costs and the design overhead can be estimated. As a result, the timing for every pin of each mapped cell and timing path is calculated based on the connected load (fan-out) and input transition times. Moreover, the design is additionally checked for timing violations against the applied timing constraints such as clock periods, input and output delays, or minimum and maximum delays for specific paths. However, in order to have a good quality of results for STA and PA in later design phases, the essential information (.lib-files) needs to be generated accurately.

As can be seen in Figure 2.1, the transistor models (device-models), the pre-defined input cell templates (.tcl), and the extracted netlists of the selected gates are applied as input for the characterization tool. The templates cover global specifications with respect to Lookup Table (LUT) sizes in terms of dimensions for constraint definitions and delay measurements determining the number of automatically generated simulation vectors. Furthermore, additional information such as temperature ranges, model corner settings, and power supply voltage definitions can be specified. As an example, for the selected 130 nm standard technology introduced in Section 2.1, three digital process, voltage and temperature (PVT) corners are typically covered with respect to the low voltage MOS transistor models, i.e., min/fast (1.32 V at -40 °C), typ/avg/nom (1.20 V at 25 °C), and the max/slow (1.08 V at 125 °C) corner.

Based on that information, vectors are generated in order to characterize each cell in terms of delay, energy, leakage power, input capacitances, and timing constraints such as setup/hold, recovery/removal or min-pulse-width for constraint pins. The resulting CZ-database consists of several thousands of vectors and checking directives, which are executed in parallel, launching analog simulations invoked by the characterization tool. When all simulation runs have passed, the model files (.lib/.v-files) can be generated and used during design generation.

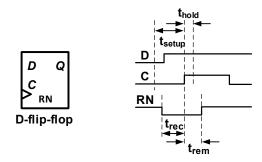

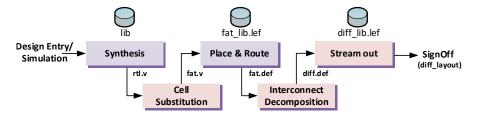

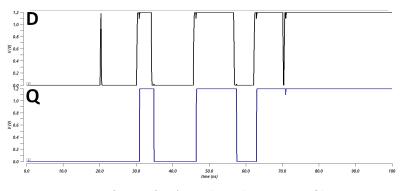

Nevertheless, the characterization of sequential cells such as flip-flops, requires some particular attention. One additional constraint is that the data must be stable before the sensitive clock edge arrives. This timing window is called setup time  $(t_{setup})$ . The counterpart window is the hold time  $(t_{hold})$ , in which the data must remain stable after the active clock edge has already occurred. Moreover, if a memory cell is equipped with asynchronous control signals, similar timing windows such as recovery time  $(t_{rec})$  and removal time  $(t_{rem})$  have to be considered additionally.

Figure 2.3 illustrates the most important timing windows of a rising-edge-triggered D-flip-flop with low-active asynchronous reset function. If one of these windows remains violated after implementation, the flip-flop can enter in a meta-stable state and might capture wrong intermediate data. Thus, the resulting output value (node Q, not shown here) is unpredictable and unknown.

Figure 2.3: Important timing windows of a rising-edge-triggered D-flip-flop

As a consequence, these windows have to be accurately calculated during the standard cell characterization task. The logical validation is done by comparison of an expected value to the obtained output value measured at a specified primary probe node Q.

When the CZ-setup and the templates are finalized, the characterization process is executed for all defined PVT corners and cells. The final resulting files, i.e., the timing/power models (.lib) and an appropriate behavioral model file (.v) are extracted. They are ready to use by other CAD tools for the design of standard cell-based applications. Nevertheless, the content of a .lib-file representation of an abstract D-flip-flop is given in the Appendix in Listing 7.2 on page 161.

#### 2.3 Digital Design Flow

As a result of increasing IC complexity over the past six decades – following Moore's Law – the development paradigm has changed from designing small circuits with a few components to a design generation with millions or billions of pre-designed logic gates. Thus, a design solution had to be found for design generation of such complex VLSIs and systems. As a consequence, the standard Digital Design Flow (DDF) has been established. One of the main changes of the paradigm is, that instead of explicitly stating sub-circuits of transistor arrangements to realize a desired function, the design behavior is done by an abstract behavioral description in a register transfer language. It allows to generate complex digital circuits with the use of pre-designed standard cell gates designed in a selected technology node. The flow has been adapted, extended and the related CAD tools have been simultaneously improved to support new technology nodes and design features. The overview of the DDF and its different design stages are illustrated Figure 2.4. Abstractly spoken for everyone, it seems to be mostly like a combination in usage of selected CAD tools in a specific order (design stages) to obtain standard cell-based VLSI.

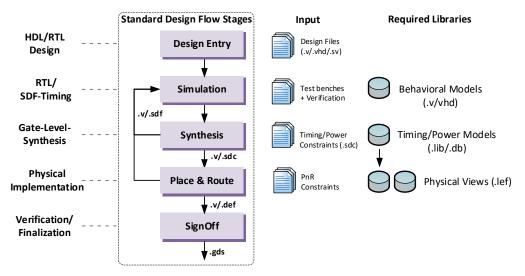

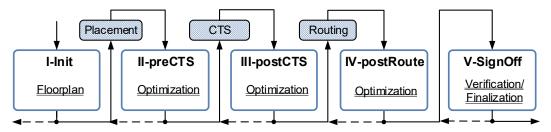

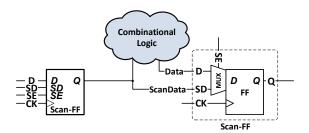

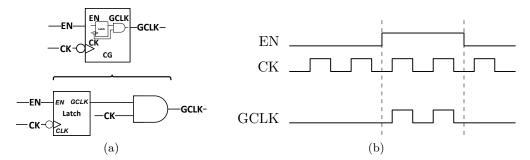

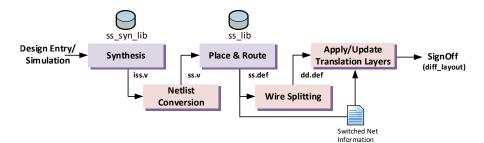

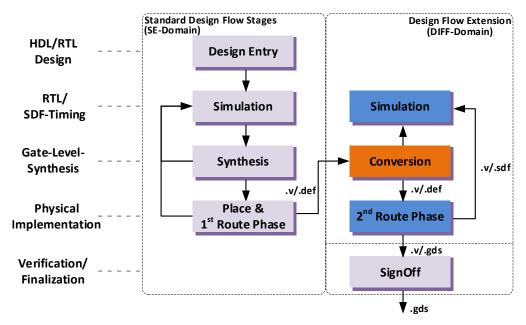

Figure 2.4: Standard digital design flow in a vertical arrangement

Finally, one result of the standard DDF is a mask set in binary GDS format which as the input for fabrication. As a consequence, this flow is also known as the RTL2GDS flow. The individual design flow stages (DF-stages) are introduced in the next paragraphs. A more detailed overview of the general design steps with the chosen tool chain of this work can also be found in the literature [29].

**DF-Stage 1 – Design Entry** At this stage, the design behavior is described in RTL according to a design specification with the use of hardware description languages (HDLs), such as VHDL, Verilog®, or System-Verilog®. The functionality can be written in technology-unrelated or technology-related manner. Moreover, the behavior can be described in structural and behavioral styles.

**DF-Stage 2 – Simulation** This stage is a continuously repetitive and can be performed after any other design flow stage. Herein, the functional behavior is verified by simulation with the use of HDL simulator environments. The informative value of the simulation and its functional coverage fully depend on the quality of the applied test benches with their stimuli. If the input of a simulation is a pure RTL design, the simulation is called RTL behavioral simulation. Alternatively, if the input is a technology-dependent netlist file, an ideal Gate-Level simulation is started. Moreover, if extracted timing (e.g., an .sdf-file, standard delay format (SDF)) from other design stage such as logic synthesis, or place and route is additionally applied, the simulation is referred to as SDF-Timing Simulation. Nevertheless, the behavior model of each used master component of the design has to be applied to the simulation environment in order to obtain a correct simulator setup.

**DF-Stage 3** – **Synthesis** In a third stage, the HDL source files of the functionallyverified design are analyzed and compiled by an HDL Compiler of a logic synthesis tool. As a result, a technology-dependent gate-level netlist is finally obtained. Within this work, the different synthesis steps are reduced to two parts, i.e., RTL-Synthesis and Gate-Level Synthesis (GLS) step.

During RTL-Synthesis, the analyzed design and its behavior are transformed into a generic, technology-independent netlist. The Boolean equations are solved and realized by interconnecting multiple generic gates. Any sequential description is mapped to a generic memory cells. All explicit hard-macro IP instantiations are directly mapped to their respective model representations. However, no technology information such as timing, area, or power is annotated to the design. At this stage, the design is just prepared for technology mapping and Boolean optimization.

In the next phase (Gate-Level Synthesis), the generic netlist scheme is mapped to the applied technology. The timing and power information of all objects is provided in the pre-characterized model files (see .lib in Section 2.2.3). Furthermore, design rule constraints, power and timing constraints are set by respective SDC or TCL commands. As a result, the design is realized with standard cell gates and IP blocks in the target technology. Afterwards, timing and power are extracted for the design. Thus, all paths are annotated with their respective delays and every violated path or design rule can be optimized incrementally. When all constraints are met, the design parameters in terms of number of gates, area occupation, power estimation, and timing budget can be extracted and analyzed. The gate-level Verilog® netlist (.v-file) is finally exported together with the obtained timing in SDF (.sdf-file). Both output files are taken as input by the design simulator for a post-synthesis SDF timing simulation. When all timing simulations have passed, the layout generation of the synthesized gate-level netlist can be started.

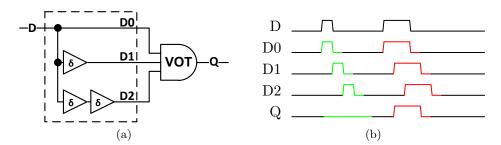

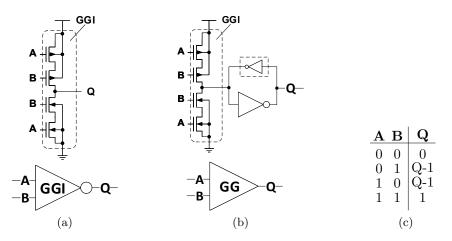

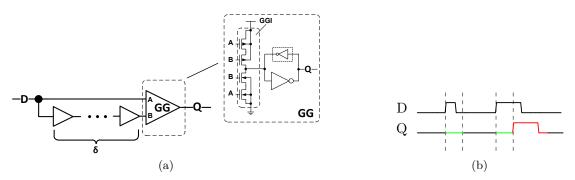

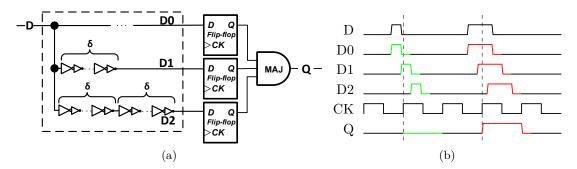

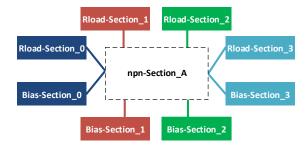

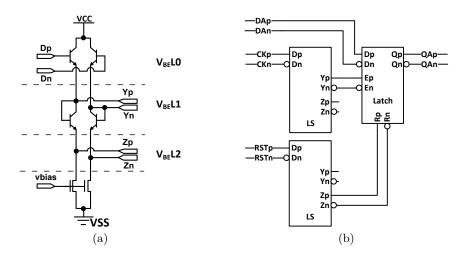

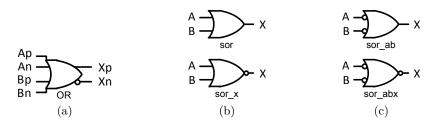

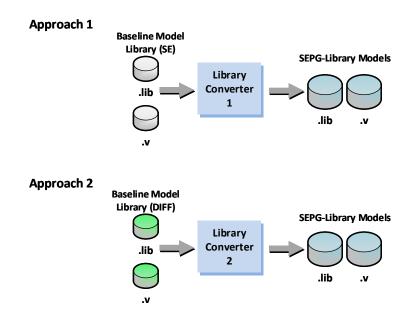

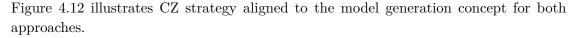

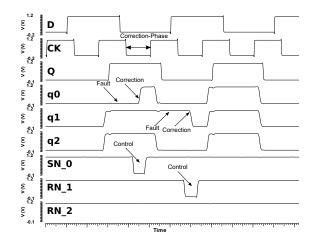

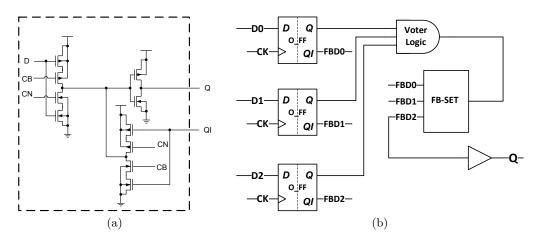

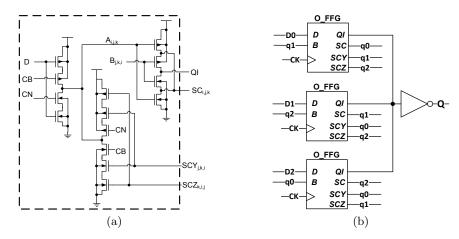

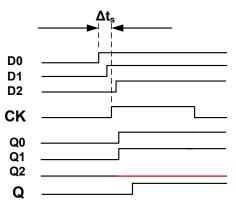

However, one hard limitation has to be considered with respect to the design of reliable and robust hardware systems in this work. Nowadays most popular logic synthesis tools such as Design Compiler [30] or Cadence Genus Synthesis Solution [31] support classical well-known single-ended signaling<sup>1</sup>. Interestingly, a single-ended signaling of differential logic gates was still supported in the early 1990's. As a consequence, and in advance, when differential logic design is addressed for the design of RnR hardware systems, additional effort is required in order to enable the compliance to the design tools and the DDF to benefit from the strengths of modern logic synthesis tools.