# RESOURCE EFFICIENT COMMUNICATION IN NETWORK-BASED RECONFIGURABLE ON-CHIP SYSTEMS

Dissertation

zum Erlangen des akademischen Grades

Doktor-Ingenieur (Dr.-Ing.)

in der Wissenschaftsdisziplin

Technische Informatik

eingereicht an der Mathematisch-naturwissenschaftlichen Fakultät der Universität Potsdam

> von Philipp Mahr

This work is licensed under a Creative Commons License: Attribution - Noncommercial - Share Alike 3.0 Germany To view a copy of this license visit  $\frac{1}{1000} \frac{1}{1000} \frac{1}{$

Published online at the Institutional Repository of the University of Potsdam: URL http://opus.kobv.de/ubp/volltexte/2012/5991/URN urn:nbn:de:kobv:517-opus-59914 http://nbn-resolving.de/urn:nbn:de:kobv:517-opus-59914

#### Betreuer:

Prof. Dr. Christophe Bobda

#### Gutachter:

Prof. Dr. Christophe Bobda

Prof. Dr. Christian Haubelt

Prof. Dr. Dietmar Tutsch

#### Prüfungskommission:

Prof. Dr. Ulrike Lucke

Prof. Dr. Christian Haubelt

Prof. Dr. Christophe Bobda

Prof. Dr. Helmut Asche

Prof. Dr. Tiziana Magaria

Prof. Dr. Klaus Rebensburg

Prof. Dr. Torsten Schaub

Prof. Dr. Bettina Schnor

Prof. Dr. Michael Gössel

#### Eidesstattliche Erklärung

Hiermit erkläre ich, dass ich die vorliegende Dissertation selbständig verfasst und keine anderen als die angegebenen Hilfsmittel benutzt habe. Die Dissertation ist bisher keiner anderen Fakultät vorgelegt worden. Weiterhin erkläre ich, dass ich bisher kein Promotionsverfahren erfolglos beendet habe und dass eine Aberkennung eines bereits erworbenen Doktorgrades nicht vorliegt.

| Potsdam, den 11.06.2012 |                |

|-------------------------|----------------|

|                         | (Philipp Mahr) |

#### Danksagung

Sowohl für die finanzielle Unterstützung als auch für die Möglichkeit zum Austausch mit anderen Forschern bedanke ich mich bei der Deutsche Forschungsgemeinschaft (DFG), die das AMoC Projektes (Adaptive Multiprocessor-on-Chip) finanzierte.

Meinem Doktorvater Christophe Bobda danke ich für seine Unterstützung und die vielfältigen Entwicklungsmöglichkeiten.

Den weiteren Gutachtern Christian Haubelt, Michael Hübner und Dietmar Tutsch danke ich für die Bereitschaft meine Arbeit zu lesen.

Meinen Kollegen Ali Zarezadeh, Felix Mühlbauer, Kevin Cheng, Lars Middendorf und Robert Hartmann danke ich für die fruchtbare Zusammenarbeit und Hilfestellung bei den vielfältigen Problemen, die im Unialltag auftreten. Weiterhin gilt mein Dank Benjamin Andres, Steffen Christgau, Max Frohberg, Sebastian Fudickar, Martin Gebser, Kerstin Rießelmann, Jens Rohrlack, Christian Spruch und Sebastian Taube für die Unterstützung und Zusammenarbeit.

Christian Haubelt und Tobias Schubert danke ich für die wissenschaftliche Zusammenarbeit während und auch nach ihrer Zeit in Potsdam.

Besonderen Dank möchte ich Jasper Nöllner für die Korrektur und intensive Beschäftigung mit einem ihm fremden Forschungsgebiet aussprechen.

Schlussendlich danke ich meiner Familie, meiner Freundin, meinen Freunden und der Musik für die ununterbrochene Unterstützung.

#### Kurzzusammenfassung

Die Leistungsfähigkeit rekonfigurierbarer Rechensysteme steigt kontinuierlich und ermöglicht damit die parallele Ausführung von immer mehr und immer größeren Anwendungen. Die Vielfalt an Anwendungen macht es allerdings unmöglich ein optimales Kommunikationsnetzwerk zu entwickeln, welches die Anforderung jeder denkbaren Anwendung berücksichtigt. Die Performanz des rekonfigurierbaren Rechensystems sinkt. Das Kommunikationsnetzwerk ist jedoch nicht der einzige Teil des Systems, der Einfluss auf die Kommunikationsperformanz nimmt. Die Ressourcenverwaltung des Systems beeinflusst durch die Platzierung der Anwendungen die Latenz zwischen Kommunikationspartnern und die Kommunikationslast im Netzwerk. Kommunikationsprotokolle beeinträchtigen die Performanz der Kommunikation durch Daten und Rechenoverhead, die ebenso zu erhöhter Netzwerklast sowie Ressourcenanforderungen führen.

In einem ganzheitlichen Kommunikationsansatz wird nicht nur das Kommunikationsnetzwerk berücksichtigt, sondern außerdem Ressourcenverwaltung, Kommunikationsprotokolle und die anderweitige Verwendung vorhandener, temporär ungenutzter Kommunikationsressourcen. Durch Einbeziehung dieser Aspekte während Entwurfs- und Laufzeit und durch Optimierung unter Berücksichtigung der Kommunikationsanforderungen, wird eine ressourceneneffizientere Kommunikation erreicht. Ausführliche Evaluationen zeigen, dass eine ganzheitliche Betrachtung von Kommunikationsfaktoren, Verbesserungen von Performanz und Flexibilität erzielt.

#### Abstract

The constantly growing capacity of reconfigurable devices allows simultaneous execution of complex applications on those devices. The mere diversity of applications deems it impossible to design an interconnection network matching the requirements of every possible application perfectly, leading to suboptimal performance in many cases. However, the architecture of the interconnection network is not the only aspect affecting performance of communication. The resource manager places applications on the device and therefore influences latency between communicating partners and overall network load. Communication protocols affect performance by introducing data and processing overhead putting higher load on the network and increasing resource demand. Approaching communication holistically not only considers the architecture of the interconnect, but communication-aware resource management, communication protocols and resource usage just as well. Incorporation of different parts of a reconfigurable system during design- and runtime and optimizing them with respect to communication demand results in more resource efficient communication. Extensive evaluation shows enhanced performance and flexibility, if communication on reconfigurable devices is regarded in a holistic fashion.

#### List of abbreviations

**ASIP** Application Specific Processor

**ASMO** Average Size Module Only

**ASP** Answer Set Programming

**CFB** Configurable Function Blocks

**CLB** Configurable Logic Blocks

**CMC** Configurable Memory Controller

**CPLD** Complex Programmable Logic Devices

**DFT** Discrete Fourier Transformation

**DSP** Domain Specific Processor

**DyNoC** Dynamic Network-on-Chip

**EDF** Earliest Deadline First

**FFT** Fast Fourier Transformation

FPGA Field-Programmable Gate Arrays

**FSL** Fast Simplex Link

**GPP** General Purpose Processor

LMF Largest Module First

**LMO** Largest Module Only

LTF Largest Task First

**LUT** Look-Up Table

**MAC** Multiply-Accumulate

MPI Message Passing Interface

**NoC** Network-on-Chip

**PAL** Programmable Array Logics

**PE** Processing Elements

**PLA** Programmable Logic Arrays

**PLD** Programmable Logic Devices

**RD** Reconfigurable Device

**RCU** Reconfigurable Unit

**SMF** Smallest Module First

**SMO** Smallest Module Only

**SVD** Singular Value Decomposition

# Contents

| 1                               | on  | 17                                                                   |                                                                  |    |  |  |  |  |

|---------------------------------|-----|----------------------------------------------------------------------|------------------------------------------------------------------|----|--|--|--|--|

|                                 | 1.1 | Assum                                                                | aption and scientific challenges                                 | 20 |  |  |  |  |

|                                 | 1.2 | .2 Organization of thesis                                            |                                                                  |    |  |  |  |  |

| 2                               | Rec | onfigur                                                              | rable computing systems                                          | 24 |  |  |  |  |

|                                 | 2.1 | Abstract hardware architecture of a reconfigurable computing systems |                                                                  |    |  |  |  |  |

|                                 | 2.2 | Recon                                                                | figurable logic devices                                          | 25 |  |  |  |  |

|                                 |     | 2.2.1                                                                | From simple PLDs to FPGAs                                        | 26 |  |  |  |  |

|                                 |     | 2.2.2                                                                | Coarse-grained reconfigurable devices                            | 28 |  |  |  |  |

|                                 |     | 2.2.3                                                                | Reconfigurability                                                | 30 |  |  |  |  |

|                                 | 2.3 | Resour                                                               | rce management of reconfigurable devices                         | 31 |  |  |  |  |

|                                 |     | 2.3.1                                                                | Placement                                                        | 33 |  |  |  |  |

|                                 |     | 2.3.2                                                                | Temporal planning                                                | 34 |  |  |  |  |

|                                 | 2.4 | Interco                                                              | onnection networks and communication protocols of reconfigurable |    |  |  |  |  |

|                                 |     | device                                                               | s                                                                | 35 |  |  |  |  |

|                                 |     | 2.4.1                                                                | Bus-based interconnection network                                | 35 |  |  |  |  |

|                                 |     | 2.4.2                                                                | Networks-on-Chip                                                 | 36 |  |  |  |  |

|                                 |     | 2.4.3                                                                | Communication protocols                                          | 38 |  |  |  |  |

|                                 | 2.5 | Discus                                                               | sion                                                             | 39 |  |  |  |  |

|                                 | 2.6 | Chapt                                                                | er conclusion                                                    | 40 |  |  |  |  |

| 3                               | Sch | eduling                                                              | on NoC-based reconfigurable architectures                        | 42 |  |  |  |  |

|                                 | 3.1 | Basic                                                                | scheduler                                                        | 43 |  |  |  |  |

|                                 |     | 3.1.1                                                                | Placement                                                        | 45 |  |  |  |  |

|                                 |     | 3.1.2                                                                | Temporal planning                                                | 46 |  |  |  |  |

| 3.2 Integrated module selection |     | Integra                                                              | ated module selection                                            | 47 |  |  |  |  |

|                                 |     | 3.2.1                                                                | Module selection strategies                                      | 48 |  |  |  |  |

|                                 |     | 3.2.2                                                                | Extended scheduling algorithm                                    | 49 |  |  |  |  |

|                                 |     | 3.2.3                                                                | Evaluation                                                       | 51 |  |  |  |  |

|                                 | 3.3 | Reloca                                                               | ation of tasks                                                   | 54 |  |  |  |  |

|                                 |     | 3.3.1                                                                | Relocation strategies                                            | 55 |  |  |  |  |

|     |        | 3.3.2                                 | Extended scheduling algorithm                   | 57  |  |

|-----|--------|---------------------------------------|-------------------------------------------------|-----|--|

|     |        | 3.3.3                                 | Evaluation                                      | 57  |  |

|     | 3.4    | Influen                               | ice of dynamic placement on path length         | 61  |  |

|     | 3.5    | .5 Off-line spatial planning with ASP |                                                 |     |  |

|     |        | 3.5.1                                 | Problem solving                                 | 63  |  |

|     |        | 3.5.2                                 | Evaluation                                      | 65  |  |

|     | 3.6    | Chapte                                | er conclusion                                   | 69  |  |

| 4   | Reso   | ource e                               | fficient DyNoC architecture                     | 70  |  |

|     | 4.1    | System                                | architecture                                    | 70  |  |

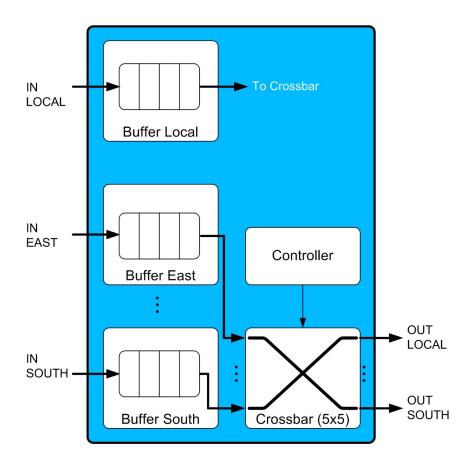

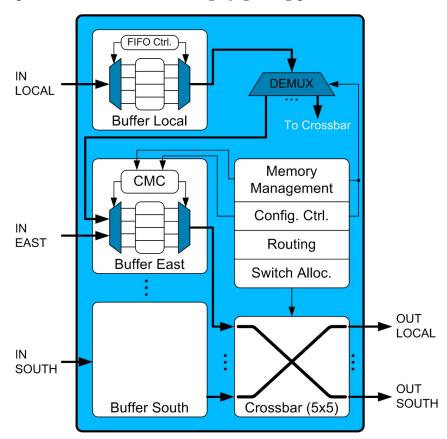

|     | 4.2    | Router                                |                                                 | 71  |  |

|     |        | 4.2.1                                 | Router Architecture                             | 72  |  |

|     |        | 4.2.2                                 | Evaluation                                      | 76  |  |

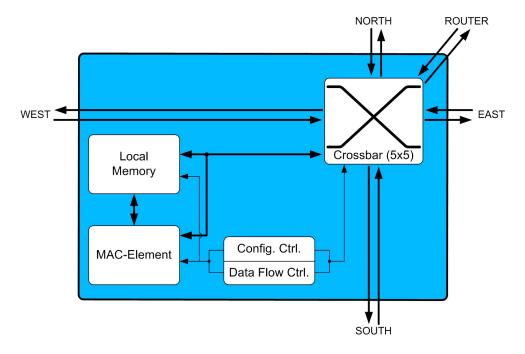

|     | 4.3    | Proces                                | sing element                                    | 80  |  |

|     |        | 4.3.1                                 | Architecture                                    | 81  |  |

|     |        | 4.3.2                                 | Evaluation                                      | 83  |  |

|     | 4.4    | Chapte                                | er conclusion                                   | 85  |  |

| 5   | High   | n-level                               | communication in reconfigurable on-chip systems | 86  |  |

|     | 5.1    | Structi                               | are and Functionality                           | 87  |  |

|     | 5.2    | Evalua                                | ${ m tion}$                                     | 89  |  |

|     |        | 5.2.1                                 | Benchmarks                                      | 89  |  |

|     |        | 5.2.2                                 | Case study                                      | 90  |  |

|     | 5.3    | Chapte                                | er conclusion                                   | 92  |  |

| 6   | Con    | clusion                               | and outlook                                     | 93  |  |

| Αι  | ıthor' | s Publ                                | ications                                        | 96  |  |

| Bi  | bliog  | raphy                                 |                                                 | 98  |  |

| Lis | st of  | Figures                               | 3                                               | 106 |  |

| Lis | st of  | Tables                                |                                                 | 108 |  |

#### 1 Introduction

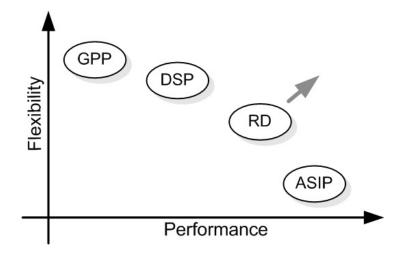

In 1971 Intel introduced the first commercial microprocessor with 2300 transistors, the Intel 4004. Since this historic release, transistor count on processors increased rapidly and doubled every two years, leading to today's high-end microprocessors like the Intel Xeon E7-8870 [37] with 2600 million transistors. The increasing amount of transistors integrated on one die led to the emergence of several processor classes providing different ways to process applications. Two main means to characterize different processors classes are *flexibility* and *performance* as shown for four common processor types in Figure 1 [33, 9].

Figure 1: Performance vs. Flexibility of processor classes

General Purpose Processors: General Purpose Processor (GPP) are able to compute any kind of task. The concept of a GPP was presented by John von Neumann [69] in 1945 and became the foundation of modern microprocessors. Computations are executed by a fixed (general purpose) data-path which carries out a stream of instructions to perform calculations sequentially (temporal computing). Because GPPs can execute any kind of algorithm, they trade flexibility for performance.

Domain Specific Processors: Domain Specific Processor (DSP) are tailored to a specific class of algorithms. Like GPPs they execute a stream of instructions but their datapath is optimized to increased performance for common operations of the algorithm class. A common DSP is the digital signal processor which is used for applications

involved in image processing, multimedia or telecommunication. The specialization of DSPs increases performance but does not allow the implementation of algorithms other than those for which it was optimized and therefore is less flexible.

Application Specific Processors: Application Specific Processor (ASIP) are even further tailored to specific applications compared to DSPs. The processor is designed for a particular application by implementing the application completely in hardware. No stream of instructions are present as the operations of the application are implemented in hardware directly, allowing for optimized (parallel) execution compared to GPPs and DSPs. While ASIPs do use spatial computing and therefore offer high performance they are only usable for the one application they are designed for, thus having very limited flexibility.

Reconfigurable Devices: A Reconfigurable Device (RD) allows adaption to the application during runtime by modifying its spatial structure. The RD is customized to a particular application containing only the needed operations, therefore reaching performance close to ASIPs. Unlike a static ASIP modifying the spatial structure of the RD by loading new configurations during runtime is similar to loading new software modules onto a GPP and enables RDs having flexibility close to GPPs.

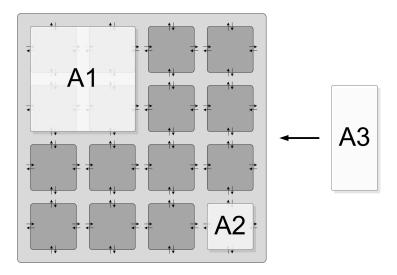

While GPPs offer a high degree of flexibility due to their ability to compute any kind of task, they do not offer much performance in contrast to the other processor classes. Flexibility is achieved by adapting the application to the hardware which subsequently runs through fixed stages like Instruction Fetch, Instruction Decode or Execution. In contrast, ASIPs offer high performance because they are optimized for a particular application and the hardware is adapted to the application. Due to the dynamic of loading new configurations on the RD during runtime and the adaption of the hardware to the application, reconfigurable devices can offer both flexibility and performance. A simplified view at the architecture of a reconfigurable device (see Figure 2) shows computational resources connected to an interconnection network (communication resources). While the computational resources needs to adapt to the applications' communication requirements, the communication resources need to adapt to the applications' communication requirements.

A general goal when designing a network for communication is to design it at minimum costs while still fully satisfying performance requirements [13]. So, in the design of interconnection networks the applications' communication requirements like the number of

Figure 2: Reconfigurable device with computational resources (dark gray) and communication resources (light gray) with two loaded applications A1 and A2 and a not yet loaded application A3.

communication partners, bandwidth or latency are of major interest in order to design a network which achieves high performance [17]. However, the mere diversity of applications deems it impossible to design an interconnection network matching the requirements of each and every application perfectly hence leading to suboptimal performance from the start.

On RDs efficient communication cannot be achieved when relying solely on the design of the interconnection network architecture. Communication protocols affect performance by introducing data and processing overhead producing higher network load and resource demand, but offering increased flexibility on the other hand. Applications can be positioned freely on the RD. The location were an application is placed on the RD in respect to its communication partners (like peripherals) has influence on the performance of both the interconnection network and the application. Longer communication paths lead to longer latencies and an (overall) higher network load [1]. So, communication at runtime need to be considered in order to achieve efficient data exchange between communication partners. Furthermore, the high resource and area demand of flexible interconnection networks on RDs limits resources available to speed-up computations thus impacting performance of applications.

Approaching communication holistically considers not only the architecture of the interconnect, but also (i) communication-aware resource management, (ii) communication protocols and (iii) resource usage just as well. By incorporating different parts of the reconfigurable system during design- and runtime with respect to communication requirements, a resource efficient communication can be achieved.

#### 1.1 Assumption and scientific challenges

The following thesis states the goal of my work.

By optimizing resource management and usage of communication protocols and network resources, and by incorporating these into the applications' communication requirements, resource efficient communication can be achieved. It can be shown, that this holistic communication approach leads to higher performance and flexibility of network-based reconfigurable systems compared to approaches focusing solely on the architecture of the interconnection network.

Confirming this thesis is done in three parts considering different aspects of resource efficient communication. Extensive evaluation will show that performance and flexibility enhancements can be reached with the help of the concepts and techniques developed here.

#### Communication-aware resource management

Resource management of the RD at runtime is an important aspect of the reconfigurable systems and is similar to the parts of an operating system managing the underlying system resources. On a RD, the resource manager determines when (temporal planning) and where (spatial planning) to execute an application, which directly influences system performance. A simulator of an on-line runtime manager is presented and several optimizations are evaluated with regard to device utilization and communication distance (Chapter 3).

#### Dynamic Network-on-Chip architecture

It is not possible to design a runtime manager without a deeper understanding of the targeted reconfigurable architecture. In this part, the implementation of a Dynamic

Network-on-Chip is presented. The reconfiguration capabilities of the architecture are evaluated and methods to enhance flexibility and performance by using the available communication (and computational) resources are given. An FPGA-based prototype implementation allows detailed evaluation of the proposed methods (Chapter 4).

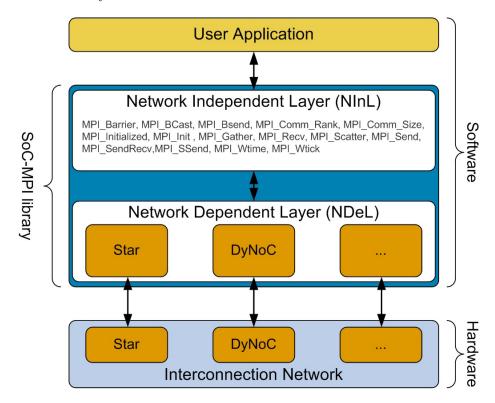

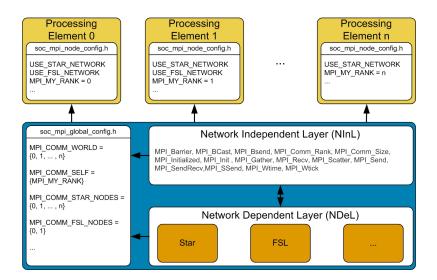

#### Communication protocol

Up until now primarily hardware-based implementations of applications for the used reconfigurable architecture were considered. Finally, the view on the system is broadened by extending the Dynamic Network-on-Chip architecture to support GPPs allowing applications to be constructed from software and/or hardware. For efficient communication between applications running on GPPs a high-level communication protocol is adjusted to the requirements of reconfigurable network-based multiprocessor systems on-chip (Chapter 5).

All these partial aspects show, that enhancements in flexibility and performance can be achieved through a resource efficient communication approach. The above aspects face several challenges to be solved.

#### Problems and challenges in communication-aware resource management

The dynamic behavior of loading new configurations on the RD during runtime has influence on the devices' free space, utilization, network load and fragmentation. With the overall goals being the maximization of acceptance of applications and the minimization of communication distance, methods for optimizing on-line temporal and spatial planning need to be found and evaluated.

Communication-aware temporal and spatial planning uses methods to approximate the path between sender and receiver on network-based RDs. Depending on the configuration of the device, the concrete communication path from sender to receiver changes during runtime, e.g. due to another application loaded in between sender and receiver. The precise path need to be considered to get information about realistic communication demands and to evaluate the quality of dynamic routing.

Spatial resource planning uses approximation algorithms to find solutions, because the planning problem is NP-hard. In order to evaluate the quality of the approximation al-

gorithm, the optimal solution need to be known for comparison. Due to the complexity of the problem it is not possible to calculate the optimal solution in most cases. The challenge is therefore to find the best possible solution in a feasible amount of time.

#### Problems and challenges in Dynamic Network-on-Chip architectures

In Dynamic Network-on-Chip architectures, efficient resource usage is of major interest. Configurations covering both computation and network resources result in suboptimal resource usage as network resources remain unused when covered by a configuration. The challenge here is to find methods to utilize the network resources inside a configuration and to achieve an optimal cooperation in terms of computation and communication. These methods have to be implemented in order to evaluate their operability.

#### Problems and challenges in Communication protocol

For multiprocessor systems, like super computers, many widely accepted communication protocols exist. An adaption to on-chip multiprocessor systems is obvious, as the communication requirements are similar. However, the adaption of communication protocols to on-chip multiprocessor systems is not straight forward as system abilities differ. Compared to multiprocessor systems, resources of on-chip systems are limited. Especially on-chip memory are sparsely available and the performance of on-chip processors is lower compared to the performance of processors in a multiprocessor system. The task at hand is to develop a communication protocol with low memory footprint and computational overhead.

## 1.2 Organization of thesis

The rest of this thesis is organized as follows. Chapter 2 introduces the abstract resource model for adaptive on-chip multiprocessor systems used in this paper. In order to understand reconfigurability a brief introduction to relevant state-of-the-art reconfigurable devices, interconnection networks and resource managers is given. After this introductory chapter, the following chapters are devoted to resource efficient communication. First of all, in chapter 3 the implementation of an on-line resource manager is presented and methods to enhance performance and flexibility, specifically integrated module selection and

relocation of tasks are evaluated. Furthermore, the results obtained by the on-line spatial planner are compared with an optimal (off-line) spatial planner. In chapter 4 the perspective is shifted from management of reconfigurable devices to the actual device itself. A resource efficient reconfigurable router is presented being usable as a network router as well as an additional resource for computation. Furthermore, an adaptive processing element for the calculation of the fast fourier transform algorithm is described. Processing elements of reconfigurable devices are not limited to pure hardware implementations like the processing element for the calculation of the fast fourier transform, but can also be implementations of general purpose processors. A communication protocol based on the message passing interface is presented in chapter 5, allowing flexible communication between programmable processors. Finally chapter 6 concludes this work and gives an outlook on follow-up research.

# 2 Reconfigurable computing systems

In this chapter the state of the art relevant for this work is given. Beginning with the description of an abstract hardware architecture for adaptive on-chip multiprocessor systems, different aspects of reconfigurable computing systems are introduced. Basics of resource management, reconfigurable logic devices, interconnection networks are covered and corresponding research work by others is presented.

# 2.1 Abstract hardware architecture of a reconfigurable computing systems

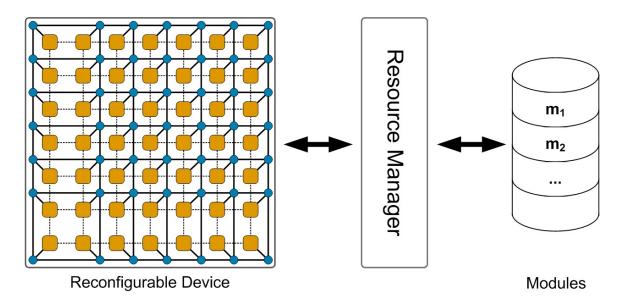

In this section the abstract resource model for a reconfigurable computing systems is described. Such a system needs to be able to (i) adapt to the application and (ii) execute several different applications simultaneously. Thus, the underlying hardware architecture needs to be able to change depending on the computational and communication demands and constraints of the applications. RDs offer the option to adapt the underlying architecture to the applications' needs. Applications or tasks are implemented by modules on a reconfigurable system.

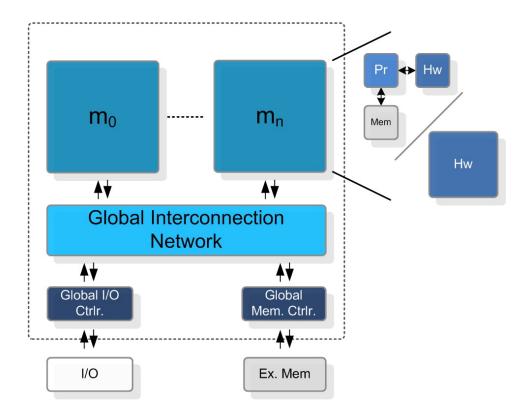

Modules consist of processors (Pr), memory (Mem), local interconnects and/or hardware accelerators (Hw). Each module has access to further global resources like peripherals (I/O) and external memory (Ex. Mem) like RAM, ROM or HDDs. Peripherals make data exchange between modules and the outside world available. UART, USB, Ethernet, WI-FI, Video I/Os, Audio I/Os or Digital Analog Converters are common examples of peripherals. Global resources are located around the RD to allow separate data storage and/or access to peripherals from independent modules.

Figure 3 shows several modules  $m_i$  on a RD. External memory and peripherals are arranged at the borders of the RD. Modules are interconnected using a global interconnection network and have access to all global resources. Note that it is possible to include I/O (I/O Ctrlr.) or memory controllers (Mem. Ctrlr.) inside a module to set up privileged access. In this case these resources are not available to other modules.

This abstract resource model is regarded as the base model of the reconfigurable computing architecture used in this thesis. The model is refined in following chapters and an actual architecture is presented.

Figure 3: Hardware infrastructure of a reconfigurable computing system with n + 1 modules

The following section gives an overview on reconfigurable logic devices in order to understand how such devices enforce reconfiguration on hardware level and how different approaches used by different reconfigurable devices deal with the involved issues.

## 2.2 Reconfigurable logic devices

The concept of reconfigurable computing was introduced by Gerald Estrin in the late 50s. The Fixed Plus Variable Structure Computer [24, 25] was the practical realization of this concept. It used a *fixed part* holding a general purpose processor, a *variable part* and a *supervisory control* part to coordinate operations between the fixed and the variable part. Configuration was done manually by replacing basic building blocks on the variable part. Two different types of building blocks were available: one for signal inversion, amplification or high-speed storage and the other one for combinatorics. Up to 36 building blocks could be inserted into the variable part and connection between them was done by a wiring

harness allowing the configuration of the Fixed Plus Variable Structure Computer. The technology at that time made the use of the Fixed Plus Variable Structure Computer difficult. A lot of effort was required to implement applications in the first place and to reconfigure the device manually later [9].

Over the last two decades, progress in the field of reconfigurable devices was amazing and reconfigurable computing is widely used. Numerous workshops and conferences deal with this topic [9]. Basically, reconfigurable logic devices belong in one of two classes — fine-grained and coarse-grained devices [33, 30].

Fine-grained reconfigurable devices like Field-Programmable Gate Arrays (FPGA) use single-bit Configurable Logic Blocks (CLB). Coarse-grain devices provide reconfiguration on function level using word-level Configurable Function Blocks (CFB). While fine-grain reconfigurable hardware has the benefit of high flexibility, coarse-grain reconfigurable hardware trades-off some flexibility for a potentially higher degree of optimization in terms of area and power. Coarse-grain architectures need significantly less time to perform reconfigurations and the amount of reconfiguration data is much lower compared to fine-grained architectures [33, 68].

#### 2.2.1 From simple PLDs to FPGAs

Programmable Logic Devices (PLD) like Programmable Logic Arrays (PLA)s, Programmable Array Logics (PAL)s, Complex Programmable Logic Devices (CPLD)s and FPGAs are commonly used devices when a flexible hardware structure is asked for [9]. All these devices belong to the fine-grained RD class.

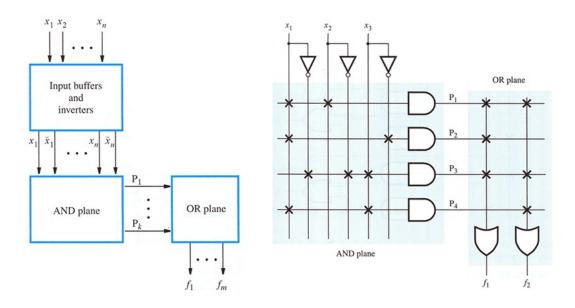

**PAL/PLA** PALs and PLAs are the simplest programmable devices and are used to implement combinatorial logic circuits. They can implement any boolean functions in a disjunctive form by connecting an AND-plane to an OR-plane (see figure 4).

PLAs were introduced by Texas Instruments in 1970 [5] and allow programming of both the AND- and OR-plane. In contrast, PALs (introduced in 1978 by Monolithic Memories) only feature programability of the AND-plane with the OR-plane being fixed, so making PALs a subclass of PLAs [9]. Both PLAs and PALs use fuses to cut connections according to the desired boolean function. To program the device once (and for all), fuses are blown after fabrication by using high currents (antifuse technology). The main drawback of PALs

Figure 4: Programmable Logic Array [38]

and PLAs is their limited capacity due to the quick growth of the AND- and OR-planes, depending on the amount of inputs to the planes.

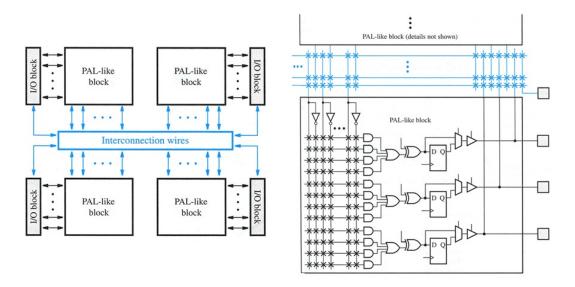

**CPLD** PALs and PLAs are only available in small sizes, equivalent to a few hundred gates. In order to create bigger circuits CPLDs can be used. CPLDs extend the concept of programmable AND/OR-planes by using additional I/O blocks and a programmable interconnect.

Figure 5 shows the structure of a CPLD using PAL-like blocks with additional registers, a programmable interconnect and I/O blocks. The registers, PAL-like blocks and I/Os can be interconnected freely. Areas, where CPLDs find common usage are power-up sequencing, system configuration, I/O expansion or interface bridging (glue logic). Many CPLDs have a non-volatile configuration memory, thus the CPLD can start processing immediately on start-up. However, these devices are still too small for applications requiring large gate counts.

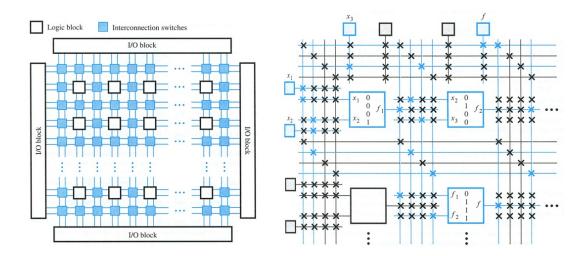

**FPGA** FPGAs were introduced in 1985 by Xilinx and can be used to implement applications requiring large gate counts. Similar to CPLDs FPGAs have I/O blocks and a programmable interconnect, but use CLBs <sup>1</sup> instead of PAL-like blocks (see Figure 6). The

<sup>&</sup>lt;sup>1</sup>CLB is a term used by Xilinx

Figure 5: CPLD structure [38]

configurable logic blocks consists of a set of logic cells which typically consists of a Look-Up Table (LUT), a one-bit register and a full adder. In contrast to CPLDs the programmable interconnect of FPGAs is of finer granularity connecting individual logic blocks instead of the large PAL-like blocks. There are different process technologies used for manufacturing FPGAs resulting in different types of programmability: one-time programmability, in-system programmability, and reprogrammability. FPGAs using SRAM-based process technology offer in-system reprogrammability, an important ability in order to perform (partial) dynamic reconfiguration.

State-of-the-art FPGAs furthermore have specialized functional blocks like memories, digital signal processing elements, fast I/Os, microprocessors or on-chip memory controllers. These blocks normally provide word-level functions like 32-bit wide on-chip memory or  $25 \times 18$  multipliers [75].

Large FPGAs, like the Altera Stratix-IV use more than 2 billion transistors [45] making them suitable to implement complex systems on chip.

#### 2.2.2 Coarse-grained reconfigurable devices

With FPGAs any kind of function can be implemented. This is possible because of the fine-granularity of the logic blocks and the flexible programmable interconnect which connects these blocks. The interconnect is also one of the main limitations of FPGA per-

Figure 6: FPGA structure [38]

formance, as it uses up to 90 % of the chip area [43]. Coarse-grained reconfigurable devices use word-level CFBs and therefore need less interconnections. CFBs are able to execute few operations like multiplications, additions or subtractions and there interconnection is realized with switching matrices or dedicated buses [9].

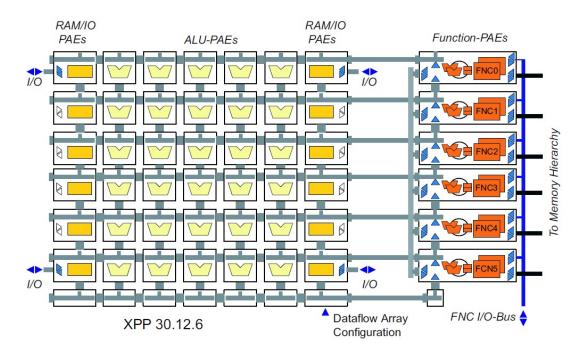

**Pact XPP-III** The Pact XPP-III [54] architecture is an example of a commercial coarse-grained reconfigurable architecture (Figure 7).

The XPP-III (eXtreme Processing Platform) core consists of an array of different processing array elements (PAEs) and a communication network for data and events. Function PAEs (16-bit general purpose processor kernels) are used to execute control-flow dominated irregular program code, whereas regular streaming algorithms like matrix transformation or FIR-filters are executed on the dataflow array of the architecture using ALU- and RAM/IO-PAEs. ALU-PAEs contain a configurable unit for basic arithmetic and logical operations. RAM-PAEs are very similar to the ALU-PAEs, but replace the arithmetic logic unit with a dual-ported SRAM and an I/O interface. Horizontal and vertical routing connections for point-to-point connections between PAEs are used with different data-width for data and events. Besides the horizontal and vertical connections an additional configuration network exists, which allows runtime reconfiguration of the PAEs. Configuration words are send to its correct row and column addresses, where they are stored in the configuration register of a PAE. When configuring only one PAE, one

Figure 7: XPP-III core structure [54]

configuration word is needed, but with the configuration of many PAEs a larger configuration word is required. Thus, the configuration time is equivalent to the amount of configuration words [53].

Many more coarse-grained reconfigurable architectures exist (see for instance [67, 49, 62, 22, 44, 14]). In [33] an overview of several architectures can be found.

#### 2.2.3 Reconfigurability

Some of the presented reconfigurable devices, especially SRAM-based FPGAs and coarse-grain architectures like the XPP-III, allow the implementation of tasks, like small video filters or complex video decoders, during runtime. The ability to reconfigure the chip during runtime enables the design of dynamically reconfigurable hardware systems that can adapt themselves to the current set of tasks for better performance. Further benefits of this capability are a reduced power consumption and a more efficient use of the available board space [72]. Tasks can be implemented using the whole RD (full reconfiguration) or only a part of the device (partial reconfiguration).

As an example for partial reconfiguration, consider an automotive infotainment system providing numerous services like audio and/or visual entertainment, video games, automotive navigation, location-based services or internet access. These tasks vary in computational and communication demand. Using a partial reconfigurable system allows execution of such tasks with high performance, while maintaining flexibility by implementing several different tasks in parallel. The system automatically adapts to the users' needs by reconfiguring the underlying hardware device with corresponding implementations of tasks [29].

In a partially reconfigurable device an Reconfigurable Unit (RCU) is the smallest fraction (or frame) available to be (re)configured. In the XPP-III RCUs are the ALU-PAEs and RAM-PAEs. This makes the XPP-III a heterogeneous RD consisting of different types of RCUs. Homogeneous devices on the other hand feature structurally identical RCUs. In FPGAs the size of a single RCU differs, depending on device family and size. In the Xilinx Virtex family FPGAs, a group of configurable logic blocks forms an RCU. The Virtex-2 FPGAs for instance allow partial reconfiguration of an array of 8 by 8 CLBs in XC2V40 devices and 112 by 104 CLBs in the XC2V8000. Meanwhile the newer Virtex-4 can be configured in 1 by 16 CLBs independent of the device's size [42].

In order to manage reconfigurations of the underlying resources a runtime resource manager is needed. Steiger et al. [64, 63] consider resource management the centerpiece of a reconfigurable operating system.

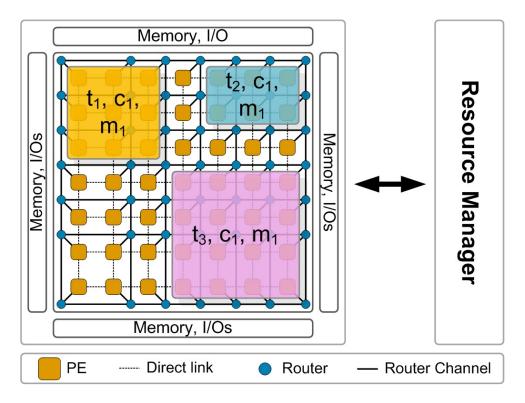

## 2.3 Resource management of reconfigurable devices

With the ability to execute several tasks simultaneously it is important to determine where the task should be placed on the reconfigurable device. This operation is called *placement* or allocation of resources. When considering timing constraints due to deadlines, either soft or hard, for the tasks has to be carried out in order to calculate the moment the tasks' execution is started *temporal planning*. However, the time at which tasks arrive is not known a priori. In Figure 8 the general architecture of a reconfigurable computing platform is shown.

The resource manager is needed to administrate the (re-)configurations of the RD according to incoming tasks and their requirements and consists of three parts: the *temporal* planner, the placer, and the loader implementing the task on the device.

Figure 8: Architecture of reconfigurable computing platform

Tasks are implemented by pre-synthesized modules which are the actual hardware situated on the RD. A start time can only be assigned to a task, if its module can be placed on the device and the task can be executed prior to its deadline. Therefore, a strong nexus between temporal planning and placement of tasks exists. Together, both placement and temporal planning steps are called scheduling in the course of this thesis corresponding to scheduling in operating systems. Application placement is an important aspect of scheduling in certain multiprocessor systems, like large-scale, shared-memory non-uniform memory access multiprocessors [12]. Thus, an interrelationship between scheduling on multiprocessor systems and reconfigurable devices exist. Yet, in multiprocessor systems tasks are often executed on several different resources (processors), while in reconfigurable devices all tasks share the same adaptable surface.

Scheduling can be done on- or off-line. On-line scheduling handles the tasks arriving one-by-one and the schedule is calculated based on the list of known tasks one after another during runtime. Only a subset of the whole task set is known which might result in suboptimal scheduling decisions. Off-line scheduling on the other hand considers the whole set of tasks and is therefore able to find optimal solutions. However, the off-line placement problem is already NP-hard.

#### 2.3.1 Placement

Most publications on managing the resources of RDs focus on temporal planning and/or placement. These papers can be divided into off- and on-line methods targeting homogeneous or heterogeneous reconfigurable devices. For the computation of task placements basically two steps are performed: (i) managing allocatable free space and (ii) finding a viable placement in this available space.

Bazargan et al. [6] take credit for being one of the first groups of authors to introduce on-line placement algorithms for two-dimensional homogeneous reconfigurable devices. Their algorithms partitions the free space and maintains a set of maximally free rectangles leading to a quadratic size of the set of free rectangles. A rectangle is chosen from the set of free rectangles by using a cost function considering the area of the free rectangles. The selected rectangle is then split into two smaller rectangles of free space which are added to the list of free rectangles. Alternatively, a method for partitioning the free-space into only O(n) rectangles using heuristics is proposed which in comparison gives worse results in terms of task rejections, if considering the same task set. Steiger et al. [64] improved the Bazargan's O(n) partitioner by delaying the split decision of the resulting free rectangles after a module has been placed. Handa and Vemuri [32] showed that free space in the form of maximal empty rectangles can be managed more efficiently by using the staircase data structure.

In [3] an algorithm considering routing-conscious placement is presented, which manages the allocatable space in  $O(n \log n)$  using plane sweep methods from computational geometry. The decision where to optimally place a module in the allocatable free space is calculated using weighted communication costs instead of computing the size of the free rectangles. Another approach to placement was presented by Eiche et al. [23]. By using a discrete hopfield neuronal network, an on-line placer for heterogeneous devices was implemented. The neural network outperforms the older SUF fit placement algorithm presented in [40].

When placing modules on a reconfigurable device the available free space becomes fragmented as tasks finish, which can lead to a higher rejection rate of tasks, even though the total amount of allocatable space is higher then the spatial requirements of an incoming task. [26] presents a defragmentation approach for one-dimensional heterogeneous reconfigurable devices in a no-break fashion. By copying one module at a time and then relocating the running computation to the copied module. Results highlighted that the presented approach leads to allocatable space up to 50% larger. In [61] Tabero et al. present a metric to estimate the degree of fragmentation of a reconfigurable device by analyzing the free space. Heuristics to decide when and how to perform defragmentation of the device are presented. In [66] this work is extended and the metric is used to implement a fragmentation-based heuristic to find a viable location in the available free space.

Danne and Stühmeier [19] introduced an off-line placement algorithm considering geometrical task variants. Tasks are modeled as three dimensional boxes constituted by their width, height and execution time. Modified heuristic methods from floorplanning are applied to select the task variants leading to better solutions for the placement problem. Belaid et al. [7] presented an off-line placer for heterogeneous devices formulating the placement problem as a constrained optimization problem taking task preemption and reconfiguration overhead into regard.

#### 2.3.2 Temporal planning

With execution time and deadlines of tasks, temporal planning becomes a necessity in order to fulfill timing requirements. In [64] different strategies for temporal planning are explored. Normalized planning considering both spatial and temporal aspects of tasks are combined with weighting coefficients and the optimal values of these coefficients are determined. Overall, best results are obtained when considering early deadlines first. Also a non-linear combination of deadline and task size had been considered, but resulted in worse outcomes. Danne et al. [18] considered off-line temporal planning of periodic real-time tasks and adapted the global Earliest Deadline First (EDF) approach used in real-time operating systems to homogeneous reconfigurable hardware devices. Two preemptive algorithms, EDF-First-k-Fit and EDF-Next-Fit, are presented and the influence of reconfiguration overhead was evaluated. Results show that reconfiguration times of smaller scale than task computation time causes only minor losses in performance.

# 2.4 Interconnection networks and communication protocols of reconfigurable devices

With placement and temporal planning of tasks at runtime it is not known a priori where and when a task is placed. It is important, that ongoing interconnections e. g. between modules of tasks and peripherals or external memories are kept and new interconnections are established. The communication infrastructure and protocols of RDs therefore have to be adaptive.

In [9] communication approaches were categorized depending on the way the communication is realized. Direct communication, communication over third party, bus-based communication, circuit switching and Network-on-Chip (NoC)-based communication are all feasible communication schemes for RDs. However, bus-based communication and NoCs are the dominant schemes in research communities [8]. While buses offer low latency, they do not scale well and are therefore a good solution for a limited number of modules only. NoCs provide far better scalability and are regarded the most viable solution for large chips using many modules, but introduce high and variable latencies [59]. Next, the implementation of a bus-bused interconnection network and NoC architectures is presented.

#### 2.4.1 Bus-based interconnection network

The RMBoC (Reconfigurable Multiple Bus-on-Chip) communication architecture targeting FPGAs is presented in [2]. Figure 9 shows the simplified architecture consisting of several switches locally attached to modules. Multiple segmented buses are used to connect the switches and allow each module to dynamically access the bus and establish communication with other modules (1-D circuit switching).

This slot-based communication approach is closely related to the reconfiguration capabilities of the Xilinx Virtex-2 architecture which allows 1-dimensional partial reconfiguration [56]. More recent FPGAs like Virtex-4 FPGAs allow tile-based partial reconfiguration and are therefore better suited for the implementation of 2-D communication approaches like with NoCs.

Figure 9: RMBoC architecture

#### 2.4.2 Networks-on-Chip

Several reconfigurable architectures using Networks-on-Chip as the main communication paradigm exist [55, 20, 35, 39, 10, 70]. A NoC is basically constructed from a set of routers relaying data from source to destination.

Devaux et al. [20] implemented a fat-tree NoC using dynamically reconfigurable routers called R2NoC. Each router contains a partial reconfigurable region which implements the dynamic communication links. Depending on the configuration of the reconfigurable region, the in and outputs are (statically) connected and a dedicated connection is established between source and destination modules using circuit switching.

Yet another NoC relying on circuit switching, is the PNoC [35]. In this design, each router has its own subnet. A collection of processing elements in each of those subnets allows frequently communicating tasks implemented by modules to be placed within the same subnet. The routers are implemented in a static manner and only their routing tables are updated as modules are removed or added.

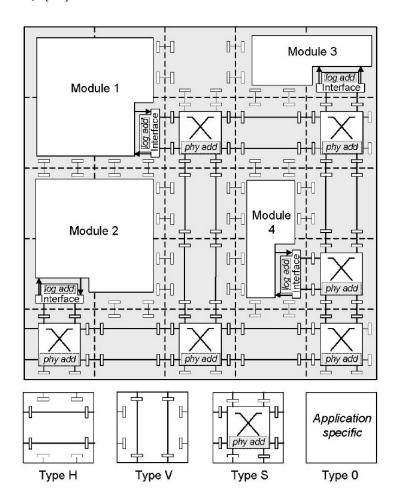

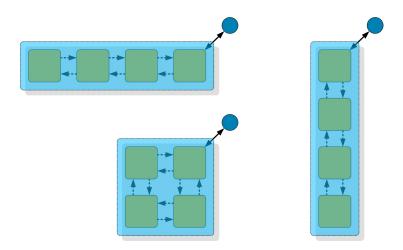

The configurable Network-on-Chip CoNoChi [55] uses virtual cut-through switching of packets. Routers have four equal full-duplex links connecting to the modules at the upper, lower, left and right side of the router. The RD is splitted into a fixed number of tiles which can be of one of four types. Figure 10 shows an exemplary configuration and the four tile types. The CoNoChi architecture makes placement of modules with different sizes possible. The communication infrastructure dynamically adapts and unused routers are deleted to decrease communication latency and to reuse computational and

communication resources previously occupied by routers. In contrast, the router resources of R2NoC and PNoC are static and cannot be removed. Thus, CoNoChi offers a higher degree of modularity [56].

Figure 10: CoNoChi architecture [56]

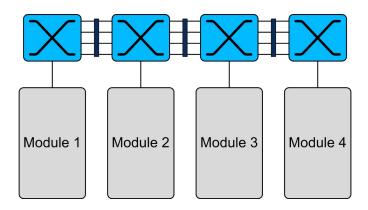

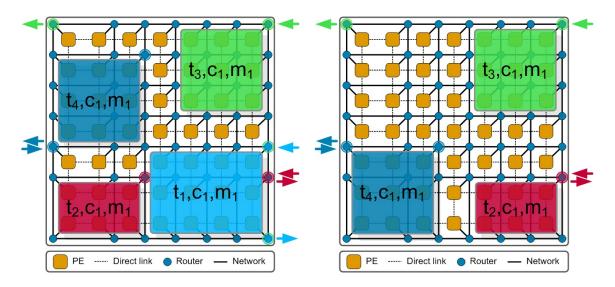

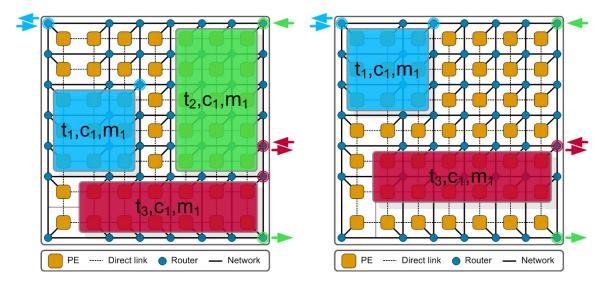

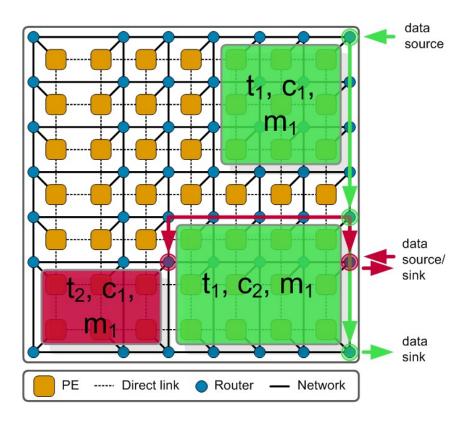

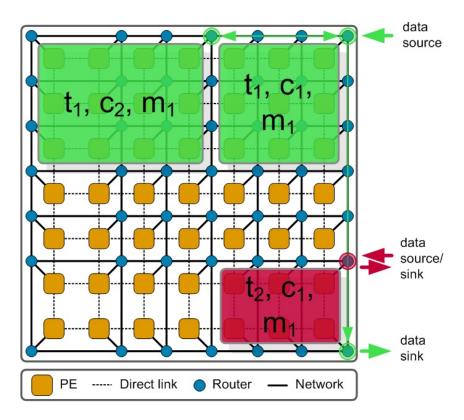

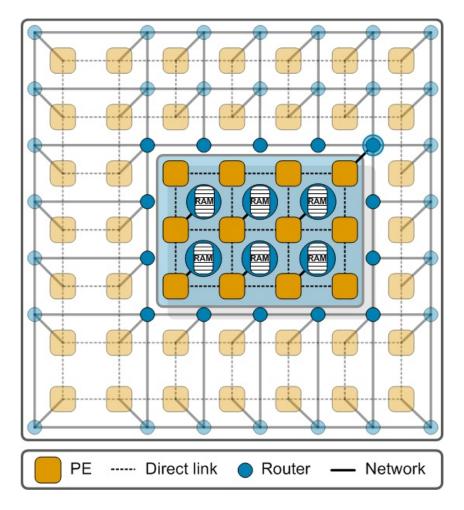

The Dynamic Network-on-Chip (DyNoC) architecture was presented by Bobda et al. in [10, 11]. The basic state without any modules placed appears and behaves like a normal network-on-chip consisting of Processing Elements (PE)s and routers. Processing elements access the network via corresponding routers. In contrast to a normal NoC, the PEs of the DyNoC can also communicate with their nearest neighbors using direct links. This allows the aggregation of several PEs creating a rectangular module to compute a complex task. PEs inside a module do not need to use the communication resources of the network in between for communication, but use their direct links instead. The advantage

of this hybrid communication scheme is a gain in flexibility. Figure 11 shows the DyNoC system architecture, whereas four modules from three different tasks are covering several PEs and routers.

Figure 11: DyNoC system architecture

## 2.4.3 Communication protocols

Closely related to the architecture of the interconnection network are communication protocols, which define the formats and rules for exchanging messages over the network. Protocols are implemented in hardware and/or software and cover one or more layers of abstraction. Different layers provide different services, like routing, flow control or synchronized communication. Research in this area mainly differs in its focus on particular layers.

The network layer S-XY dynamic routing protocol [11] for the DyNoC adapts routes between communication partners in order to surround obstructing modules in the path

of the packet. S-XY is implemented in the router of the DyNoC and operates in three different modes. In normal XY mode (N-XY), XY routing is applied. Packets are first send first send horizontally to the correct X-coordinate and then vertically to the Y-coordinate. Surround horizontal mode (SH-XY) is entered when an obstacle left or right of the packet needs to be surrounded. The last available mode is surround vertical (SV-XY) and is executed when an obstacle to the upper or lower direction is detected. Because modules are surrounded by a ring of router in a DyNoC it could be shown that with a very high probability S-XY routing is deadlock free by proving that there is always a path from the source of the packet to its destination and that the packet will reach its destination after a fixed number of steps [10]. Available work on high layer protocols often provides communication interfaces for applications [60, 46, 28]. Different concepts like synchronous, asynchronous or buffered communication, depending on the underlying architecture of the computational and communication resources, are offered and can be directly accessed in the applications' source code. Some projects consider high level protocol implementations in both software and hardware to realize uniform communication between hardware and software processing modules [71].

## 2.5 Discussion

As seen in the previous sections, published literature on reconfigurable systems is vast and reaches into multiple research fields. An important field of research is communication, especially as communication is a main factor limiting cost, area, power and performance of systems [17].

Many publications on communication in reconfigurable system focus on the architecture of the interconnection network and aim at developing an efficient communication infrastructure. The network resources of the RD need to provide a high degree of flexibility, in order to handle the changing requirements due to dynamic partial reconfigurations [55, 35, 50]. NoCs are most prominently considered as the interconnection network for reconfigurable devices and certain network aspects like quality of service [27] or buffer sizes [16, 51, 4] are taken into account during design. However, in many cases resource usage of the interconnection network is not optimal because communication resources do not adapt to the applications' communication and/or computational resource demand

[35, 20, 56, 11]. Therefore, methods for efficient resource usage have to be considered in the design of interconnection networks.

Protocols managing the communication on RDs generally target specific architectures, the S-XY routing algorithm of [11] is directly implemented in the hardware of the router, for example. Higher layer RD communication protocols enable flexible communication between applications. Most high layer protocols for on-chip systems can not be adapted to the applications' needs [60, 46, 28, 71] and therefore have a higher memory demand and reduced performance in comparison to adaptable protocols. Hence, flexible and adaptable high-level communication protocols have to be considered in reconfigurable systems.

Only few publications on communication consider resource management of reconfigurable devices during runtime. Most works on resource management focus on optimizing device utilization [64, 23, 26, 61, 18] of the RD, but do not consider communication as a performance factor. Communication-aware on-line temporal and spatial planning offer possibilities to improve performance, e.g. by reducing the network load and path length due to communication-aware scheduling [3, 65, 41]. However, this methods have to be further investigated and evaluated.

In this work a holistic approach on applications' communication with reconfigurable systems during design time and runtime is presented, which increases performance and flexibility through resource efficient management of communication demands.

# 2.6 Chapter conclusion

This chapter gave an overview of research aspects in the field of reconfigurable computing systems. An abstract hardware architecture of a reconfigurable multiprocessor systems was introduces as the basic resource model used in this work. Several actual reconfigurable devices with different complexities, performance characteristics, granularity and reconfiguration capabilities were described. A brief overview of state-of-the-art interconnection networks and communication protocols for reconfigurable devices has been given. Finally, a resource manager for the management of reconfigurable devices was introduced with the main job being temporal planning and placement of tasks.

The placement of tasks directly influences the volume of communication traffic, so task scheduling should be communication aware to efficiently use the communication resources of the reconfigurable device. Shorter communication path lead to an overall higher system performance, as latency between sender and receiver as well as the network load are reduced. Yet, most scheduling algorithms consider the calculation of viable allocations only and do not comprise finding an optimal placement in regard to communication.

The next chapter presents methods to improve performance of a communication-aware on-line scheduling algorithm. Furthermore, a communication-aware off-line placement algorithm using declarative problem solving is introduced and compared to the on-line variant.

# 3 Scheduling on NoC-based reconfigurable architectures

This chapter describes communication-aware scheduling of tasks on reconfigurable devices using a NoC-based communication infrastructure. While this paper focuses on the communication between tasks and/or I/Os at the devices' border, scheduling on RDs has not only to provide minimized communication distance as an optimization goal, but aims for maximal device utilization, as well. The approach of this work is to determine time and area, i.e. when and where to place a task on the RD in a fashion to meet the following objectives:

- 1. The amount of placed tasks out of a task set is maximized and in turn minimizes rejection rates.

- 2. Communication distances (path length) between communication partners are shortened to a minimum.

The first objective ensures, that the maximum number of tasks out of a task set is executed, while the second objective minimizes path length between sender and receiver. Both goals are strongly related to placement as well as temporal planning. The research presented in this chapter firstly extends a basic on-line scheduler to increase the amount of placed tasks and to lower communication distances between tasks and secondly compares the results of the on-line placer with the optimal results calculated by an off-line placer. Rejection rate of a task set and path length (hop count) are the main metrics used for evaluation. Placement and temporal planning on reconfigurable devices are dependent on the architecture of the device and the used task model. Knowledge on the communication and configuration capabilities of the device is crucial: The size of the reconfigurable regions, as well as the time needed to reconfigure a region and the interconnection network have to be considered to fully exploit the capabilities of the reconfigurable device by a scheduling algorithm. For the thesis at hand, the DyNoC architecture for the dynamic interconnection of reconfigurable modules in a mesh network was used (see Chapter 2.4.2).

Tasks are built up out of one or more components communicating with each other or with I/Os at the devices' edge. An exemplary task is the MPEG-4 part 10 video compression algorithm. It performs several consecutive steps like discrete cosine transformation (DCT), entropy coding or quantization. Each of these steps is dependent on at least one

other step or an external data source or sink. The steps are modeled as components of the MPEG-4 task with intra-task dependencies.

## 3.1 Basic scheduler

This section is an extended version of [MCHB11]. Tasks have a set of components each consisting of at least one implementation in the form of a rectangular module covering a fixed amount of reconfigurable units. The relations between tasks, components and modules are defined as follows:

A task consists of at least one component.

**Definition 1 (Task-Component-Relation)** For each task  $t_i \in T$ , a non empty set  $C_i$  of components  $c_j \in C_i$  exist.

Each component has at least one input and output communication link.

**Definition 2 (Component-Component-Relation)** For each component  $c_j \in C_i$ , a set of communication partners or points  $cp_k \in CP_j$  exist.

Each communication partner or point  $cp_k \in CP_j$  is associated with the communication requirements average bandwidth  $ba_k$ , the communication distance  $cd_k$  and the attribute  $sr_k$  which marks the communication partner as a sender or receiver. Besides components, also memories or I/Os positioned around the RD can be communication partners, which are called interfaces.

**Definition 3 (Component-Module-Relation)** For each component  $c_j \in C_i$ , a non empty set  $M_j$  of modules  $m_k \in M_j$  exist.

With each module  $m_k \in M_j$  of a component  $c_j \in C_i$  of a task  $t_i$  a width  $w_k$  and height  $h_k$  and a worst-case execution time  $e_{jk}$  is associated. Thus, when considering several modules differing in area requirements and execution time, the selection of a modules need to be made prior to placement and temporal planning.

**Definition 4 (Feasible Module Selection)** A feasible module selection assigns a module  $m_k \in M_j$  to each component  $c_j \in C_i$  of task  $t_i$ , so that a feasible schedule exist.

A feasible schedule has to consider both spatial and temporal aspects meaning a placement on the device as well as a start time (temporal planning) for a task have to be found.

**Definition 5 (Feasible Schedule)** A feasible schedule exist, when placement and temporal planning for the task exist.

The issues of placement and temporal planning are firmly related; a feasible start time cannot be assigned without considering the placement of the tasks' modules.

**Definition 6 (Feasible Placement)** Presuming, a set  $M_p$  of already placed modules  $m_l \in M_p$  on a device with size  $(A_x, A_y)$  is given. With all modules  $m_l \in M_p$  an origin  $x_l, y_l$  and the required space  $w_l, h_l$  of the modules is associated. A feasible spatial planning for a newly arriving task  $t_i$  at time  $a_i$  with the components  $c_j \in C_i$ , the selected modules  $m_k$  and the required space  $w_k, h_k$  of each module  $m_k$  exist, if for each  $m_k$  a position  $x_k, y_k$  on the reconfigurable device can be found satisfying the following conditions:

I)

$$x_k + w_k \le A_x \land y_k + h_k \le A_y$$

II)  $\forall m_l \in M_p$ :

$$[(x_l + w_l) \le x_k \lor (x_k + w_k) \le x_l] \land [(y_l + h_l) \le y_k \lor (y_k + h_k) \le y_l]$$

As soon as a feasible placement for the selected module  $m_k \in M_j$  has been determined, a start time  $s_i \leq a_i$  can be assigned to the task  $t_i$ . Modules of tasks having finished execution are removed from the RD, i.e.,  $M'_p = M_p \setminus m_k$ . Only when the task finishes prior its deadline  $d_i$  a feasible temporal planning exist.

**Definition 7 (Feasible Temporal Planing)** A feasible temporal planning assigns a task  $t_i$  a start time  $s_i$ , so that  $s_i + e_i + o_i < d_i$  holds true.

$e_i$  is the expected execution time of a task  $t_i$  and  $o_i$  contains the amount of configuration overhead.

Up next, the implementation of a basic scheduler follows.

#### 3.1.1 Placement

Placement generally includes two steps, management of free space (partitioner) and fitting the application in this space (fitter). The partitioner keeps track of available free space on the device, while the fitter selects an area inside this free space depending on selection strategy. The research at hand is based on the routing-conscious, dynamic placement algorithm by Ahmadinia et al. [3]. This algorithm can be computed in  $\theta(n \log n)$  time and considers manhattan distance between modules to select optimal placement. In contrast to [6, 63, 66], the algorithm by [3] manages free space by storing the location of occupied spaces and finding a placement for a single point instead of searching completely through all free rectangles. This is done by shrinking the reconfigurable device of an area  $A = (0, 0, A_x, A_y)$  and simultaneously blowing up the already placed modules  $m_p \in M_p$  by half of the width  $w_j/2$  and half of the height  $h_j/2$  of the module yet to be placed  $m_j$ . Equation 1 shrinks the area of the reconfigurable device A and Equation 2 blows the modules up.

$$A' = \left(\frac{w_j}{2}, \frac{h_j}{2}, A_x - \frac{w_j}{2}, A_y - \frac{h_j}{2}\right) \tag{1}$$

$$m'_{p} = (x'_{p}, y'_{p}, w'_{p}, h'_{p})$$

(2)

Equation 3 and 4 calculates the new x and y position  $x'_p$  and  $y'_p$  of a placed module on the shrunken reconfigurable device A'.

$$x_p' = \max(x_p - \frac{w_j}{2}, \frac{w_j}{2}) \tag{3}$$

$$y_p' = \max(y_p - \frac{h_j}{2}, \frac{h_j}{2}) \tag{4}$$

Equations 5 and 6 determines the updated width  $w'_p$  and height  $h'_p$  of the already placed module.

$$w_p' = \min(w_p + w_j, W - w_j) \tag{5}$$

$$h_p' = min(h_p + h_j, H - h_j) \tag{6}$$

In the end, all possible positions for  $m_j$  are reduced to points instead of rectangles. The fitter then selects a point location from the available free space. The points immediately on the edge of the chip are of particular interest, as they preserve the structure of free space in good shape. The contours of the free space are computed using the CUR algorithm (contour of union of rectangles) [31] known from computational geometry. It performs plane sweeps and uses segmentation trees as data structures. The optimal point for the module in the available free space is found by minimizing the manhattan distance between communication points.

# 3.1.2 Temporal planning

If a feasible placement for a task has been calculated and the task  $t_i$  meets its deadline  $d_i$  (feasible temporal planning) the task is accepted and placed on the reconfigurable device.

When considering multiple tasks with different area requirements, execution times, deadlines and arrival times, one has to order these tasks in a priority queue according to their specific requirements. Placement of the task of highest priority is then calculated first and, if a feasible placement exists, the task is loaded on the RD. Next the task of second highest priority is considered for placement, and so on. Steiger et al. [64] have shown that sorting the tasks according to their deadline leads to better results compared to ordering according to size. This sorting process is an adaption of the well known EDF dynamic scheduling algorithm for real-time systems. Furthermore, an currently unplaceble task is put on hold and the computation continues with the next task in queue. Danne [18] called this the EDF-NF (Next-Fit) algorithm and presented a schedulability test for periodic task sets. The Next-Fit strategy can place and execute tasks out-of-order, thus allowing a better utilization of the reconfigurable device. The work at hand uses the EDF-NF algorithm.

The following sections extends and optimizes the basic scheduler trying to maximize device utilization as well as minimizing communication distance between communication partners. Module selection is considered the first optimization necessary, focusing on device utilization.

# 3.2 Integrated module selection

The selection of a module from a set of modules implementing the same functionality but having different constraints poses the first issue to turn to. Research on the matter was published in [MCHB11] and this section is a derivation of this paper.

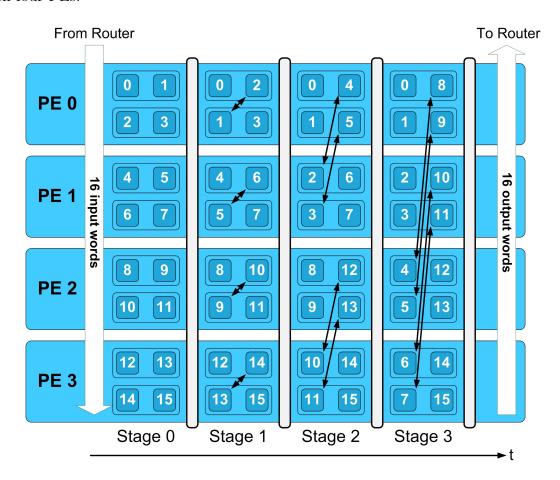

Tasks can be computed by different implementations (modules) of a component varying in size, execution time and communication overhead: Computing an Fast Fourier Transformation (FFT), for instance, involves the butterfly operation. A N-point Discrete Fourier Transformation (DFT) needs  $log_2(N)$  stages with N/2 radix-2-butterflies per stage. Viable FFT implementations need to calculate one radix-2-butterfly operation at minimum, covering the area a, or at most N/2 butterflies covering an area of roughly  $a \cdot N/2$ . This does not consider the area needed for communication. Thus the execution time of a N-point DFT varies when done on different modules. The largest implementation computes N/2 butterflies in parallel and is about N/2 times faster then the smallest one. Other tasks, as present in image processing, sort algorithms or applications using the Monte Carlo method show a similar behavior. The availability of several modules of different characteristic implementing the very same component of a task, does not only expand the design space for static designs, but also for dynamic implementations like Dynamic Networks-on-Chip. In particular, selecting the best fitted module has impact on both schedulability and optimality of an implementation.

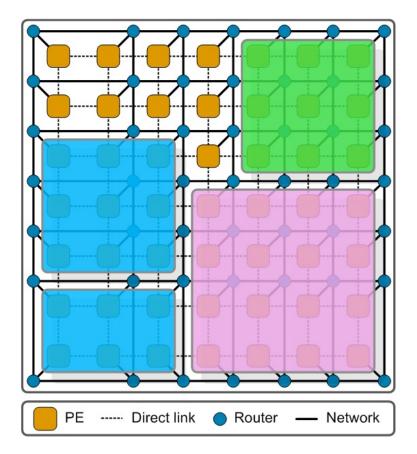

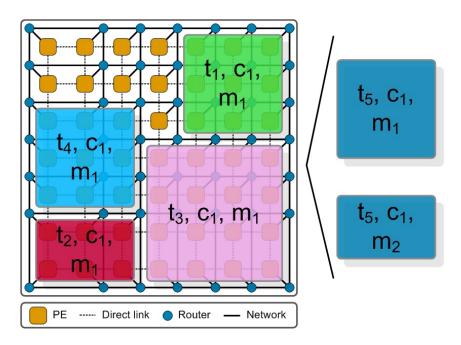

In Figure 12 the tasks  $t_1$ ,  $t_2$ ,  $t_3$  and  $t_4$  with one component per task are placed on a DyNoC. Task  $t_5$  has one component implemented by two modules  $m_1$  and  $m_2$ . The modules differ in size and execution time with  $m_1$  having the shorter execution time but covering a larger area of the RD.

A feasible placement of  $t_5$  is only possible with module  $m_2$ , as  $m_1$  excels the available space. Still, the execution time of  $m_2$  must not excess the deadline of  $t_5$ . Module selection is an extension to temporal planning and placement steps and is integrated in the scheduler.

This section only considers tasks consisting of one component in order to evaluate the achievable performance through integrated temporal planning, module selection and placement. The problem definition for integrated temporal planning, module selection and placement reads as follows:

Figure 12: Module selection of task  $t_5$

# Definition 8 (Integrated temporal planning, module selection and placement)

Given a set T of tasks  $t_i \in T$  with arrival times  $a_i$ , components  $C_i$  and associated modules  $m_j \in M_j \subset M_i$ . For each component  $c_j \in C_i$  selects a module  $m_j \in M_j$  in such a way that a feasible schedule for the maximal number of tasks  $t_i$  exists.

# 3.2.1 Module selection strategies

State-of-the-art on-line schedulers only consider one module per task. With the availability of several modules able to execute a particular task, a fitting module has to be selected during runtime. Selecting the right module is crucial when considering device utilization and rejection rates. A solid module selection strategy should be dynamic in order to allow adaption to the current utilization of the device and timing requirements of the task. Another advantage of having multiple modules per task is the possibility to use other modules, if the initially chosen one cannot be scheduled.

**Dynamic Module Selection** The Largest Module First (LMF) heuristic picks the module with the largest area requirement first. When the largest module can not be placed, because free space is not big enough, the second largest module is chosen. The LMF is invoked over and over again until a feasible placement for the task has been found or the

execution time of the chosen module exceeds the deadline. This strategy tries to compute a task as fast as possible.

Smallest Module First (SMF) is the counter part to LMF and considers the module with the smallest area requirements first. When the runtime of this module conflicts with the given deadline of the task, the next largest module is chosen until the smallest possible module is found which meets the deadline. This strategy tries to maximize free space by using only the smallest operable module.

**Static Module Selection** While dynamic selection heuristics allow the adaption to the device state or timing by selecting smaller (slower) or larger (faster) modules, static heuristics preselect a module for placement at compile time and do not take other modules for a task into account. The following static module selection heuristics are discussed as a comparison to dynamic heuristics.

Largest Module Only (LMO) considers the module with the largest area requirement only.

Smallest Module Only (SMO) heuristic chooses the module with the smallest area requirement which meets the deadline  $d_i$ .

Average Size Module Only (ASMO) just picks the module of overall average size.

Module selection is integrated in the basic scheduler as an extension. Pseudo code for this extended scheduler is given next considering only tasks with one component.

#### 3.2.2 Extended scheduling algorithm

The scheduler handles tasks by managing them in different lists according to their current state. When a task arrives it is put in the  $T_{FLOATING}$  list and the scheduler is called.  $T_{FLOATING}$  holds all plannable tasks and sorts them by means of the EDF-Next-Fit temporal planning algorithm. The first task  $t_i$  of the list is checked for feasibility. A task is considered feasible, if there is at least one module for each component meeting the deadline  $t_i$ . deadline of the task. If the task is not feasible, it is rejected and put into the  $T_{REJECTED}$  list. A module  $m_j$  of a feasible task is selected according to the module selection strategy and the placer (spatial planning) is invoked. If placement is successful, the task is loaded on the device and put onto the  $T_{RUNNING}$  list, otherwise the next module of the task is chosen depending on the module selection strategy. If no feasible module

can be placed, the next task is considered (next fit) and  $t_i$  is put back in  $T_{FLOATING}$  again. It might be possible to schedule the task at later point.

# Algorithm 1 Scheduling with module selection

```

success \leftarrow FALSE

k \leftarrow 0

Sort(T_{FLOATING})

while (k \le next \ fit) do

t_i \leftarrow Pop(T_{FLOATING})

c_i \leftarrow t_i.C_i

M_s \leftarrow c_j.M_j

if (time() + M_s.MinRuntime() < t_i.deadline) then

while (not success and M_s \neq \emptyset) do

m_k \leftarrow SelectModule(M_s)

success \leftarrow Placement(t_i, c_i, m_k)

end while

if (success) then

t_i.start time \leftarrow time

t_i.state \leftarrow RUNNING

T_{RUNNING} \leftarrow t_i \cup T_{RUNNING}

else

t_i.state \leftarrow FLOATING

T_{FLOATING} \leftarrow t_i \cup T_{FLOATING}

end if

else

t_i.state \leftarrow REJECTED

T_{REJECTED} \leftarrow t_i \cup T_{REJECTED}

end if

k \leftarrow k + 1

end while

```

Algorithm 1 shows the pseudo code of one run of the scheduler. The algorithm has an overall complexity of  $O(n \log n)$ . In [3], Ahmadinia et al. showed the placement algorithm to be of a complexity of  $O(n \log n)$ . All other steps of the scheduling algorithm, like the ordering of tasks in a priority queue, are simply accessing and sorting lists taking O(n) or  $O(n \log n)$  steps respectively. Thus, the overall complexity of the scheduling algorithm remains in the  $O(n \log n)$  domain. The scheduler is integrated in a simulation environment and is implemented in the Python programming language.

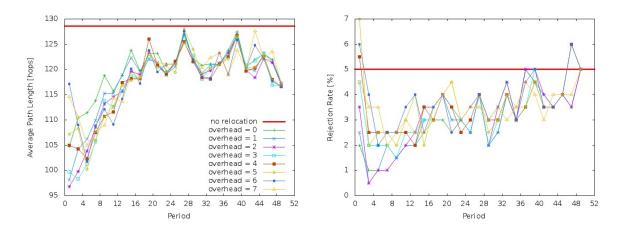

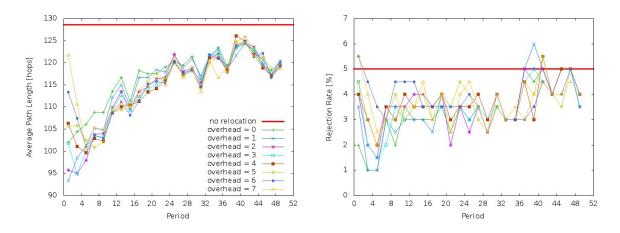

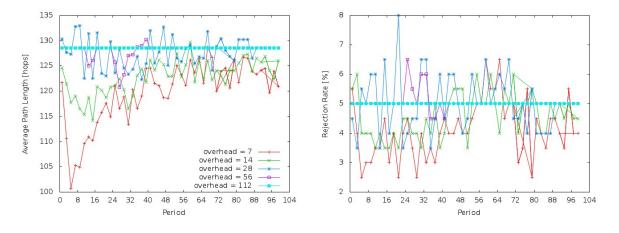

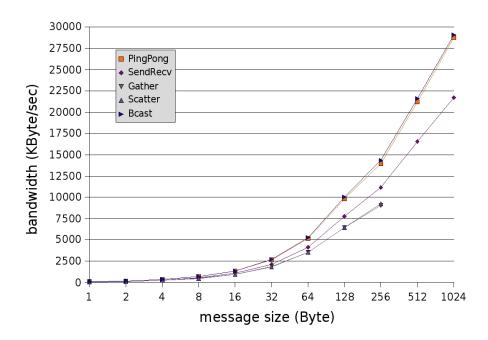

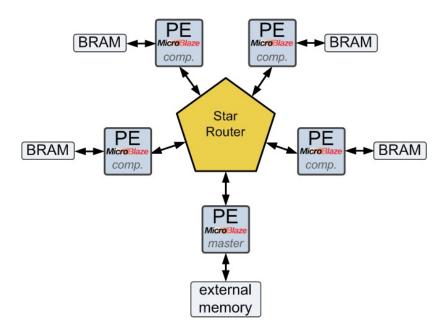

## 3.2.3 Evaluation