# A Methodology for Characterization, Modeling, and Mitigation of Single Event Transient Effects in CMOS Standard Combinational Cells

Marko Andjelkovic

Dissertation

zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.)

in der Wissenschaftsdisziplin "Rechnenarchitektur und Fehlertoleranz"

eingereicht an der Mathematisch-Naturwissenschaftlichen Fakultät Institut für Informatik der Universität Potsdam und IHP – Leibniz-Institut für innovative Mikroelektronik

Potsdam, 27.10.2021.

ii

Unless otherwise indicated, this work is licensed under a Creative Commons License Attribution 4.0 International.

This does not apply to quoted content and works based on other permissions.

To view a copy of this license visit:

https://creativecommons.org/licenses/by/4.0

Hauptbetreuer: Prof. Dr.-Ing. Milos Krstic (*Universität Potsdam und IHP*) Betreuer: Prof. Dr. rer. nat. habil. Mario Schölzel (*Hochschule Nordhausen*) Mentorin: Prof. Dr.-Ing. habil. Ulrike Lucke (*Universität Potsdam*)

Gutachter 1: Prof. Dr.-Ing. Milos Krstic (*Universität Potsdam und IHP*) Gutachter 2: Prof. Dr.-Ing. Harald Michalik (*Technische Universität Braunschweig*) Gutachter 3: Prof. Dr. Michael Gössel (*Universität Potsdam*)

Prüfungskommission:

- 1. Prof. Dr.-Ing. Beno Stabernack (Universität Potsdam) Vorsitzender

- 2. Prof. Dr.-Ing. habil. Ulrike Lucke (Universität Potsdam)

- 3. Prof. Dr.-Ing. Milos Krstic (Universität Potsdam und IHP)

- 4. Prof. Dr.-Ing. Harald Michalik (Technische Universität Braunschweig)

- 5. Prof. Dr. Michael Gössel (Universität Potsdam)

- 6. PD Dr. rer. nat. habil. Henning Bordihn (Universität Potsdam)

Published online on the Publication Server of the University of Potsdam: https://doi.org/10.25932/publishup-53484 https://nbn-resolving.org/urn:nbn:de:kobv:517-opus4-534843

## Acknowledgement

This work would have not been possible without the support of others. Therefore, I would like to thank all who helped in successful accomplishment of this work.

First of all, I would like to express my gratitude to Prof. Dr. Rolf Kraemer and Prof. Dr. Milos Krstic for the opportunity to conduct my research at IHP, and enormous help in the preparation of the project proposal. I owe special gratitude to the German Research Foundation DFG (Deutsche Forschungsgemeinschaft) for funding this work.

I would particularly like to thank my supervisor, Prof. Dr. Milos Krstic, for the support and guidance during the past five years. His advices and critiques have been crucial for achieving the results presented in this thesis, as well as for giving this thesis the final shape. In addition, his encouragement has been crucial in overcoming all obstacles during the course of work.

For numerous fruitful discussions I would especially like to thank Oliver Schrape. His support has been essential for better understanding of various design, technical and technological issues. For valuable feedback that helped in improving the quality of this work and the related publications, I would like to thank Aleksandar Ilic, Aleksandar Simevski, Anselm Breitenreiter, Junchao Chen, Milan Babic, Mitko Veleski, Yuanqing Li and Zoran Stamenkovic.

I would like also to express my sincere gratitude to Vladimir Petrovic and Zoran Stamenkovic, for their support during my short visits at IHP in 2014 and 2015, which have been essential for getting familiar with the research topics explored at IHP.

Last, but certainly not least, I want to thank my parents for their unconditional support and all they have done for me.

## Abstract

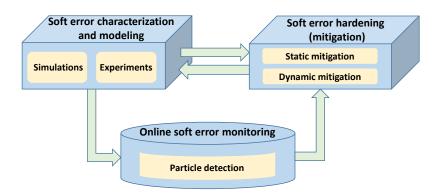

With the downscaling of CMOS technologies, the radiation-induced Single Event Transient (SET) effects in combinational logic have become a critical reliability issue for modern integrated circuits (ICs) intended for operation under harsh radiation conditions (e.g., in space). The SET pulses generated in combinational logic may propagate through the circuit and eventually be latched in storage elements (flip-flops or latches), resulting in soft errors and, consequently, in data corruption or system failure. It has thus become an imperative to address the SET effects in the early phases of the radiation-hard IC design. In general, the soft error mitigation solutions should accommodate both static and dynamic measures to ensure the optimal utilization of available resources. An efficient soft-error-aware design should address synergistically three main aspects: (i) characterization and modeling of soft errors, (ii) multi-level soft error mitigation, and (iii) online soft error monitoring. Although significant results have been achieved, the effectiveness of SET characterization methods, accuracy of predictive SET models, and efficiency of SET mitigation measures are still critical issues. Therefore, this work addresses the following topics:

- Characterization and modeling of SET effects in standard combinational cells,

- Static mitigation of SET effects in standard combinational cells, and

- Online particle detection, as a support for dynamic soft error mitigation.

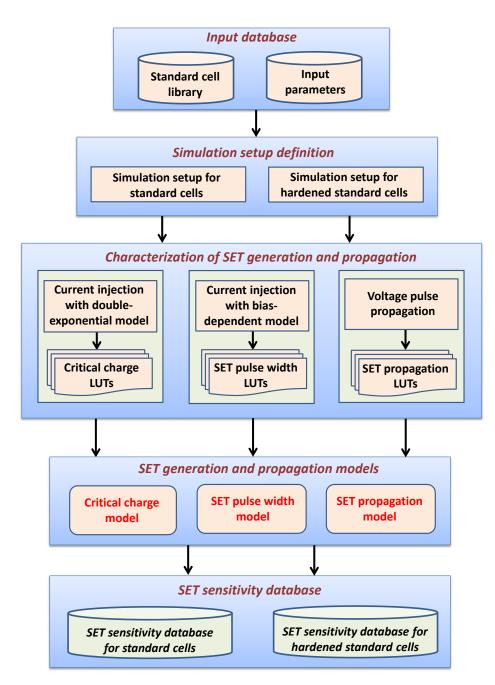

Since the standard digital libraries are widely used in the design of radiation-hard ICs, the characterization of SET effects in standard cells and the availability of accurate SET models for the Soft Error Rate (SER) evaluation are the main prerequisites for efficient radiation-hard design. This work introduces an approach for the SPICE-based standard cell characterization with the reduced number of simulations, improved SET models and optimized SET sensitivity database. It has been shown that the inherent similarities in the SET response of logic cells for different input levels can be utilized to reduce the number of required simulations in the characterization process. Based on characterization results, the fitting models for the SET sensitivity metrics (critical charge, generated SET pulse width and propagated SET pulse width) have been developed. The proposed models are based on the principle of superposition, and they express explicitly the dependence of the SET sensitivity of individual combinational cells on design, operating and irradiation parameters. In contrast to the state-of-the-art characterization methodologies which employ extensive look-up tables (LUTs) for storing the raw simulation results, this work proposes the use of LUTs for storing the fitting coefficients of the SET sensitivity models derived from the characterization results. In that way the amount of characterization data in the SET sensitivity database is reduced significantly, which could potentially enable to speed up the subsequent SER evaluation of a given design.

The initial step in enhancing the robustness of combinational logic is the application of gate-level mitigation techniques. This is done selectively, i.e., the mitigation techniques are applied to the most sensitive gates (with the highest SER). As a result, significant improvement of the overall SER can be achieved with minimum area, delay and power overheads. For the SET mitigation in standard cells, it is essential to employ the techniques that do not require modifying the cell structure. This work introduces the use of decoupling cells for improving the robustness of standard combinational cells. By insertion of

two decoupling cells at the output of a target cell, the critical charge of the cell's output node is increased and the attenuation of short SETs is enhanced. In comparison to the most common gate-level techniques (gate upsizing and gate duplication), the proposed approach provides better SET filtering. However, as there is no single gate-level mitigation technique with optimal performance, a combination of multiple techniques is required. This work introduces a comprehensive characterization of gate-level mitigation techniques aimed to quantify their impact on the SET robustness improvement, as well as introduced area, delay and power overhead per gate. By characterizing the gate-level mitigation techniques together with the standard cells, the required effort in subsequent SER analysis of a target design can be reduced. The characterization database of the hardened standard cells can be utilized as a guideline for selection of the most appropriate mitigation solution for a given design.

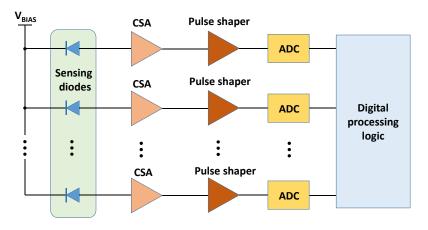

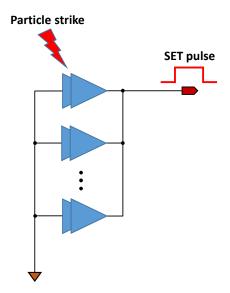

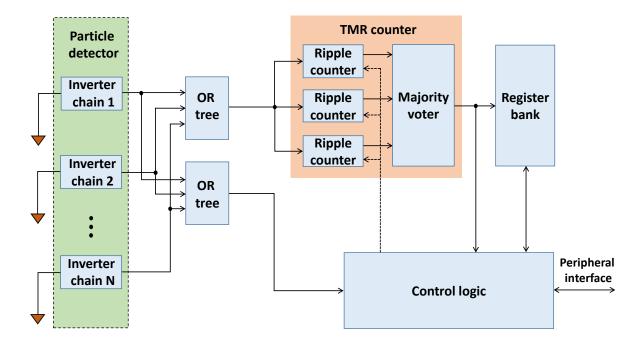

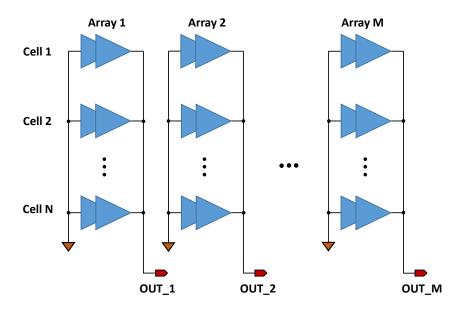

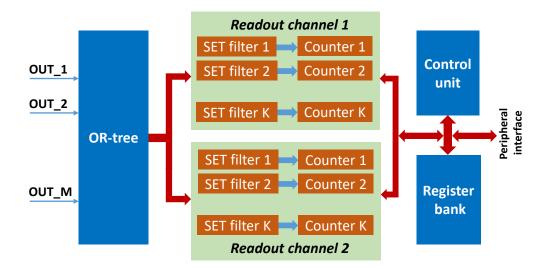

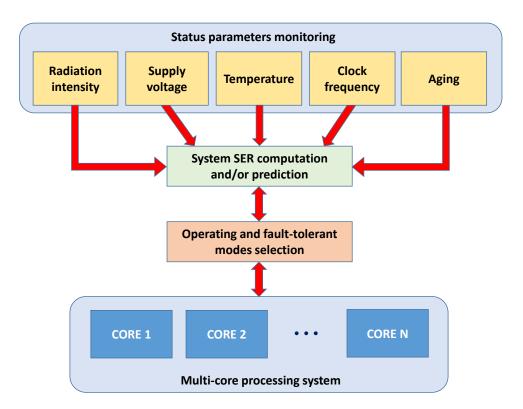

As a support for dynamic soft error mitigation techniques that are applied at the system level, it is important to enable the online detection of energetic particles causing the soft errors. This allows activating the power-greedy fault-tolerant configurations based on N-modular redundancy (e.g., Triple Modular Redundancy) only at the high radiation levels. To enable such a functionality, it is necessary to monitor both the particle flux and the variation of particle LET, as these two parameters contribute significantly to the system SER. In this work, a particle detection approach based on custom-sized pulse stretching inverters is proposed. Employing the pulse stretching inverters connected in parallel enables to measure the particle flux in terms of the number of detected SETs, while the particle LET variations can be estimated from the distribution of SET pulse widths. This approach requires a purely digital processing logic, in contrast to the standard detectors for flux and LET monitoring (e.g., diode-based detectors) which require complex mixed-signal processing. Besides the possibility of LET monitoring, additional advantages of the proposed particle detector are low detection latency and power consumption, and immunity to error accumulation.

The results achieved in this thesis can serve as a basis for establishment of an overall soft-error-aware database for a given digital library, and a comprehensive multi-level radiation-hard design flow that can be implemented with the standard IC design tools. The following step will be to evaluate the achieved results with irradiation experiments.

## Zusammenfassung

Mit der Verkleinerung der Strukturen moderner CMOS-Technologien sind strahlungsinduzierte Single Event Transient (SET)-Effekte in kombinatorischer Logik zu einem kritischen Zuverlässigkeitsproblem in integrierten Schaltkreisen (ICs) geworden, die für den Betrieb unter rauen Strahlungsbedingungen (z. B. im Weltraum) vorgesehen sind. Die in der Kombinationslogik erzeugten SET-Impulse können durch die Schaltungen propagieren und schließlich in Speicherelementen (z.B. Flip-Flops oder Latches) zwischengespeichert werden, was zu sogenannten *Soft-Errors* und folglich zu Datenbeschädigungen oder einem Systemausfall führt. Daher ist es in den frühen Phasen des strahlungsharten IC-Designs unerlässlich geworden, die SET-Effekte systematisch anzugehen. Im Allgemeinen sollten die Lösungen zur Minderung von Soft-Errors sowohl statische als auch dynamische Maßnahmen berücksichtigen, um die optimale Nutzung der verfügbaren Ressourcen sicherzustellen. Somit sollte ein effizientes Soft-Error-Aware-Design drei Hauptaspekte synergistisch berücksichtigen: (i) die Charakterisierung und Modellierung von Soft-Errors, (ii) eine mehrstufige-Soft-Error-Minderung und (iii) eine Online-Soft-Error-Überwachung. Obwohl signifikante Ergebnisse erzielt wurden, sind die Wirksamkeit der SET-Charakterisierung, die Genauigkeit von Vorhersagemodellen und die Effizienz der Minderungsmaßnahmen immer noch die kritischen Punkte. Deshalb befasst sich diese Arbeit mit den aktuellen Themen im Zusammenhang mit

- Charakterisierung und Modellierung von SET-Effekten in der Standardzellbibliothek

- Abschwächung von SET-Effekten in Standardzellen

- Online-Erkennung von Partikelflux- und LET-Variationen durch Messung der SETs

Da die digitalen Standardbibliotheken beim Entwurf von strahlungsharten ICs weit verbreitet sind, sind die Charakterisierung von SET-Effekten in Standardzellen und die Verfügbarkeit genauer SET-Modelle für die Bewertung der Soft Error Rate (SER) die Hauptvoraussetzungen für ein effizientes strahlungsharten Design. Diese Arbeit stellt einen Ansatz für die SPICE-basierte Standardzellcharakterisierung vor, der auf einer reduzierten Anzahl von Simulationen, verbesserten SET-Modellen und einer optimierten SET-Datenbank basiert. Es wurde gezeigt, dass die inhärenten Ähnlichkeiten in der SET-Antwort von Logikzellen unter verschiedenen Betriebseinstellungen verwendet werden können, um die Anzahl der erforderlichen Simulationen im Charakterisierungsprozess zu reduzieren. Basierend auf den Ergebnissen dieser Charakterisierung wurden Modelle für Metriken der SET-Empfindlichkeit wie kritische Ladung, erzeugte SET-Impulsbreite und propagierte SET-Impulsbreite erstellt. Diese Modelle drücken explizit den Einfluss der SETs auf die Entwurfs-, Betriebs- und Bestrahlungsparametern einer Schaltung aus. Solche Modelle können in Standardbibliotheken für verschiedene Technologien übernommen und als Grundlage für die SER-Bewertung eines Designs verwendet werden. Im Gegensatz zu den neuesten Charakterisierungs-methoden, bei denen umfangreiche Tabellen (Look-Up Tables, LUTs) zum Speichern der Simulations-ergebnisse verwendet werden, wird in dieser Arbeit die Speicherung der Anpassungskoeffizienten der SET-Sensitivitätsmodelle vorgeschlagen, die aus einer Charakterisierung entstehen. Auf diese Weise wird die Menge der Daten erheblich reduziert, wodurch die nachfolgende SER-Auswertung gegebenenfalls beschleunigt werden kann.

Der erste Schritt zur Verbesserung der Robustheit der kombinatorischen Logik ist die Anwendung von Techniken zur Minderung auf Gatter-Ebene. Dies erfolgt selektiv, d.h. die Techniken werden nur auf die empfindlichsten Gatter (mit dem höchsten SER) angewendet. Infolgedessen kann eine signifikante Verbesserung des gesamten SER mit minimalem Flächen-, Verzögerungs- und Leistungsaufwand erreicht werden. Für die SET-Minderung in Standardzellen ist es wichtig, die Techniken anzuwenden, die keine Modifikation der Zellstruktur erfordern. In dieser Arbeit wird die Verwendung von Entkopplungszellen zur Verbesserung der Robustheit von kombinatorischen Standardzellen vorgestellt. Durch Einfügen von zwei Entkopplungszellen am Ausgang eines Gatters wird die kritische Ladung des Ausgangsknotens dieser erhöht und eine Dämpfung kurzer SETs ermöglich. Im Vergleich zu den gängigen Techniken auf Gatter-Ebene (Upsizing und Duplizierung) bietet der vorgeschlagene Ansatz eine bessere SET-Filterung. Da es jedoch keine einzige Minderungstechnik auf Gatter-Ebene mit optimaler Leistung gibt, ist eine Kombination mehrerer Techniken erforderlich. In dieser Arbeit wird eine umfassende Charakterisierung von Techniken zur Minderung auf Gatter-Ebene vorgestellt, um deren Auswirkungen auf die Verbesserung der SET-Robustheit sowie den eingeführten Bereich, die Verzögerung und den Leistungsaufwand pro Gatter zu quantifizieren. Durch die Charakterisierung der Minderungstechniken auf Gatter-Ebene und den vorgeschlagenen robusteren Standardzellen kann der erforderliche Aufwand bei der anschließenden SER-Analyse eines Zieldesigns minimiert werden. Die Charakterisierungsdatenbank für die gehärteten Standardzellen auf Gatter-Ebene kann als Richtlinie für die Auswahl der am besten geeigneten Lösung für ein bestimmtes Design verwendet werden.

Zur Unterstützung dynamischer Techniken zur Minderung der Soft-Errors, ist es wesentlich eine Online-Überwachung energetischer Partikel auf Systemebene, zu ermöglichen. Dadurch können leistungshungrige, fehlertolerante auf N-modularer Redundanz basierende Konfigurationen (z. B. dreifache modulare Redundanz) nur unter den hohen Strahlungspegeln aktiviert werden. Um eine solche Funktionalität zu ermöglichen, ist es notwendig, sowohl den Partikelfluss als auch die Variation des Partikel-LET zu überwachen, da diese beiden Parameter wesentlich zum SER des Systems beitragen. In dieser Arbeit wird durch eigens dafür entwickelten Invertern, ein Ansatz zum Detektieren der Partikel vorgeschlagen. Die Verwendung dieser Zellen in einer parallelen Konfiguration ermöglicht die Messung des Partikelflusses in Bezug auf die Anzahl der erfassten SETs, während die Partikel-LET-Variation aus der Verteilung der verschiedenen SET-Impulsbreiten abgeschätzt werden kann. Dieser Ansatz erfordert eine einfache, rein digitale Verarbeitungslogik im Gegensatz zu den komplexeren Standarddetektoren für den Flux- und die LET-Überwachung (z. B. Detektoren auf Diodenbasis). Darüber hinaus sind die Möglichkeiten der LET-Überwachung, eine geringe Latenz, der geringe Stromverbrauch und die Immunität gegenüber einer Fehlerakkumulation die Hauptvorteile der hier vorgeschlagenen Lösung.

Die in dieser Arbeit erzielten Ergebnisse können als Grundlage für die Erstellung einer umfassenden Soft-Errors-Datenbank dienen, die zusammen mit einer Standardzellenbibliothek, eine vollständige mehrstufige strahlungsharte IC-Entwicklung unter der Verwendung gängiger IC-Entwurfswerkzeugen ermöglich. Der letzte Schritt besteht darin, die erzielten Ergebnisse durch Bestrahlungsexperimente zu bewerten.

# Contents

| Acknowledgement                                           | v     |

|-----------------------------------------------------------|-------|

| Abstract                                                  | vii   |

| Zusammenfassung                                           | ix    |

| List of Figures                                           | xvi   |

| List of Tables                                            | xxi   |

| List of Acronyms                                          | xxiii |

| 1. Introduction                                           |       |

| 1.1 Motivation                                            |       |

| 1.1.1 Soft Error Trends in CMOS Technologies              |       |

| 1.1.2 Soft-Error-Aware Design Concept                     | 5     |

| 1.1.3 SET Characterization and Modeling                   | 6     |

| 1.1.4 Radiation Hardening Techniques                      | 7     |

| 1.1.5 Online Soft Error Rate Monitoring                   |       |

| 1.2 Research Scope and Objectives                         | 9     |

| 1.3 Thesis Contributions                                  |       |

| 1.4 Thesis Organization                                   |       |

| 1.5 Publications                                          |       |

| 2. Basics of SET Effects                                  |       |

| 2.1 Radiation Environments and Quantities                 |       |

| 2.2 SET Generation Mechanisms                             |       |

| 2.2.1 Charge Generation                                   |       |

| 2.2.2 Charge Collection                                   |       |

| 2.2.3 SET Current and Voltage Pulse Formation             |       |

| 2.2.4 Charge Sharing and Single Event Multiple Transients |       |

| 2.3 SET Propagation Mechanisms                            |       |

| 2.3.1 SET Masking Effects                                 |       |

| 2.3.2 Other SET Propagation Effects                       |       |

| 2.4 SET Sensitivity Metrics                               |       |

|      | 2.4.1 C    | ritical Charge ( $Q_{CRIT}$ ) and LET Threshold ( $LET_{TH}$ ) | 23 |

|------|------------|----------------------------------------------------------------|----|

|      | 2.4.2 S    | ET Amplitude and Width                                         | 23 |

|      | 2.4.3 S    | oft Error Rate (SER)                                           | 24 |

|      | 2.4.4 C    | ross Section (σ)                                               | 25 |

| 2.5  | 5 Effect o | of CMOS Technology Scaling on SET Sensitivity                  | 25 |

|      | 2.5.1 C    | ritical Charge (Threshold LET) Scaling                         | 25 |

|      | 2.5.2 S    | ET Pulse Width Scaling                                         | 25 |

|      | 2.5.3 C    | ombinational SER Scaling                                       | 26 |

| 2.0  | 6 Parame   | ters Affecting the SET Sensitivity                             | 28 |

|      | 2.6.1 Ir   | npact of Technology Parameters                                 | 28 |

|      | 2.6.2 Ir   | npact of Design Parameters                                     | 29 |

|      | 2.6.3 Ir   | npact of Operating Parameters                                  | 30 |

|      | 2.6.4 Ir   | npact of Irradiation Parameters                                | 31 |

|      | 2.6.5 Ir   | npact of Other Failure Mechanisms                              | 32 |

|      | 2.6.6 R    | elative and Combined Impact of Multiple Parameters             | 32 |

| 3. R | elated V   | Vork                                                           | 33 |

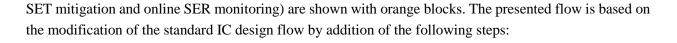

| 3.   | 1 A Mult   | ilevel Radiation-Hardening-By-Design Flow                      | 33 |

| 3.2  | 2 SET Ch   | aracterization in Combinational Logic                          | 35 |

|      | 3.2.1      | Simulation-Based and Analytical Characterization Methodologies | 35 |

|      | 3.2.2      | A Two-Phase Combinational SER Evaluation                       | 37 |

|      | 3.2.3      | SET Characterization of Standard Cell Library                  | 39 |

| 3.3  | 3 SET M    | odels                                                          | 43 |

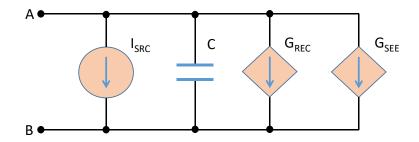

|      | 3.3.1      | SET Current Models                                             | 44 |

|      | 3.3.2      | Critical Charge Models                                         | 48 |

|      | 3.3.3      | SET Pulse Width Models                                         |    |

|      | 3.3.4      | SET Propagation Models                                         | 51 |

| 3.4  | 4 Gate-le  | vel SET Mitigation Approaches                                  | 53 |

|      | 3.4.1      | Gate Upsizing                                                  | 55 |

|      | 3.4.2      | Gate Duplication/Cloning                                       | 55 |

|      | 3.4.3      | Load Upsizing                                                  | 56 |

|      | 3.4.4      | Guarded Dual Modular Redundancy                                | 56 |

|      | 3.4.5      | Insertion of Charge Sharing Logic                              | 57 |

|      | 3.4.6      | Insertion of Cross-Coupled Inverters                           | 57 |

|      | 3.4.7      | Insertion of Schmitt Trigger                                   | 58 |

|      | 3.4.8      | Insertion of Transmission Gate                                 | 58 |

|      |            |                                                                |    |

|       | 3.4.9      | Insertion of Guard Gate Filter                                       | 58  |

|-------|------------|----------------------------------------------------------------------|-----|

|       | 3.4.10     | Insertion of Cascaded Inverters                                      | 59  |

|       | 3.4.11     | Comparison of Gate-level Hardening Techniques                        | 59  |

| 3.5   | 5 Particle | Detectors for On-line Soft Error Rate Monitoring                     | 61  |

|       | 3.5.1      | Bulk Built-in Current Detectors                                      | 61  |

|       | 3.5.2      | Acoustic Wave Detectors                                              | 63  |

|       | 3.5.3      | Diode Detectors                                                      | 63  |

|       | 3.5.4      | SRAM Detectors                                                       | 64  |

|       | 3.5.5      | 3D NAND Flash Detectors                                              | 65  |

|       | 3.5.6      | Comparison of Particle Detectors                                     | 65  |

| 3.6   | 5 Summa    | ry of Open Issues Addressed in this Thesis                           | 66  |

| 4. Cl | haracte    | rization and Modeling of SET Effects in Standard Combinational Cells | 68  |

|       |            | ction                                                                |     |

|       |            | tic Methodology for Standard Cell Library Characterization           |     |

|       |            | neration Analysis                                                    |     |

|       |            | ritical Charge Analysis                                              |     |

|       |            | ominal SER per Logic Gate                                            |     |

|       |            | ET Pulse Width Analysis                                              |     |

| 4.4   |            | ppagation Analysis                                                   |     |

|       |            | ET Propagation through Single-Input Gates                            |     |

|       |            | ET Propagation through Multiple-Input Gates                          |     |

|       |            | verall Comparison of SET Propagation Effects                         |     |

|       |            | ET Propagation in Combinational Paths                                |     |

| 4.5   |            | vare Design Considerations                                           |     |

| 4.6   | 5 SET Se   | nsitivity Models                                                     | 101 |

|       | 4.6.1 C    | ritical Charge Model                                                 | 101 |

|       | 4.6.2 G    | enerated SET Pulse Width Model                                       | 105 |

|       | 4.6.3 P    | ropagated SET Pulse Width Model                                      | 109 |

| 4.7   | SET Ef     | fects in Application-Specific Standard Cells                         | 113 |

|       | 4.7.1 S    | ET and SEU Effects in a Muller-C Element                             | 113 |

|       | 4.7.2 S    | ET Effects in a SEL Protection Switch                                | 115 |

| 4.8   | 8 Optimiz  | ation of SET Characterization Process                                | 118 |

|       | 4.8.1 R    | eduction of Number of Simulations                                    | 119 |

|       | 4.8.2 R    | eduction of SET Database                                             | 121 |

| 4.9   | Summa      | ry                                                                   | 125 |

| 5. Mitigation of SET Effects in Standard Combinational Cells       |  |

|--------------------------------------------------------------------|--|

| 5.1 Introduction                                                   |  |

| 5.2 Concept of SET Mitigation with Decoupling Cells                |  |

| 5.3 Analysis of SET Mitigation with Decoupling Cells               |  |

| 5.3.1 Critical Charge Analysis                                     |  |

| 5.3.2 Nominal SER Analysis                                         |  |

| 5.3.3 SET Pulse Generation Analysis                                |  |

| 5.3.4 SET Pulse Propagation Analysis                               |  |

| 5.3.5 Application of Decoupling Cells to Combinational Paths       |  |

| 5.4 Comparative Characterization of SET Mitigation Techniques      |  |

| 5.4.1 Comparison of SET Sensitivity                                |  |

| 5.4.2 Comparison of Area, Delay and Power Overhead                 |  |

| 5.4.3 Comparison of SET Mitigation Efficiency                      |  |

| 5.5 Combined Application of Multiple SET Mitigation Techniques     |  |

| 5.6 SET Mitigation in Standard Delay Cells                         |  |

| 5.7 Overall Comparison of SET Mitigation Techniques                |  |

| 5.8 Summary                                                        |  |

| 6. Particle Detection with Pulse Stretching Inverters              |  |

| 6.1 Introduction                                                   |  |

| 6.2 Design and Operation of a Pulse Stretching Cell (PSC)          |  |

| 6.3 Characterization of Normal Operation of a PSC                  |  |

| 6.3.1 Impact of Technology                                         |  |

| 6.3.2 Impact of Transistor Sizing                                  |  |

| 6.3.3 Impact of Supply Voltage and Temperature                     |  |

| 6.3.4 Impact of the Number of Cascaded Pulse Stretchers            |  |

| 6.4 Characterization of PSC as a Particle Detector                 |  |

| 6.4.1 SET Effects in a Single PSC                                  |  |

| 6.4.2 SET Effects in PSCs Connected in Series                      |  |

| 6.4.3 SET Effects in PSCs Connected in Parallel                    |  |

| 6.4.4 Overall Comparison of Serial and Parallel PSC Configurations |  |

| 6.5 Readout Circuit Design                                         |  |

| 6.5.1 Readout Circuit for Particle Flux Monitoring                 |  |

| 6.5.2 Readout Circuit for Particle Flux and LET Monitoring         |  |

| 6.6 Comparison with the State-of-the-Art Particle Detectors        |  |

| 6.7 Application in a Self-Adaptive Multi-Processor System          |  |

| 6.8 Summary          |  |

|----------------------|--|

| 7. Conclusion        |  |

| 7.1 Achieved Results |  |

| 7.2 Future Work      |  |

| Bibliography         |  |

# **List of Figures**

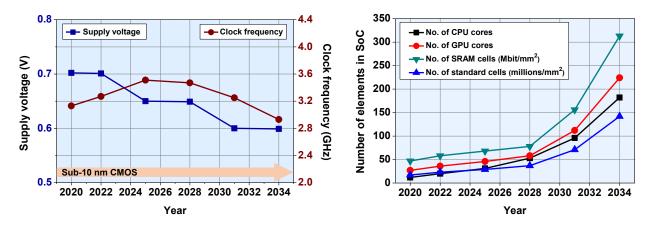

| Figure 1. 1:  | SoC scaling trends predicted by IRDS 2020 report [2]                             | 1  |

|---------------|----------------------------------------------------------------------------------|----|

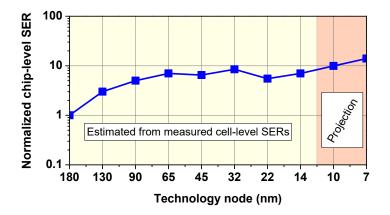

| Figure 1. 2:  | Chip-level SER trends with technology scaling [38]                               |    |

| Figure 1. 3:  | Main elements of a soft-error-aware IC design concept                            |    |

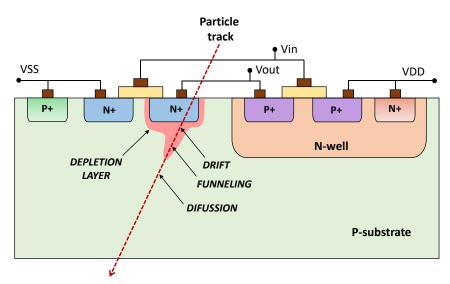

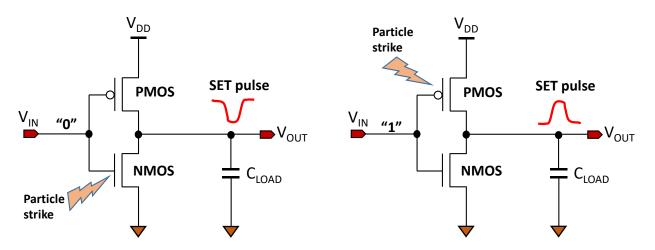

| Figure 2. 1:  | Basic mechanisms of particle interaction with a p-n junction in CMOS             |    |

| -             | inverter                                                                         | 17 |

| Figure 2. 2:  | Effect of particle strike in an inverter for low(0) and high(1) input levels     |    |

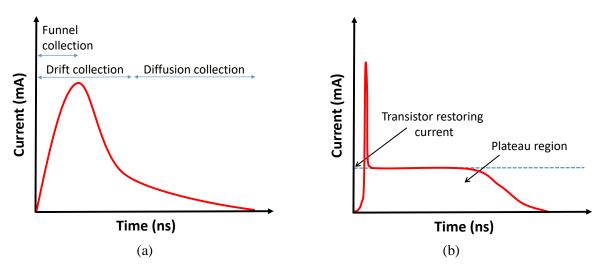

| Figure 2. 3:  | Typical shape of SET current pulse for: (a) low LET and (b) high LET             | 19 |

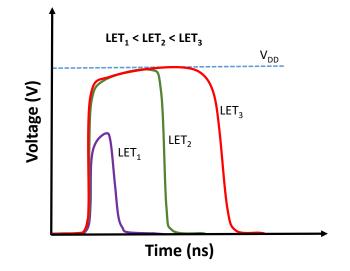

| Figure 2. 4:  | Typical shapes of positive (0-to-1) SET pulse for different LET                  |    |

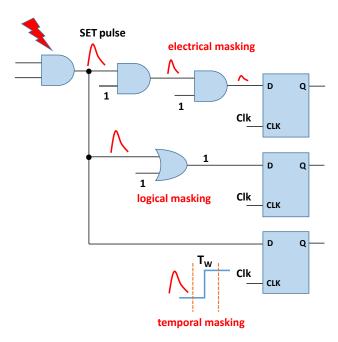

| Figure 2. 5:  | Effect of electrical, logical and temporal masking on SET propagation            |    |

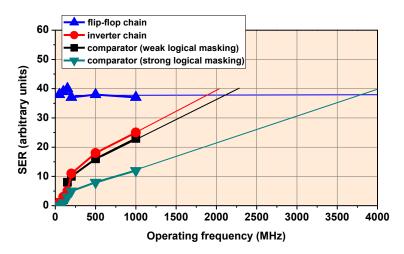

| Figure 2. 6:  | Measured SER (thick lines with symbols) and predicted SER (thin lines) as a      |    |

|               | function of operating frequency, for sequential and combinational logic in 40    |    |

|               | nm technology (reproduced from [44])                                             |    |

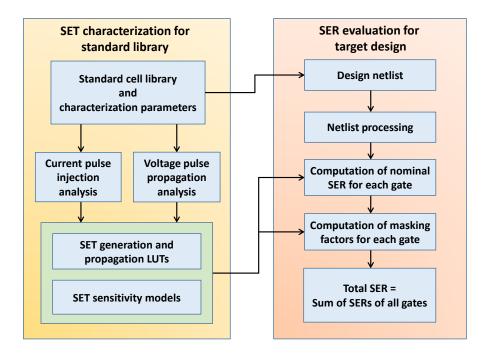

| Figure 3. 1:  | A multilevel rad-hard design flow for standard-cell-based IC designs             |    |

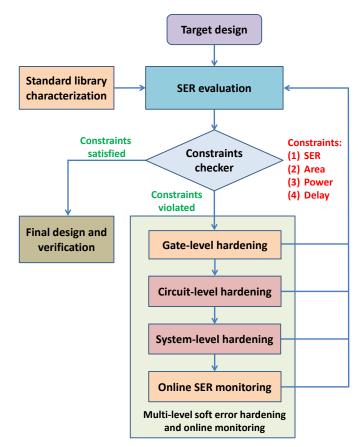

| Figure 3. 2:  | Hierarchy of multi-level simulation-based SET characterization                   |    |

| Figure 3. 3:  | A general two-phase combinational SER evaluation flow                            |    |

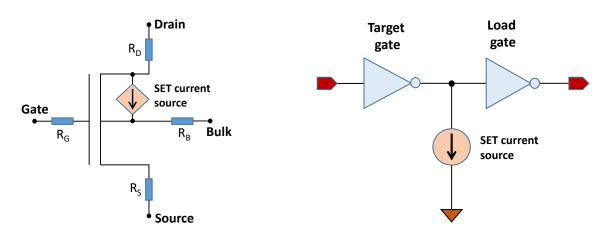

| Figure 3. 4:  | SET current models: micro-model (left) and macro-model (right)                   |    |

| Figure 3. 5:  | Bias-dependent current model proposed in [205, 206]                              |    |

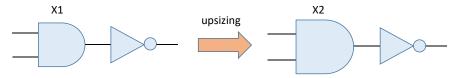

| Figure 3. 6:  | Gate upsizing by replacing AND2_x1 with AND2_x2                                  |    |

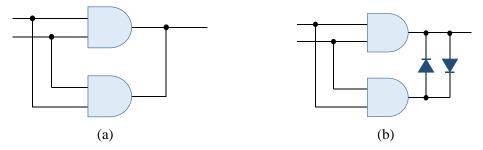

| Figure 3. 7:  | Duplication of AND gate: (a) standard variant, and (b) variant with clamping     |    |

|               | diode                                                                            |    |

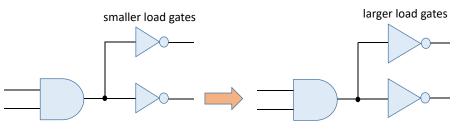

| Figure 3. 8:  | SET mitigation by increasing the size of load gates                              |    |

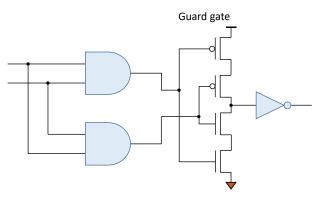

| Figure 3. 9:  | GDMR implementation of AND gate                                                  |    |

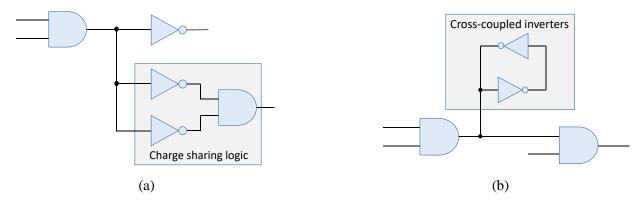

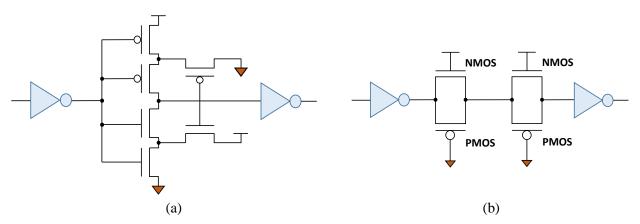

| Figure 3. 10: | SET mitigation in AND gate by with: (a) charge sharing logic, (b) cross-         |    |

|               | coupled inverters                                                                |    |

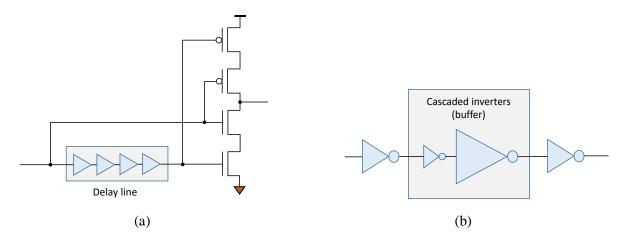

| Figure 3. 11: | SET mitigation with: (a) Schmitt trigger, and (b) transmission gates             |    |

| Figure 3. 12: | SET mitigation with (a) delay element and guard gate, (b) two cascaded           |    |

|               | inverters                                                                        |    |

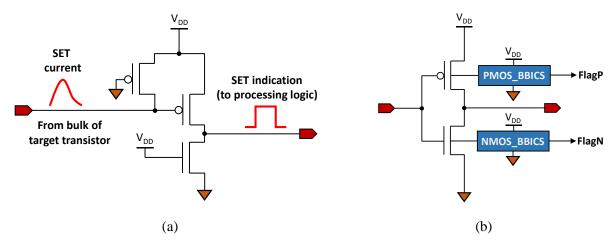

| Figure 3. 13: | BBICS implementation: (a) design of a PMOS-BBICS, and (b) connection of          |    |

|               | two BBICSs to an inverter [263]                                                  |    |

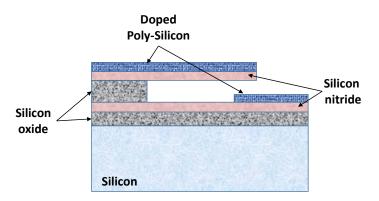

| Figure 3. 14: | A cross-section of cantilever structure for acoustic wave detection [270]        |    |

| Figure 3. 15: | Diode detectors with readout circuit                                             | 64 |

| Figure 4. 1:  | Proposed methodology for characterization and modeling of SET effects in         |    |

|               | standard cells and corresponding hardened configurations                         | 71 |

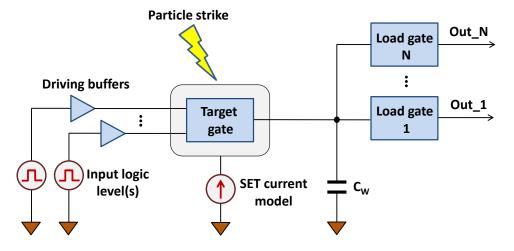

| Figure 4. 2:  | Simulation setup for characterization of SET effects in standard cells           | 73 |

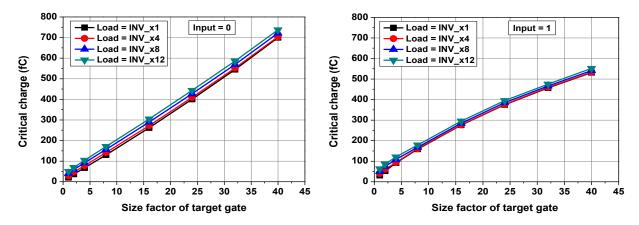

| Figure 4. 3:  | Critical charge of inverter as a function of its size factor, for different load |    |

|               | sizes and both input levels, and for nominal supply voltage (1.2 V) and          |    |

|               | temperature (27 °C)                                                              | 76 |

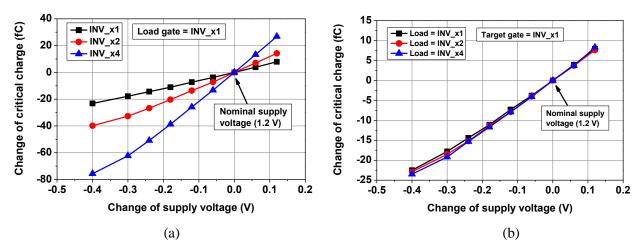

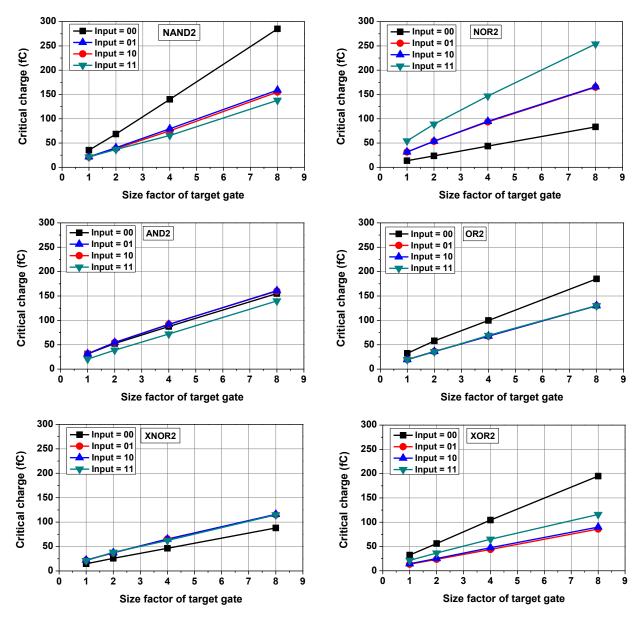

| Figure 4. 4:  | Change of critical charge of INV gate as a function of the change of supply      |    |

|               | voltage, for: (a) different driving strengths of target inverter, (b) different  |    |

|               | driving strengths of load inverter                                               | 77 |

| Figure 4. 5:  | Change of critical charge of INV gate as a function of the change of temperature with respect to $T_{EMP} = 27$ °C, for different driving strengths of |     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|               | INV gate and low input level                                                                                                                           |     |

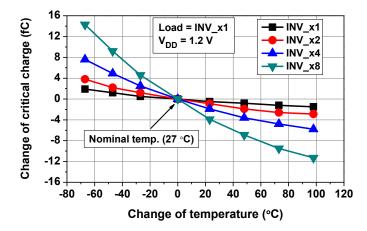

| Figure 4. 6:  | Critical charge of INV gate as a function of rise and fall time constants of the                                                                       |     |

|               | current pulse, for different driving strengths of INV gate and low input level                                                                         |     |

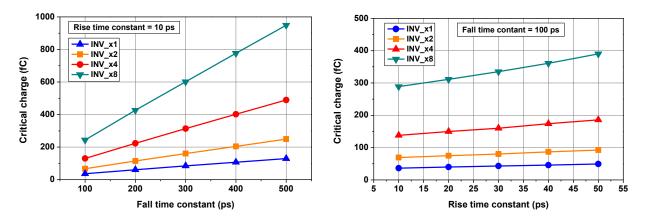

| Figure 4. 7:  | Critical charge of two-input logic gates as a function of their driving strength                                                                       |     |

|               | and input levels, while all other parameters are at nominal values                                                                                     |     |

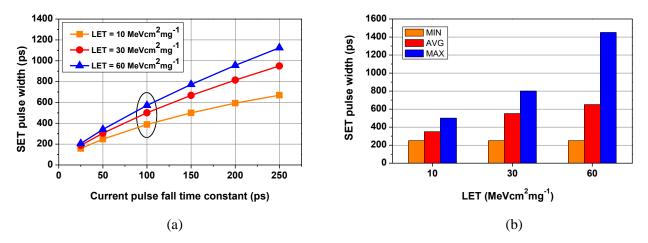

| Figure 4. 8:  | SET pulse width for LET of 10, 30 and 60 MeVcm <sup>2</sup> mg <sup>-1</sup> : (a) SPICE                                                               |     |

|               | simulation results for INV_x1 gate, (b) minimum, average and maximum                                                                                   |     |

|               | values measured by Narasimhan et al. [115]                                                                                                             |     |

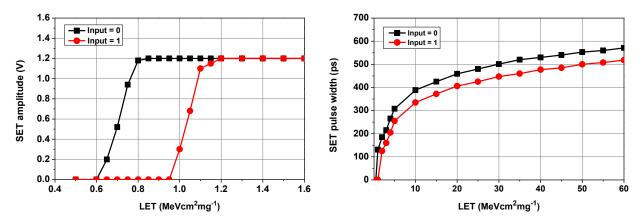

| Figure 4. 9:  | SET pulse amplitude and width as a function of LET, for current injection in INV_x1                                                                    |     |

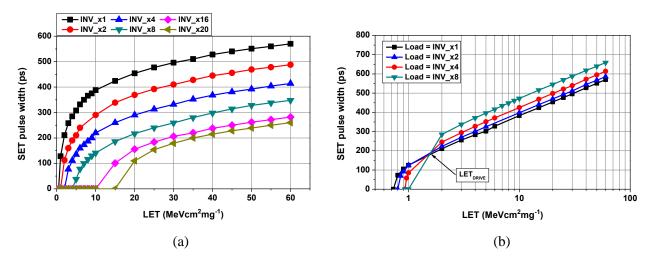

| Figure 4. 10: | SET pulse width as a function of LET: (a) for different driving strengths of                                                                           |     |

|               | target inverter with low input level and INV_x1 as a load gate, and (b) for                                                                            |     |

|               | INV_x1 as a target gate with low input level and different driving strengths                                                                           |     |

|               | of load inverter                                                                                                                                       |     |

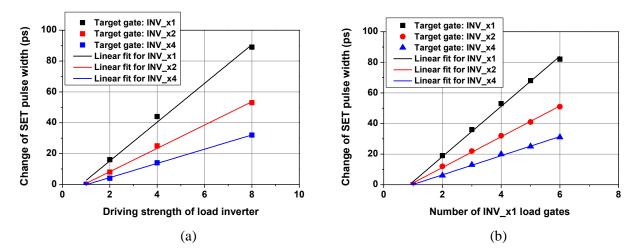

| Figure 4. 11: | SET pulse width for LET = 60 MeVcm <sup>2</sup> mg <sup>-1</sup> , as a function of: (a) driving                                                       |     |

|               | strengths of target inverter and load inverter, and (b) driving strength of target                                                                     |     |

|               | inverter and number of INV_x1 load gates                                                                                                               |     |

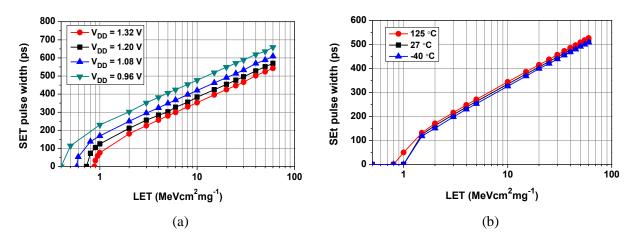

| Figure 4. 12: |                                                                                                                                                        |     |

|               | supply voltage, and (b) temperarure                                                                                                                    |     |

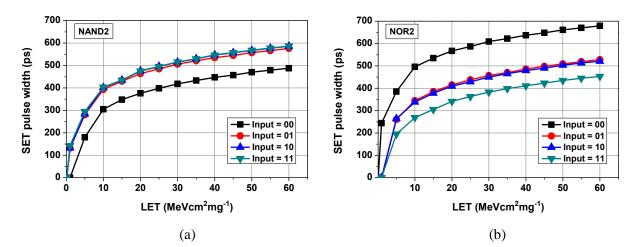

| Figure 4. 13: | SET pulse width as a function of LET, for (a) NAND2_x1, and (b) NOR2_x1                                                                                |     |

| Figure 4. 14: | SET pulse width at the output of SDC_x1 and SDC_x2, when current pulse                                                                                 |     |

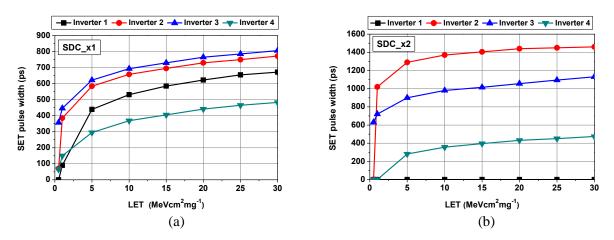

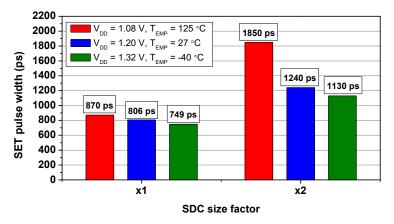

|               | is injected successively in each inverter within the cells, for low input level                                                                        |     |

| Figure 4. 15: | SET pulse width at the output of SDCs for supply voltage and temperature                                                                               |     |

|               | corners                                                                                                                                                |     |

| Figure 4. 16: | SET pulse width at the output of standard combinational cells with x1 driving                                                                          |     |

|               | strength, when the current pulse with $LET = 30 \text{ MeV cm}^2 \text{mg}^{-1}$ is injected in                                                        |     |

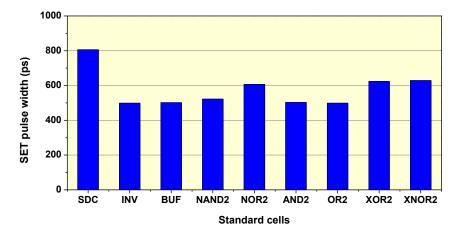

|               | most sensitive nodes                                                                                                                                   | 91  |

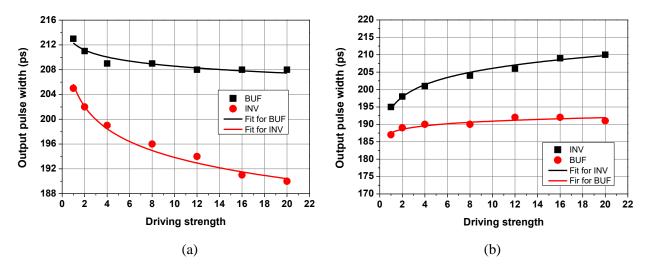

| Figure 4. 17: | SET pulse width at the output of INV and BUF gates, as a function of their                                                                             |     |

|               | driving strength, for: (a) positive input pulse of 200 ps, (b) negative input                                                                          |     |

|               | pulse of 200 ps                                                                                                                                        |     |

| Figure 4. 18: | SET pulse width at the output of INV gate, as a function of its driving strength                                                                       |     |

|               | and load capacitance, for: (a) positive input pulse of 200 ps, (b) negative input                                                                      |     |

|               | pulse of 200 ps                                                                                                                                        |     |

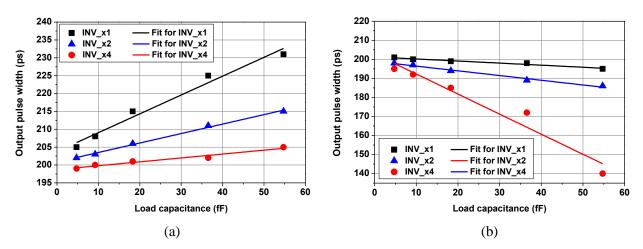

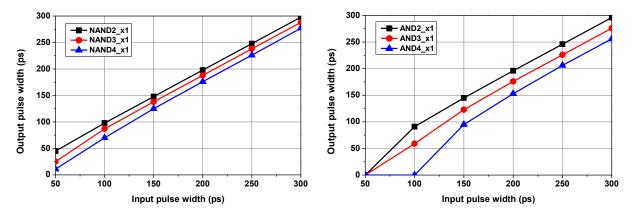

| Figure 4. 19: | SET pulse width at the output of 2-, 3- and 4-input NAND and AND gates, as                                                                             |     |

|               | a function of input SET pulse width                                                                                                                    |     |

| Figure 4. 20: | SET pulse width in terms of LET, for inviter with minimum size factor as a                                                                             |     |

| <b>T</b>      | target gate                                                                                                                                            |     |

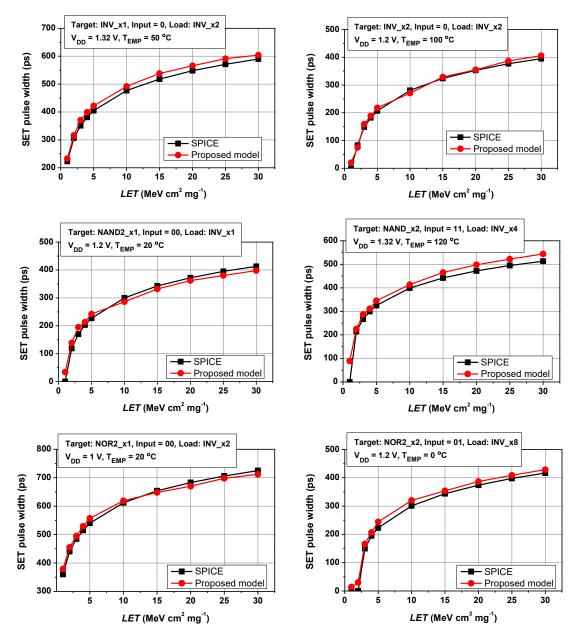

| Figure 4. 21: | Comparison of generated SET pulse width from simulations and proposed                                                                                  | 100 |

| E 4.02        | model, for INV, NAND2 and NOR2 gates                                                                                                                   |     |

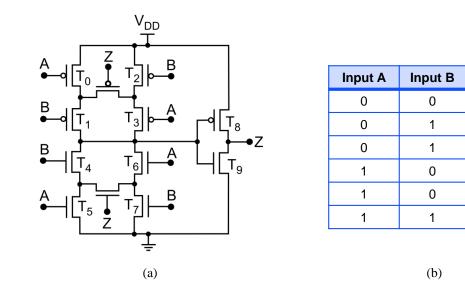

|               | Van Berkel's C-element implementation and C-element truth table                                                                                        | 114 |

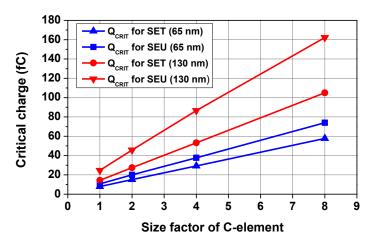

| Figure 4. 23: | Comparison of SET and SEU critical charge as a function of size factor of C-                                                                           | 114 |

|               | element, for INV_x1 as a load, and nominal supply voltage and temperature                                                                              |     |

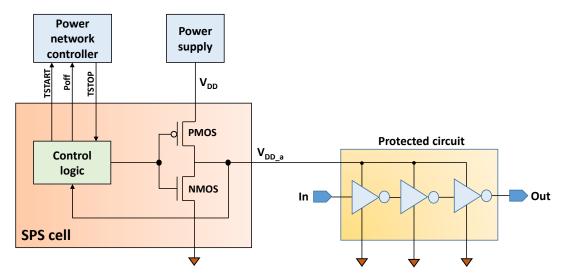

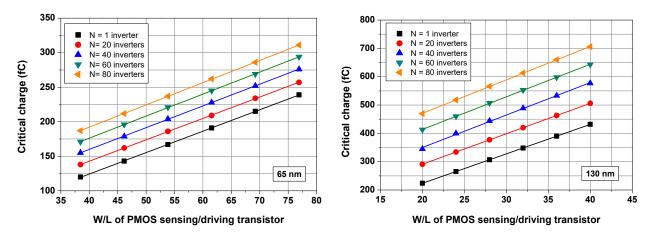

| Figure 4. 24: | SPS cell block diagram                                                            | 116 |

|---------------|-----------------------------------------------------------------------------------|-----|

| Figure 4. 25: | Critical charge of the output node of SPS cell as a function of W/L ratio of      |     |

|               | PMOS sensing/driving transistor and number of load inverters N (for fixed         |     |

|               | supply voltage, temperature and timing parameters of current pulse)               | 117 |

| Figure 4. 26: | A generic example of four LUTs for storing the critical charge values in terms    |     |

|               | of size factor of target gate, size factor of load gate and supply voltage, for   |     |

|               | nominal values of all other parameters (for a single input vector, one sensitive  |     |

|               | node and fixed timing parameters of current pulse)                                |     |

| Figure 4. 27: | A generic 2D LUT for storing the coefficients for critical charge model, for a    |     |

| -             | particular gate and all input vectors (for one sensitive node in target gate, and |     |

|               | fixed timing parameters of current pulse)                                         |     |

| Figure 4. 28: | A generic 2D LUT for storing the coefficients for generated SET pulse width       |     |

|               | model, for a particular gate and all input vectors (for one sensitive node in     |     |

|               | target gate, and fixed timing parameters of current pulse)                        | 124 |

| Figure 4. 29: | A generic 2D LUT for storing the coefficients for propagated SET pulse width      |     |

| 0             | model, for a particular gate and all input pins                                   | 124 |

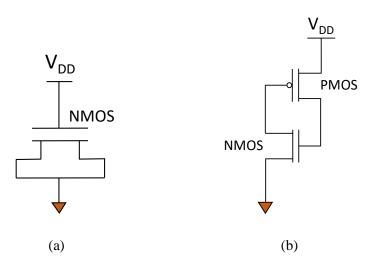

| Figure 5. 1:  | Schematic of decoupling cell in CMOS technology; (a) with one NMOS                |     |

| -             | transistor, (b) with cross-coupled NMOS and PMOS transistors                      | 129 |

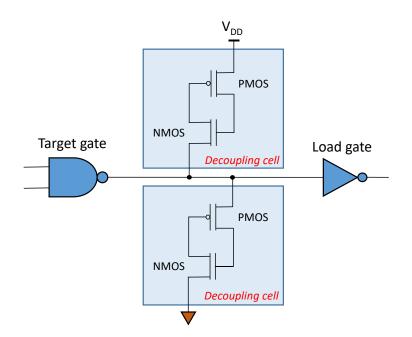

| Figure 5. 2:  | Application of two decoupling cells for improving the SET robustness of           |     |

| 0             | NAND gate                                                                         |     |

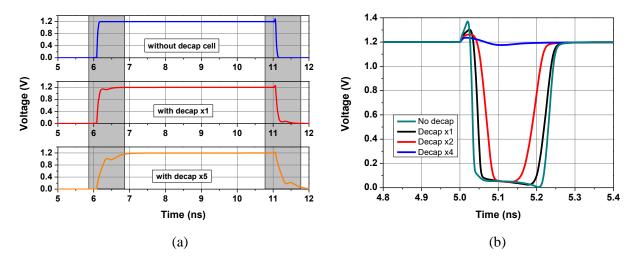

| Figure 5. 3:  | Response of NAND2_x1 gate: (a) normal pulse after propagation through             |     |

| -             | NAND2_x1 gate without and with decoupling cells, (b) SET pulses generated         |     |

|               | at the output of NAND2_x1 gate without and with decoupling cells                  | 131 |

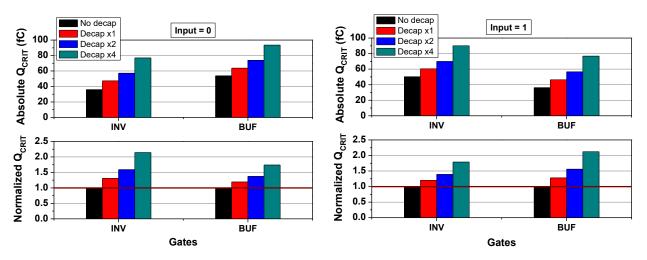

| Figure 5. 4:  | Absolute and normalized Q <sub>CRIT</sub> when two decoupling cells with driving  |     |

| 0             | strengths x1, x2 and x4 are inserted successively at the output of 1-input gates  |     |

|               | (for all input levels)                                                            |     |

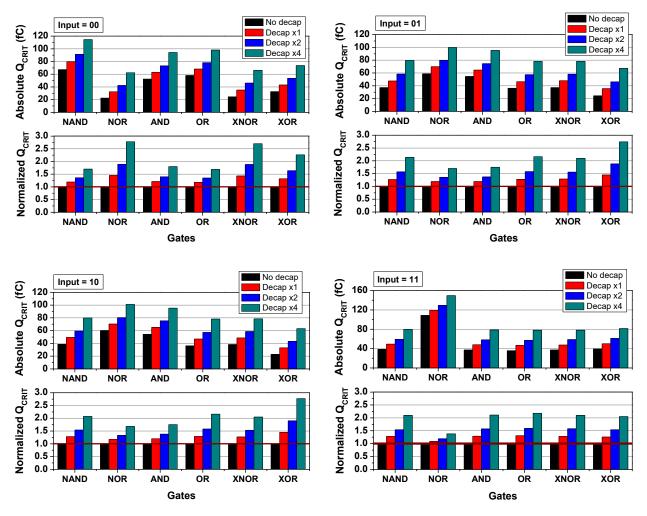

| Figure 5. 5:  | Absolute and normalized Q <sub>CRIT</sub> when two decoupling cells with driving  |     |

| 0             | strengths x1, x2 and x4 are inserted successively at the output of 2-input gates  |     |

|               | (for all input levels)                                                            |     |

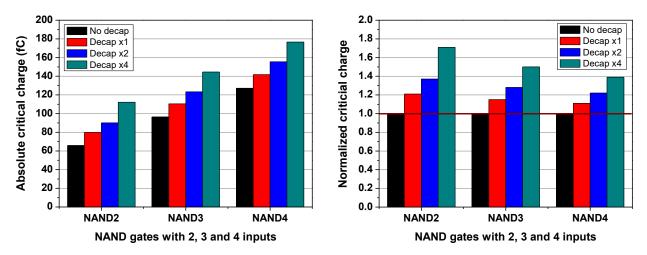

| Figure 5. 6:  | Absolute and normalized Q <sub>CRIT</sub> when two decoupling cells with driving  |     |

| 0             | strengths x1, x2 and x4 are inserted successively at the output of 2-, 3- and 4-  |     |

|               | input NAND gate (for low input levels)                                            | 134 |

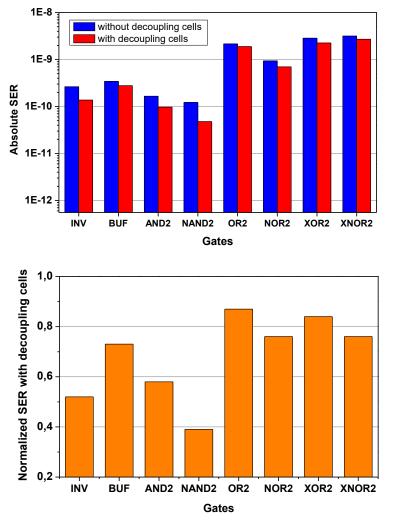

| Figure 5. 7:  | Absolute and normalized SER for 1- and 2-input standard logic gates with          |     |

| 0             | and without decoupling cells with size factor x1, for most sensitive input        |     |

|               | levels                                                                            | 137 |

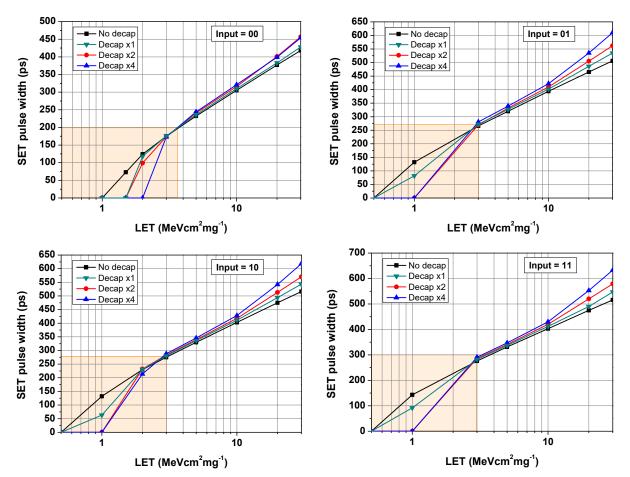

| Figure 5. 8:  | SET pulse width at the output of NAND2_x1 gate as a function of LET, when         |     |

| C             | decoupling cells with driving strengths x1, x2 and x4 are applied successively    |     |

|               | (for all input levels)                                                            |     |

| Figure 5. 9:  | Effect of decoupling cells on SET filtering for NAND2 and NOR2 gates              |     |

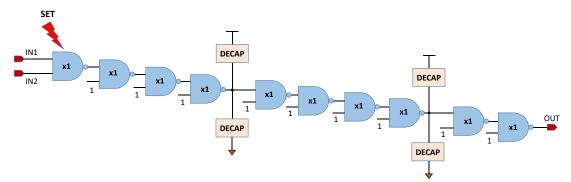

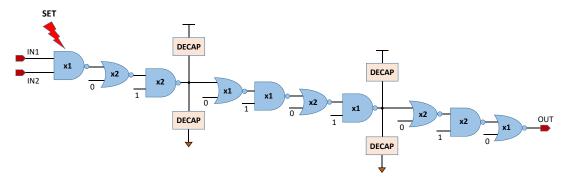

| Figure 5. 10: | Homogeneous path with NAND gates and decoupling cells at nodes 4 and 8            |     |

| Figure 5. 11: |                                                                                   |     |

| 0             | nodes 3 and 7                                                                     |     |

| Figure 5. 12: | SET pulse width at the output of a 10-gate NAND chain as a function of LET,       |     |

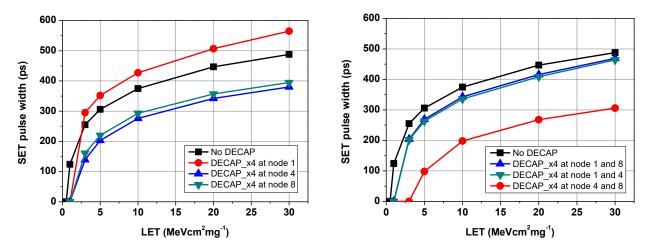

| C I           | for different positions of decoupling cells with size factor x4                   | 143 |

|               |                                                                                   |     |

| Figure 5. 13: | SET pulse width at the output of a 10-gate NAND-NOR chain as a function                            |     |

|---------------|----------------------------------------------------------------------------------------------------|-----|

|               | of LET, for different positions of decoupling cells with size factor x4                            | 143 |

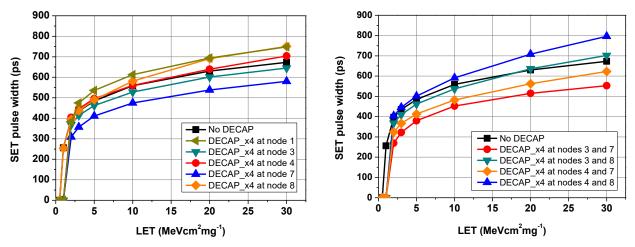

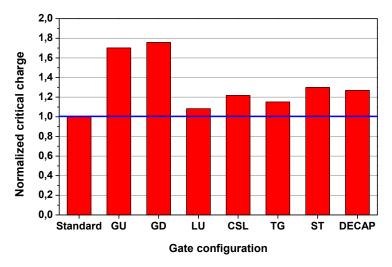

| Figure 5. 14: | Normalized critical charge for standard (non-hardened) NAND2_x1 gate and                           |     |

|               | NAND2_x1 gate with hardening configurations (for 11 input)                                         | 147 |

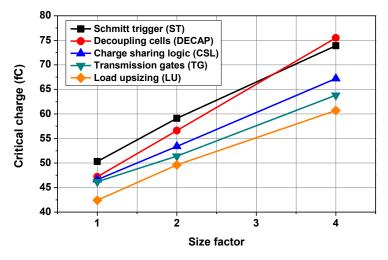

| Figure 5. 15: | Dependence of critical charge on size factor of applied hardening configu-                         |     |

|               | ration (for NAND2_x1 gate with 11 input)                                                           | 147 |

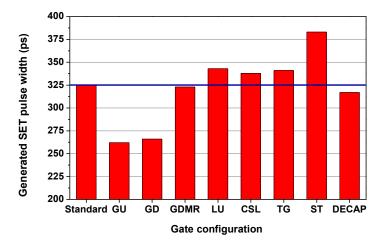

| Figure 5. 16: | Generated SET pulse width at the output NAND2_x1 gate without and with                             |     |

|               | hardening configurations with size factor x1, for $LET = 5 \text{ MeV}\text{cm}^2\text{mg}^{-1}$   | 149 |

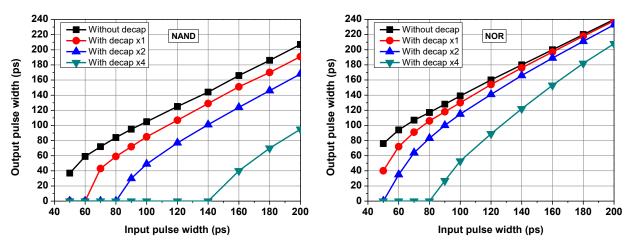

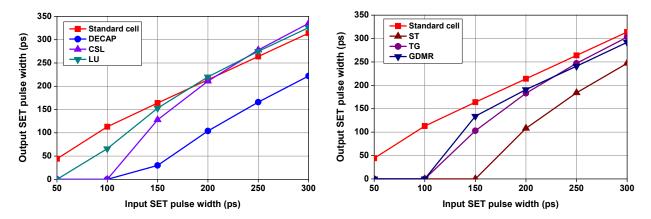

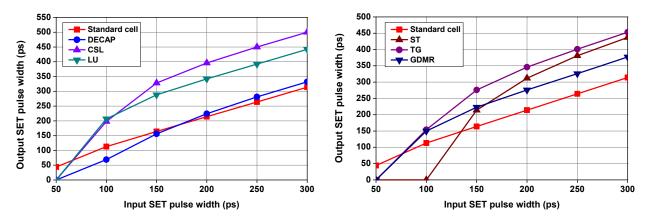

| Figure 5. 17: | Output SET pulse width as a function of input SET pulse width, for                                 |     |

|               | NAND2_x1 gate and hardening configurations with size factor x4                                     | 151 |

| Figure 5. 18: | Output SET pulse width as a function of input SET pulse width, for NOR2_x1                         |     |

|               | gate and hardening configurations with size factor x4                                              | 151 |

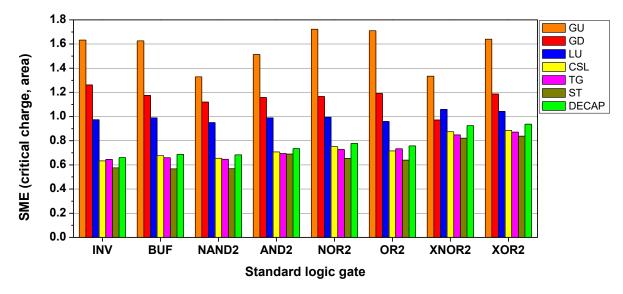

| Figure 5. 19: | SET mitigation efficiency of analyzed hardening techniques considering the                         |     |

|               | relation between critical charge and area overhead, for size factor x1 of                          |     |

|               | hardening configurations (higher SME value is better)                                              | 155 |

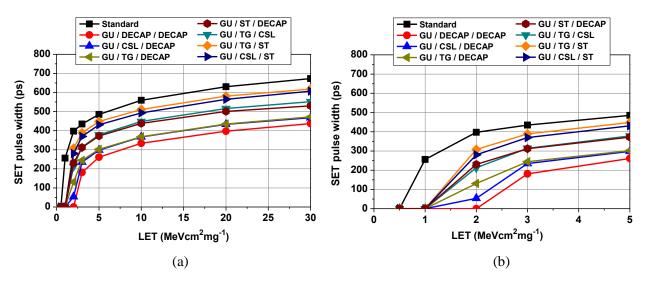

| Figure 5. 20: | SET pulse width at the output of a 10-gate NAND-NOR path as a function of                          |     |

|               | LET, for standard (non-hardened) path and for path with various combi-                             |     |

|               | nations of mitigation techniques: (a) for LET from 0.5 to 30 MeVcm <sup>2</sup> mg <sup>-1</sup> , |     |

|               | and (b) for LET from 0.5 to 5 MeVcm <sup>2</sup> mg <sup>-1</sup>                                  | 156 |

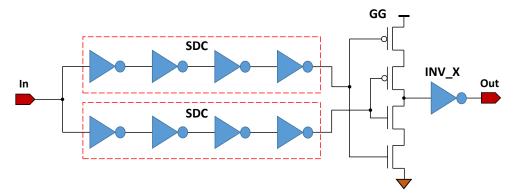

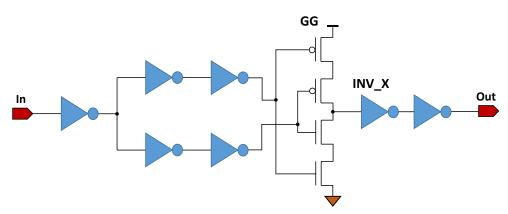

| Figure 5. 21: | SET mitigation in standard delay cells with complete duplication                                   | 158 |

| Figure 5. 22: | SET mitigation in standard delay cells with partial duplication                                    |     |

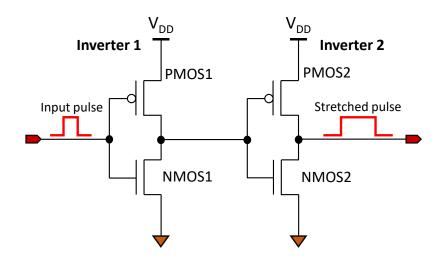

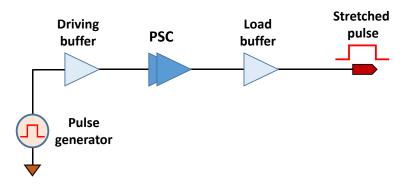

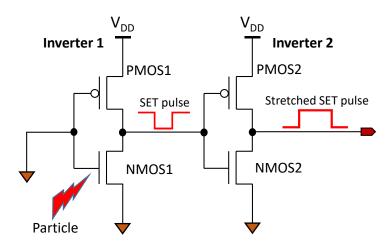

| Figure 6. 1:  | A two-inverter pulse stretching cell (PSC)                                                         | 164 |

| Figure 6. 2:  | Proposed symbol of two-inverter pulse stretching cell (PSC)                                        | 165 |

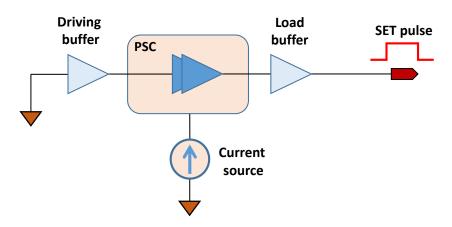

| Figure 6. 3:  | Simulation setup for analysis of normal operation of PSC                                           | 166 |

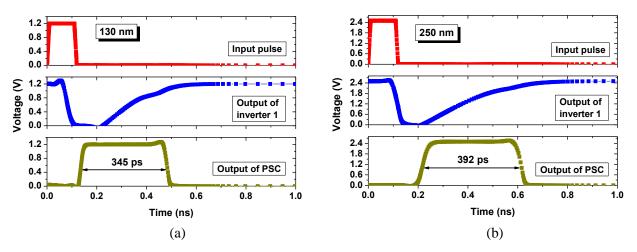

| Figure 6. 4:  | Stretching of 100 ps pulse with a single PSC in 130 nm and 250 nm techno-                          |     |

|               | logies                                                                                             | 167 |

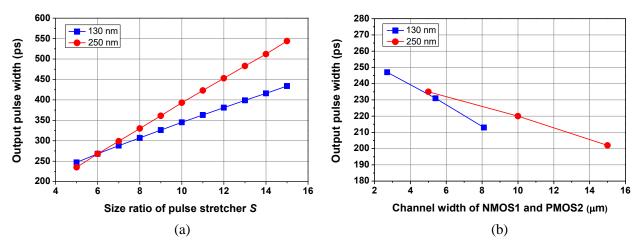

| Figure 6. 5:  | Output pulse width as a function of: (a) size factor S, (b) transistor size (for S                 |     |

|               | = 5)                                                                                               | 168 |

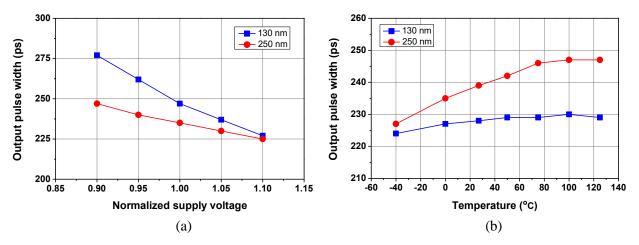

| Figure 6. 6:  | Output pulse width as a function of: (a) normalized supply voltage, (b)                            |     |

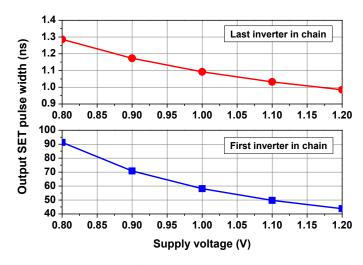

|               | temperature                                                                                        | 169 |

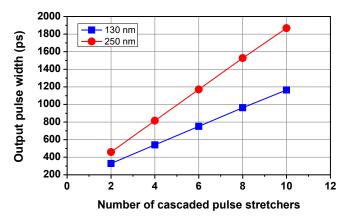

| Figure 6. 7:  | Output pulse width as a function of the number of cascaded pulse stretchers                        | 169 |

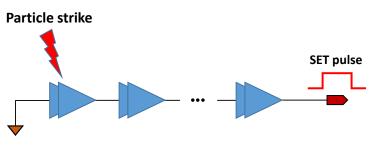

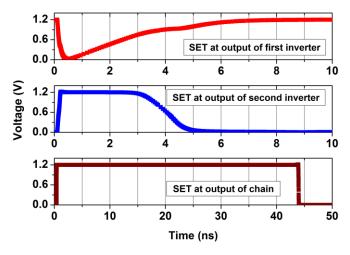

| Figure 6. 8:  | SET response of PSC due to a particle strike in off-state NMOS transistor                          | 170 |

| Figure 6. 9:  | Simulation setup for analysis of SET response of PSC                                               | 172 |

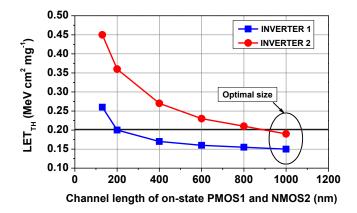

| Figure 6. 10: | Dependence of LET <sub>TH</sub> on channel length of on-state transistors (PMOS1 and               |     |

| -             | NMOS2)                                                                                             | 173 |

| Figure 6. 11: | Dependence of LET <sub>TH</sub> on channel width of off-state transistors (NMOS1 and               |     |

| -             | PMOS2)                                                                                             | 173 |

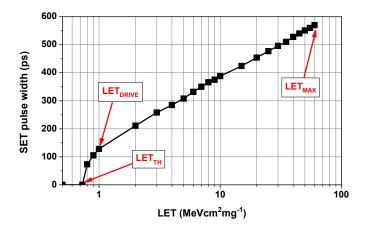

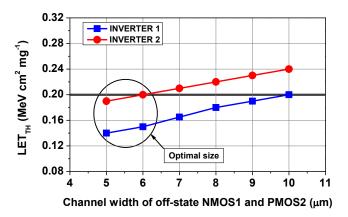

| Figure 6. 12: | Output pulse width of a single PSC as a function of LET                                            | 174 |

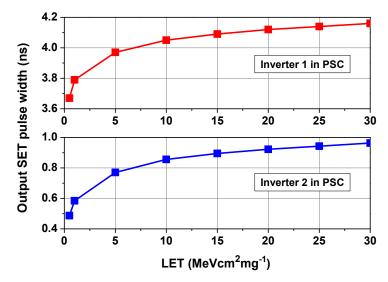

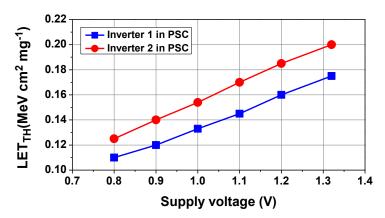

| Figure 6. 13: | LET <sub>TH</sub> for two inverters in a single PSC as a function of supply voltage                | 175 |

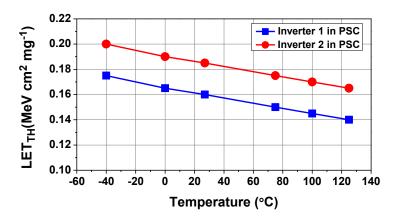

| Figure 6. 14: | LET <sub>TH</sub> for two inverters in a single PSC as a function of temperature                   | 175 |

| -             | Serial PSC configuration                                                                           |     |

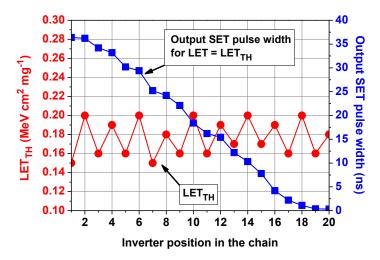

| e             | LET <sub>TH</sub> and corresponding output SET pulse width when current pulse is                   |     |

| -             | successively injected in each inverter in a chain composed of 20 pulse                             |     |

|               | stretching inverters (10 PSCs)                                                                     | 177 |

|               |                                                                                                    |     |

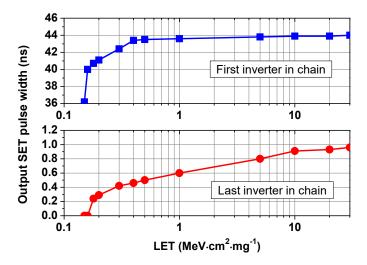

| Figure 6. 17: | Output SET pulse width as a function of LET, when the current pulse is                           |     |

|---------------|--------------------------------------------------------------------------------------------------|-----|

|               | injected in the first and last inverters of a chain composed of 20 pulse                         |     |

|               | stretching inverters (10 PSCs)                                                                   | 177 |

| Figure 6. 18: | SET response due to simultaneous current injection in two inverters of a 20-                     |     |

|               | inverter pulse stretching chain                                                                  | 178 |

| Figure 6. 19: | SET pulse width at the output of a 20-inverter pulse stretching chain, as a                      |     |

|               | function of supply voltage, for $LET = 10 \text{ MeV cm}^2 \text{mg}^{-1}$ and temperature of 27 |     |

|               | °C                                                                                               | 178 |

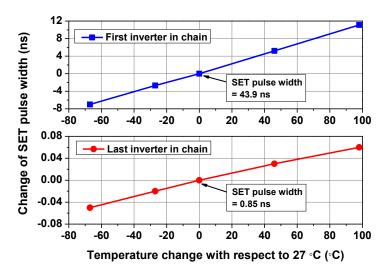

| Figure 6. 20: | Change of SET pulse width at the output of a 20-inverter pulse stretching                        |     |

|               | chain, as a function of temperature, for LET = $10 \text{ MeV cm}^2 \text{mg}^{-1}$ and supply   |     |

|               | voltage of 1.2 V                                                                                 | 179 |

| Figure 6. 21: | Parallel PSC configuration                                                                       |     |

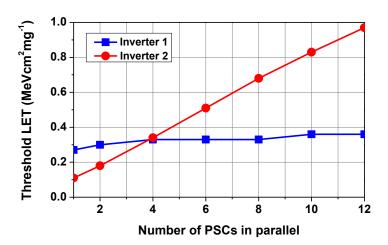

| Figure 6. 22: | Threshold LET of Inverter 1 and Inverter 2 in a PSC, for different number of                     |     |

|               | PSCs connected in parallel                                                                       |     |

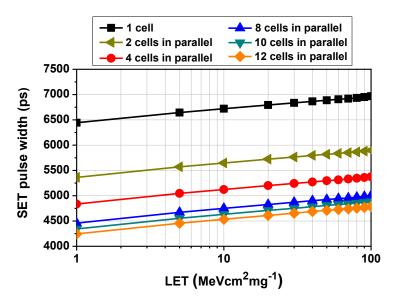

| Figure 6. 23: | SET pulse width as a function of LET and number of cells connected in                            |     |

|               | parallel, when the current pulse is injected in second inverter in PSC                           |     |

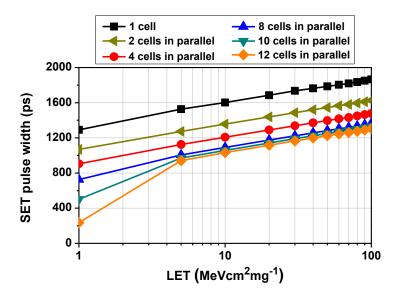

| Figure 6. 24: | SET pulse width as a function of LET and number of cells connected in                            |     |

|               | parallel, when the current pulse is injected in second inverter in PSC                           |     |

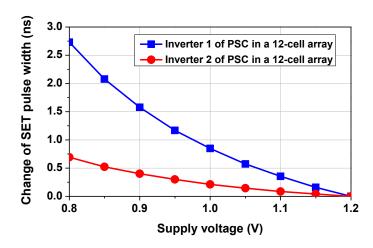

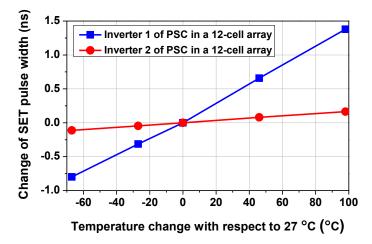

| Figure 6. 25: | Change of SET pulse width at the output of one PSC in a 12-cell parallel                         |     |

|               | array, as a function of supply voltage and temperature, for LET = $10$                           |     |

|               | MeVcm <sup>2</sup> mg <sup>-1</sup>                                                              |     |

| Figure 6. 26: | Change of SET pulse width at the output of one PSC in a 12-cell parallel                         |     |

|               | array, as a function of supply voltage and temperature, for LET = $10$                           |     |

|               | MeVcm <sup>2</sup> mg <sup>-1</sup>                                                              |     |

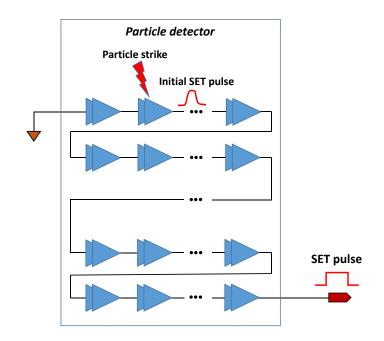

| Figure 6. 27: | Particle detector based on a long PSC chain                                                      |     |

| Figure 6. 28: | Readout circuit for particle detector based on a long PSC chain                                  |     |

| Figure 6. 29: | Particle detector based on multiple short PSC chains                                             |     |

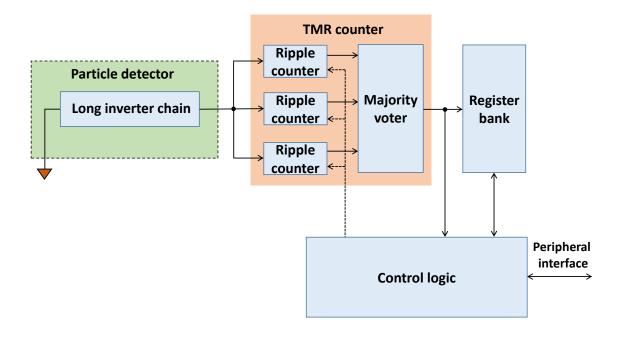

| Figure 6. 30: | Readout circuit for particle detector based on multiple short PSC chains                         |     |

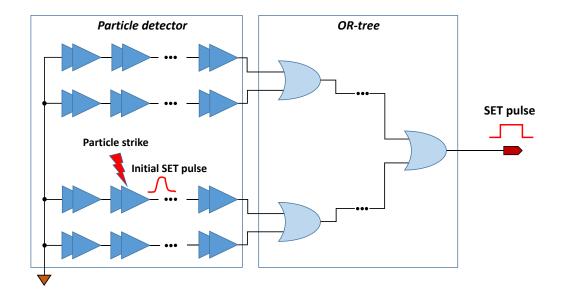

| e             | Particle detector based on PSCs connected in parallel                                            |     |

| Figure 6. 32: | Readout circuit for particle detector based on PSCs connected in parallel                        |     |

| Figure 6. 33: | A self-adaptive microprocessor platform with online SER monitoring                               | 194 |

|               |                                                                                                  |     |

# List of Tables

| Table 2. 1:   | Measured SET pulse widths for bulk CMOS technologies                                                                        |     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3. 1:   | Summary of methodologies for SET characterization of standard cell libraries                                                | 41  |

| Table 3. 2:   | Comparison of SET current models                                                                                            | 47  |

| Table 3. 3:   | Comparison of gate-level SET mitigation techniques                                                                          | 60  |

| Table 3. 4:   | Comparison of soft error (particle) detectors                                                                               |     |

| Table 4. 1:   | Parameters analyzed in simulations                                                                                          | 73  |

| Table 4. 2:   | Critical charge for INV gate with driving strengths x1, x2 and x4, for various load                                         |     |

|               | configurations and low input level                                                                                          | 77  |

| Table 4. 3:   | Q <sub>CRIT</sub> for output node of NAND3                                                                                  |     |

| Table 4. 4:   | Q <sub>CRIT</sub> for output node of AND3                                                                                   |     |

| Table 4. 5:   | Q <sub>CRIT</sub> for output node of NAND4                                                                                  |     |

| Table 4. 6:   | Q <sub>CRIT</sub> for output node of AND4                                                                                   |     |

| Table 4. 7:   | Nominal SER for INV_x1, for corner cases for supply voltage and temperature                                                 |     |

| Table 4. 8:   | Nominal SER for logic gates with driving strengths x1 and x2 ( $V_{DD} = 1.2 \text{ V}$ , $T_{EMP} = 27 ^{\circ}\text{C}$ ) | 83  |

| Table 4. 9:   | Channel width (W) and length (L) for transistors in SDCs                                                                    |     |

|               | SET pulse widths at the outputs of standard logic cells with driving streight x1,                                           |     |

| 1 auto 4. 10. | when the current is injected in the output node                                                                             | 01  |

| Table 4 11.   | SET pulse width at the output of $INV_x1$ in terms of supply voltage, for positive                                          |     |

| 1 4010 4. 11. | input pulses                                                                                                                | 95  |

| Table 4 12.   | SET pulse width at the output of BUF_x1 in terms of supply voltage, for positive                                            |     |

| 10010 4. 12.  | input pulses                                                                                                                | 95  |

| Table 4 13.   | SET pulse width at the outputs of INV and BUF gates, in terms of temperature, for                                           |     |

| 1000 4.15.    | $V_{DD} = 1.2$ V and positive input pulse of 200 ps                                                                         | 95  |

| Table 4 14.   | SET pulse width at the outputs of NAND and AND gates, in terms of supply vol-                                               |     |

| 1 4010 4. 14. | tage, for positive input pulse of 200 ps                                                                                    | 96  |

| Table 4 15.   | SET pulse width at the outputs of NAND and AND gates, in terms of temperature,                                              |     |

| 1000 4.15.    | for positive input pulse of 200 ps                                                                                          | 97  |

| Table 4 16.   | SET pulse widths at the outputs of logic gates, for positive and negative input                                             |     |

| 1000 4.10.    | pulses of 50, 100 and 200 ps (for driving strength $x_1$ , INV_ $x_1$ as a load gate, $V_{DD}$                              |     |

|               | = 1.2 V and $T_{\text{EMP}}$ = 27 °C)                                                                                       |     |

| Table 4 17.   | SET pulse widths at the outputs of combinational paths, for positive and negative                                           |     |

| 1 4010 4. 17. | input pulses of 200 ps, for Low-VT ( $V_{DD} = 1.08$ V, $T_{EMP} = -40$ °C), Typical-VT                                     |     |

|               | $(V_{DD} = 1.2 \text{ V}, T_{EMP} = 25 \text{ °C})$ and High-VT $(V_{DD} = 1.32 \text{ V}, T_{EMP} = 125 \text{ °C})$       | 90  |

| Table 4 18.   | Comparison of critical charge obtained with proposed model and SPICE simula-                                                |     |

| 1000 4. 10.   | tions, for different setting for INV, NAND2 and NOR2 gates                                                                  | 104 |

| Table 4 19.   | Description of combinational paths used for model verification                                                              |     |

|               | Comparison of SET propagation through combinational paths from Table 4.19,                                                  |     |

| 1 4010 7, 20, | with proposed model and SPICE simulations, when the current pulse with LET =                                                |     |

|               | $10 \text{ MeV cm}^2\text{mg}^{-1}$ is injected in the output node of first gate in each path                               | 112 |

|               | To the vent mg is injected in the output node of mst gate in each path                                                      |     |

|              | Comparison of critical charge obtained with proposed model and SPICE simula-                            |     |

|--------------|---------------------------------------------------------------------------------------------------------|-----|

|              | tions for C-element designed in 130 and 65 nm technologies                                              | 115 |

|              | Comparison of critical charge obtained with proposed model and SPICE simula-                            |     |

|              | tions for SEL protection switch designed in 130 and 250 nm technologies                                 | 118 |

| Table 4. 23: | Number of simulation runs for characterization of SET generation sensitivity of                         |     |

|              | standard logic cells, for standard and optimized characterization approaches                            | 121 |

| Table 4. 24: | Number of LUTs and elements in LUTs for storing the critical charge values for                          |     |

|              | one gate type, obtained from standard characterization                                                  | 123 |

| Table 4. 25: | Number of LUTs and elements in LUTs for storing the model coefficients for one                          |     |

|              | gate type                                                                                               |     |

|              | Transistor size and area for decoupling cells in 130 nm technology                                      | 132 |

| Table 5. 2:  | Critical charge for standard logic gates without and with applied decoupling cells,                     |     |

|              | when the current pulse is injected successively in the output node of target gate                       |     |

|              | and in decoupling cells connected to the gate (for the most sensitive input levels)                     | 136 |

| Table 5. 3:  | Width of SET pulse generated at the output of logic gates with driving strength x1,                     |     |

|              | when the current pulse with $LET = 1 \text{ MeV cm}^2 \text{mg}^{-1}$ is injected in the output of each |     |

|              | gate (for the most sensitive input levels)                                                              | 139 |

| Table 5. 4:  | Minimum pulse width that can propagate through a logic gate with drive strength                         |     |

|              | x1, without and with decoupling cells                                                                   |     |

|              | Gate-level hardening configurations analyzed in this work                                               | 144 |

| Table 5. 6:  | Critical charge at the output node of a target gate (for the most sensitive input                       |     |

|              | levels)                                                                                                 | 146 |

|              | Generated SET pulse width for standard logic gates without hardening and with                           |     |

|              | hardening configurations with size factor x1, for $LET = 1 \text{ MeV}\text{cm}^2\text{mg}^{-1}$        | 148 |

|              | Propagated SET pulse width for standard logic gates without hardening and with                          |     |

|              | hardening configurations with size factor x1, for positive input pulse of 100 ps                        | 150 |

| Table 5. 9:  | Normalized area for standard logic gates without and with hardening configura-                          |     |

|              | tions with size factor x1                                                                               | 152 |

| Table 5. 10: | Propagation delay of a chain composed of driving buffer, target gate and load inv-                      |     |

|              | erter, without and with hardening configurations with size factor x1                                    | 153 |

| Table 5. 11: | Normalized power overhead for standard logic gates without hardening and with                           |     |

|              | applied hardening configurations with size factor x1                                                    | 153 |

| Table 5. 12: | SET pulse width at the output of NAND-NOR path for $LET = 30 \text{ MeV cm}^2\text{mg}^{-1}$ ,          |     |

|              | propagation delay of the path without and with mitigation configurations, and                           |     |

|              | corresponding SET mitigation efficiency SME (SET pulse width, delay)                                    | 157 |

|              | SET pulse width at the output of standard delay cells, for standard version and two                     |     |

|              | hardened configurations (for low input level and LET = 30 MeVcm <sup>2</sup> mg <sup>-1</sup> )         | 159 |

| Table 5. 14: | Normalized area and propagation delay for standard delay cells (SDC) with driving                       |     |

|              | strength x1 and x2, and corresponding hardened configurations (SDC_CD and                               |     |

|              | SDC_PD)                                                                                                 |     |

|              | LET <sub>TH</sub> for standard logic cells and SRAM cell in IHP's 130 nm technology                     |     |

| Table 6. 2:  | Transistor sizes for parallel PSC configuration                                                         |     |

| Table 6. 3:  | SET pulse width ranges for a PSC in a 12-cell array                                                     |     |

| Table 6. 4:  | SET pulse width ranges for standard cells in 130 nm library                                             |     |

| Table 6. 5:  | Comparison of proposed particle detector with existing solutions                                        | 192 |

# List of Acronyms

| ASETAnalog Single Event TransientASICApplication Specific Integrated CircuitBBICSBulk Built-in Current SensorCECumulative EffectsCMOSComplementary Metal Oxide SemiconductorCPUCentral Processing UnitCSLCharge Sharing LogicDDDisplacement DamageDECAPDecoupling cellDMRDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEnror Detection and CorrectionELTEnclosed Layout TransistorESSCEuropean Space AgencyFSMFinFeld Effect TransistorFITFin Field Effect TransistorFITGate DuplicationGDMRGate DuplicationGDMRGate UplicationGDMRGate UplicationGDMRGate UplicationGUInternational Roadmap for Devices and SystemsItDLInterational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad UpiszingLULoakup Table | ALPEN  | Alpha Particle Source Drain Penetration       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|

| BBICSBulk Built-in Current SensorCECumulative EffectsCMOSComplementary Metal Oxide SemiconductorCPUCentral Processing UnitCSLCharge Sharing LogicDDDisplacement DamageDECAPDecoupling cellDMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACEuropean Space AgencyESAEuropean Space AgencyESDElectrostatic DischargeFinFETFin Field Effect TransistorFTTGate DuplicationGDMRGuarded Dual Modular RedundancyGDUGate DuplicationFITFiallures in TimeGDGate UpsizingHILHardware Description LanguageICInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad Upsizing                                                                                 | ASET   | Analog Single Event Transient                 |

| CECumulative EffectsCMOSComplementary Metal Oxide SemiconductorCPUCentral Processing UnitCSLCharge Sharing LogicDDDisplacement DamageDECAPDecoupling cellDMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLError Detection and CorrectionEDACError Detection and CorrectionESAEuropean Space AgencyESQElectrostatic DischargeFinFETFin Field Effect TransistorFITGate OpplicationGDMRGated Dual Modular RedundancyGPUGatel OpplicationGLGate UppizingHDLHardware Description LanguageICInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad Upsizing                                                                                                                     | ASIC   | Application Specific Integrated Circuit       |

| CMOSComplementary Metal Oxide SemiconductorCPUCentral Processing UnitCSLCharge Sharing LogicDDDisplacement DamageDECAPDecoupling cellDMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACError Detection and CorrectionELTEnclosed Layout TransistorESAEuropean Space AgencyESCCEuropean Space Components CoordinationESDElectrostatic DischargeFinFETFin Field Effect TransistorFITGate DuplicationGDGate UpilcationGDUGraphics Processing UnitGUGate UpsizingHDLHardware Description LanguageICInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad Upsizing                                                                                    | BBICS  | Bulk Built-in Current Sensor                  |

| CPUCentral Processing UnitCSLCharge Sharing LogicDDDisplacement DamageDECAPDecoupling cellDMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACError Detection and CorrectionELTEuropean Space AgencyESCEuropean Space Components CoordinationESDElectrostatic DischargeFinFETFin Field Effect TransistorFITGate DuplicationGDGate DuplicationGDUGraphics Processing UnitGUGate UpsizingHDLIntegrated CircuitIRDSInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad Upsizing                                                                                                                                                                     | CE     | Cumulative Effects                            |

| CSLCharge Sharing LogicDDDisplacement DamageDECAPDecoupling cellDMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACError Detection and CorrectionELTEnclosed Layout TransistorESAEuropean Space AgencyESDElectrostatic DischargeFinFETFin Field Effect TransistorFITSaitures in TimeGDGate DuplicationGDUGraphics Processing UnitGUGate UpsizingHDLIntegrated CircuitIRDSInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad Upsizing                                                                                                                                                                                                           | CMOS   | Complementary Metal Oxide Semiconductor       |

| DDDisplacement DamageDECAPDecoupling cellDMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACError Detection and CorrectionELTEnclosed Layout TransistorESAEuropean Space AgencyESCCEuropean Space Components CoordinationESDElectrostatic DischargeFinFETFailures in TimeGDGate DuplicationGDWRGuarded Dual Modular RedundancyGPUGate UpsizingHDLHardware Description LanguageICInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad Upsizing                                                                                                                                                                                                    | CPU    | Central Processing Unit                       |

| DECAPDecoupling cellDMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACEmitter Coupled LogicEDACEnclosed Layout TransistorELTEnclosed Layout TransistorESAEuropean Space AgencyESDElectrostatic DischargeFinFETFailures in TimeGDGate DuplicationGDMRGated Dual Modular RedundancyGPUGraphics Processing UnitGUGate UpsizingHDLHardware Description LanguageICInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULinear Energy Transfer                                                                                                                                                                                                             | CSL    | Charge Sharing Logic                          |

| DMRDual Modular RedundancyDSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACError Detection and CorrectionELTEnclosed Layout TransistorESAEuropean Space AgencyESDElectrostatic DischargeFinFETFin Field Effect TransistorFITFailures in TimeGDGate DuplicationGDWRGated Dual Modular RedundancyGPUGraphics Processing UnitGUIntegrated CircuitIRDSIntegrated CircuitIRDSInternational Roadmap for Devices and SystemsLETLinear Energy TransferLULoad Upsizing                                                                                                                                                                                                                                    | DD     | Displacement Damage                           |

| DSETDigital Single Event TransientDVFSDynamic Voltage and Frequency ScalingECLEmitter Coupled LogicEDACError Detection and CorrectionELTEnclosed Layout TransistorESAEuropean Space AgencyESDElectrostatic DischargeFinFETFin Field Effect TransistorGDGate DuplicationGDGate DuplicationGDUGate dupsizingHDLIntegrated CircuitIRDSIntegrated CircuitLETLinear Energy TransferLULoad Upsizing                                                                                                                                                                                                                                                                                                                                                          | DECAP  | Decoupling cell                               |