### Dissertation

# One-Sided Communication on a Non-Cache-Coherent Many-Core Architecture

eingereicht von

Steffen Christgau, M.Sc.

vorlegt der Mathematisch-Naturwissenschaftlichen Fakultät der Universität Potsdam

zur Erlangung des akademischen Grades Doktor der Naturwissenschaften (Dr. rer. nat.) in der Wissenschaftsdisziplin Betriebssysteme und Verteilte Systeme

> angefertigt am Institut für Informatik und Computational Science Professur für Betriebssysteme und Verteilte Systeme

> > Potsdam, den 1. Februar 2017

This work is licensed under a Creative Commons License: Attribution – Noncommercial 4.0 International To view a copy of this license visit http://creativecommons.org/licenses/by-nc/4.0/

#### **Supervisor**

Prof. Dr. Bettina Schnor

#### Referees

Prof. Dr. Bettina Schnor Prof. Dr. Wolfgang Karl Prof. Dr. Wolfgang E. Nagel

#### **Examining Board**

Prof. Dr. Andreas Polze

Prof. Dr. Tobias Scheffer (head) Prof. Dr.-Ing. Benno Stabernack

#### **Faculty Delegate**

Prof. Dr. Arkady Pikovsky

Christgau, Steffen christgau@cs.uni-potsdam.de One-Sided Communication on a Non-Cache-Coherent Many-Core Architecture Dissertation, Institute for Computer Science University of Potsdam, February 2017

Published online at the Institutional Repository of the University of Potsdam: URN urn:nbn:de:kobv:517-opus4-403100 http://nbn-resolving.de/urn:nbn:de:kobv:517-opus4-403100

#### **Abstract**

Contemporary multi-core processors are parallel systems that also provide shared memory for programs running on them. Both the increasing number of cores in so-called many-core systems and the still growing computational power of the cores demand for memory systems that are able to deliver high bandwidths. Caches are essential components to satisfy this requirement. Nevertheless, hardware-based cache coherence in many-core chips faces practical limits to provide both coherence and high memory bandwidths. In addition, a shift away from global coherence can be observed. As a result, alternative architectures and suitable programming models need to be investigated.

This thesis focuses on fast communication for non-cache-coherent many-core architectures. Experiments are conducted on the Single-Chip Cloud Computer (SCC), a non-cache-coherent many-core processor with 48 mesh-connected cores. Although originally designed for message passing, the results of this thesis show that shared memory can be efficiently used for one-sided communication on this kind of architecture. One-sided communication enables data exchanges between processes where the receiver is not required to know the details of the performed communication. In the notion of the Message Passing Interface (MPI) standard, this type of communication allows to access memory of remote processes. In order to support this communication scheme on non-cache-coherent architectures, both an efficient *process synchronization* and a *communication scheme* with software-managed cache coherence are designed and investigated.

The process synchronization realizes the concept of the general active target synchronization scheme from the MPI standard. An existing classification of implementation approaches is extended and used to identify an appropriate class for the non-cache-coherent shared memory platform. Based on this classification, existing implementations are surveyed in order to find beneficial concepts, which are then used to design a lightweight synchronization protocol for the SCC that uses shared memory and uncached memory accesses. The proposed scheme is not prone to process skew and also enables direct communication as soon as both communication partners are ready. Experimental results show very good scaling properties and up to five times lower synchronization latency compared to a tuned message-based MPI implementation for the SCC.

For the *communication*, *SCOSCo*, a shared memory approach with software-managed cache coherence, is presented. According requirements for the coherence that fulfill

MPI's separate memory model are formulated, and a lightweight implementation exploiting SCC hard- and software features is developed. Despite a discovered malfunction in the SCC's memory subsystem, the experimental evaluation of the design reveals up to five times better bandwidths and nearly four times lower latencies in micro-benchmarks compared to the SCC-tuned but message-based MPI library. For application benchmarks, like a parallel 3D fast Fourier transform, the runtime share of communication can be reduced by a factor of up to five. In addition, this thesis postulates beneficial hardware concepts that would support software-managed coherence for one-sided communication on future non-cache-coherent architectures where coherence might be only available in local subdomains but not on a global processor level.

#### Zusammenfassung

Aktuelle Mehrkernprozessoren stellen parallele Systeme dar, die den darauf ausgeführten Programmen gemeinsamen Speicher zur Verfügung stellen. Sowohl die ansteigende Kernanzahlen in sogenannten Vielkernprozessoren (many-core processors) als auch die weiterhin steigende Leistungsfähigkeit der einzelnen Kerne erfordert hohe Bandbreiten, die das Speichersystem des Prozessors liefern muss. Hardware-basierte Cache-Kohärenz stößt in aktuellen Vielkernprozessoren an Grenzen des praktisch Machbaren. Dementsprechend müssen alternative Architekturen und entsprechend geeignete Programmiermodelle untersucht werden.

In dieser Arbeit wird der Single-Chip Cloud Computer (SCC), ein nicht-cachekohärenter Vielkernprozessor betrachtet, der aus 48, über ein Gitternetzwerk verbundenen Kernen besteht. Obwohl der Prozessor für nachrichten-basierte Kommunikation entwickelt worden ist, zeigen die Ergebnisse dieser Arbeit, dass einseitige Kommunikation auf Basis gemeinsamen Speichers effizient auf diesem Architekturtyp realisiert werden kann. Einseitige Kommunikation ermöglicht Datenaustausch zwischen Prozessen, bei der der Empfänger keine Details über die stattfindende Kommunikation besitzen muss. Im Sinne des MPI-Standards ist so ein Zugriff auf Speicher entfernter Prozesse möglich. Zur Umsetzung dieses Konzepts auf nicht-kohärenten Architekturen werden in dieser Arbeit sowohl eine effiziente *Prozesssynchronisation* als auch ein Kommunikationsschema auf Basis von software-basierter Cache-Kohärenz erarbeitet und untersucht.

Die Prozesssynchronisation setzt das Konzept der general active target synchronization aus dem MPI-Standard um. Ein existierendes Klassifikationsschema für dessen Implementierungen wird erweitert und zur Identifikation einer geeigneten Klasse für die nicht-kohärente Plattform des SCC verwendet. Auf Grundlage der Klassifikation werden existierende Implementierungen analysiert, daraus geeignete Konzepte extrahiert und ein leichtgewichtiges Synchronisationsprotokoll für den SCC entwickelt, das sowohl gemeinsamen Speicher als auch ungecachete Speicherzugriffe verwendet. Das vorgestellte Schema ist nicht anfällig für Verzögerungen zwischen Prozessen und erlaubt direkte Kommunikation sobald beide Kommunikationspartner dafür bereit sind. Die experimentellen Ergebnisse zeigen ein sehr gutes Skaliserungsverhalten und eine fünffach geringere Latenz für die Prozesssynchronisation im Vergleich zu einer auf Nachrichten basierenden MPI-Implementierung des SCC.

Für die Kommunikation wird mit SCOSCo ein auf gemeinsamen Speicher und software-basierter Cache-Kohärenz basierenden Konzept vorgestellt. Entsprechen-

de Anforderungen an die Kohärenz, die dem MPI-Standard entsprechen, werden aufgestellt und eine schlanke Implementierung auf Basis der Hard- und Software-Funktionalitäten des SCCs entwickelt. Trotz einer aufgedecktem Fehlfunktion im Speichersubsystem des SCC kann in den experimentellen Auswertungen von Mikrobenchmarks eine fünffach verbesserte Bandbreite und eine nahezu vierfach verringerte Latenz beobachtet werden. In Anwendungsexperimenten, wie einer dreidimensionalen schnellen Fourier-Transformation, kann der Anteil der Kommunikation an der Laufzeit um den Faktor fünf reduziert werden. In Ergänzung dazu werden in dieser Arbeit Konzepte aufgestellt, die in zukünftigen Architekturen, die Cache-Kohärenz nicht auf einer globalen Ebene des Prozessors liefern können, für die Umsetzung von software-basierter Kohärenz für einseitige Kommunikation hilfreich sind.

## **Acknowledgements**

At this point, I would like to express my thanks to some people who supported me in the process of creating this thesis. First of all, I thank Bettina Schnor for supervising me in the past years and for the vivid and fruitful discussions we had. Second, this thesis would not have been possible without the provision of an SCC system by Intel. For their support on SCC matters, thanks go to Werner Haas and Michael Riepen, Intel engineers at the time. My colleagues from the sun deck at the Institute for Computational Science deserve credits for the nice time we had together in the past years: I want to point out Jörg Jung and Sven Schindler, who shared the office with me from time to time, but who also caused (sometimes unproductive, yet welcomed) distractions when they stayed in the room. The latter applies to Marius Lindauer as well. I do not want to forget Klemens Kittan to thank him for his friendly and infrastructure support, like shutting down and turning the SCC on again due to reoccurring, nasty and campus-wide power shutdowns. Thanks goes also to Sebastian Menski for his experimental support in the very early stages of the thesis, and to Martin Ohmann for his work on the FFT benchmark during his diploma thesis. In addition, Sven Schindler and Susi Kirschbaum have to be mentioned for their individual support in language matters.

## **Contents**

| 1 | Intro                                           | duction |                                                   | 1  |  |

|---|-------------------------------------------------|---------|---------------------------------------------------|----|--|

|   | 1.1                                             | Motiv   | ration                                            | 2  |  |

|   | 1.2                                             | Outlin  | ne                                                | 4  |  |

|   | 1.3                                             | Contr   | ributions                                         | 4  |  |

|   | 1.4                                             | Public  | cations                                           | 6  |  |

|   | 1.5                                             | Scope   |                                                   | 6  |  |

|   | 1.6                                             | Conve   | entions                                           | 7  |  |

| 2 | Back                                            | ground  |                                                   | 9  |  |

|   | 2.1                                             | Shared  | d Memory Processors                               | 9  |  |

|   |                                                 | 2.1.1   | Memory Consistency and Coherence                  | 10 |  |

|   |                                                 | 2.1.2   | Limitations of Cache Coherence                    | 13 |  |

|   | 2.2                                             | The Ir  | ntel Single-Chip Cloud Computer                   | 16 |  |

|   |                                                 | 2.2.1   | Architectural Overview                            | 16 |  |

|   |                                                 | 2.2.2   | Memory Subsystem                                  | 18 |  |

|   |                                                 | 2.2.3   | Message Passing Buffers                           | 21 |  |

|   |                                                 | 2.2.4   | Memory Types                                      | 21 |  |

|   |                                                 | 2.2.5   | Configuration and Atomic Registers                | 25 |  |

|   |                                                 | 2.2.6   | Software Environment                              | 26 |  |

|   | 2.3 Programming Models for Many-core Processors |         |                                                   |    |  |

|   |                                                 | 2.3.1   | Message Passing Concepts                          | 30 |  |

|   |                                                 | 2.3.2   | The Message Passing Interface Standard            | 31 |  |

|   |                                                 | 2.3.3   | Message Passing on the Single-Chip Cloud Computer | 33 |  |

|   |                                                 | 2.3.4   | One-sided Communication                           | 35 |  |

|   |                                                 | 2.3.5   | One-Sided Communication in the MPI standard       | 38 |  |

|   |                                                 | 2.3.6   | Discussion                                        | 40 |  |

|   | 2.4                                             | Relate  | ed Work                                           | 41 |  |

|   |                                                 | 2.4.1   | Coherence and Consistency in Distributed Systems  | 41 |  |

|   |                                                 | 2.4.2   | Coherence via Release Consistency                 | 41 |  |

|   |                                                 | 2.4.3   | Shared Virtual Memory                             | 43 |  |

|   |                                                 | 2.4.4   | Object-based approaches                           | 47 |  |

### Contents

|   |       | 2.4.5                              | Software-Based Cache Coherence        | 49  |

|---|-------|------------------------------------|---------------------------------------|-----|

|   | 2.5   | Conclu                             | usion                                 | 51  |

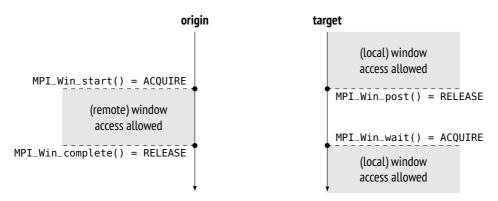

| 3 | Synch | on for MPI One-Sided Communication | 53                                    |     |

|   | 3.1   | Backgr                             | round: MPI Process Synchronization    | 53  |

|   |       | 3.1.1                              | Synchronization Epochs                | 55  |

|   |       | 3.1.2                              | Fence Synchronization                 | 56  |

|   |       | 3.1.3                              | General Active Target Synchronization | 57  |

|   |       | 3.1.4                              | Passive Target Synchronization        | 59  |

|   | 3.2   | Classif                            | ication of Implementation Methods     | 61  |

|   |       | 3.2.1                              | Deferred Method                       | 61  |

|   |       | 3.2.2                              | Immediate Method                      | 62  |

|   |       | 3.2.3                              | Trigger-Only Method                   | 63  |

|   |       | 3.2.4                              | Discussion                            | 63  |

|   | 3.3   | Survey                             | of Synchronization Implementations    | 64  |

|   |       | 3.3.1                              | MPICH                                 | 64  |

|   |       | 3.3.2                              | MVAPICH                               | 67  |

|   |       | 3.3.3                              | Open MPI                              | 69  |

|   |       | 3.3.4                              | FoMPI                                 | 73  |

|   |       | 3.3.5                              | NEON                                  | 76  |

|   |       | 3.3.6                              | Summary                               | 80  |

|   | 3.4   | Synchi                             | ronization for the SCC                | 81  |

|   |       | 3.4.1                              | Analysis of RCKMPI's Implementation   | 82  |

|   |       | 3.4.2                              | Related Work                          | 84  |

|   |       | 3.4.3                              | Design Overview                       | 86  |

|   |       | 3.4.4                              | Data Structures                       | 87  |

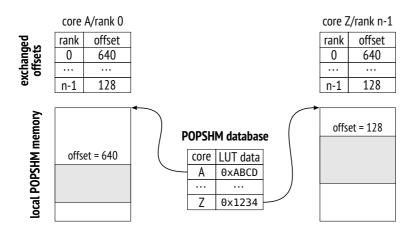

|   |       | 3.4.5                              | Window Database                       | 88  |

|   |       | 3.4.6                              | Window Creation                       | 93  |

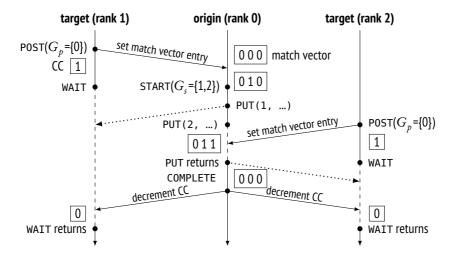

|   |       | 3.4.7                              | Start and Post Operations             | 94  |

|   |       | 3.4.8                              | Polling the Match Vector              | 96  |

|   |       | 3.4.9                              | Complete and Wait Operations          | 97  |

|   |       | 3.4.10                             | Summary                               | 98  |

|   | 3.5   | Experi                             | mental Evaluation                     | 99  |

|   |       | 3.5.1                              | Environment                           | 99  |

|   |       | 3.5.2                              | Functional Tests                      | 100 |

|   |       | 3.5.3                              | Benchmark Methodology                 | 101 |

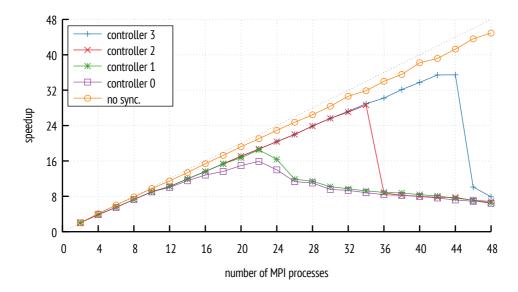

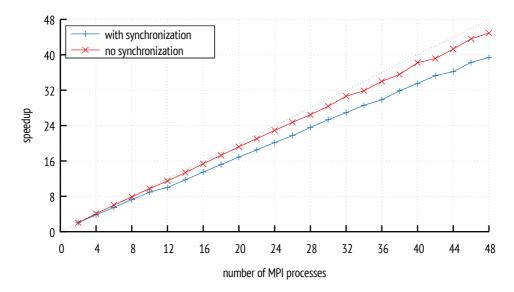

|   |       | 3.5.4                              | Scaling                               | 103 |

|   |       | 3.5.5                              | Comparison with MPICH/RCKMPI          | 106 |

|   | 3.6   | Summ                               | arv                                   | 107 |

| 4 | Softw | vare-Mar                       | naged Cache Coherence for MPI One-Sided Communication | 109 |  |  |

|---|-------|--------------------------------|-------------------------------------------------------|-----|--|--|

|   | 4.1   | Backg                          | round                                                 |     |  |  |

|   |       | 4.1.1                          | MPI One-Sided Communication                           |     |  |  |

|   |       | 4.1.2                          | One-Sided Communication in RCKMPI                     | 114 |  |  |

|   |       | 4.1.3                          | Other MPI Implementations                             | 120 |  |  |

|   | 4.2   | SCOS                           | Co: An Approach for the Intel SCC                     | 123 |  |  |

|   |       | 4.2.1                          | Cache Coherence Management                            |     |  |  |

|   |       | 4.2.2                          | Memory Model                                          | 125 |  |  |

|   |       | 4.2.3                          | Requirements for MPI One-Sided Communication          | 126 |  |  |

|   |       | 4.2.4                          | Memory Type Considerations                            | 127 |  |  |

|   |       | 4.2.5                          | Implementation Sketch                                 | 130 |  |  |

|   | 4.3   | Imple                          | mentation                                             | 131 |  |  |

|   |       | 4.3.1                          | Window Creation                                       | 131 |  |  |

|   |       | 4.3.2                          | Communication Operations                              | 134 |  |  |

|   |       | 4.3.3                          | Management of the Cache Coherence                     | 134 |  |  |

|   | 4.4   | Exper                          | imental Evaluation                                    | 136 |  |  |

|   |       | 4.4.1                          | Functional Tests                                      | 136 |  |  |

|   |       | 4.4.2                          | Memory Performance                                    | 137 |  |  |

|   |       | 4.4.3                          | OSU Micro-Benchmarks                                  | 141 |  |  |

|   |       | 4.4.4                          | Three-Dimensional Fast Fourier Transform              | 144 |  |  |

|   |       | 4.4.5                          | Cellular Automaton                                    | 151 |  |  |

|   |       | 4.4.6                          | Summary                                               | 157 |  |  |

|   | 4.5   | Possib                         | ole Optimization                                      | 158 |  |  |

|   | 4.6   | Conclusions for Future Systems |                                                       |     |  |  |

|   |       | 4.6.1                          | Configurable Shared Memory and Memory Registration    | 159 |  |  |

|   |       | 4.6.2                          | Guaranteed Commit to RAM                              | 160 |  |  |

|   |       | 4.6.3                          | Selective Invalidation of Cache Lines                 | 161 |  |  |

|   |       | 4.6.4                          | Non-blocking Data Transfer                            | 162 |  |  |

|   | 4.7   | Summ                           | nary                                                  | 163 |  |  |

| 5 | Concl | lusions a                      | nd Outlook                                            | 165 |  |  |

|   | 5.1   | Result                         | ts and Discussion                                     | 165 |  |  |

|   | 5.2   | Future                         | e Work                                                | 167 |  |  |

| A | Empl  | oyed MP                        | PICH test cases                                       | 169 |  |  |

|   | A.1   | Succee                         | eded Test Cases                                       | 169 |  |  |

|   | A.2   | Failed                         | Test Cases                                            | 170 |  |  |

| В |       |                                | Extracts                                              | 171 |  |  |

|   | B.1   | Load a                         | and Store Latencies                                   | 171 |  |  |

## Contents

|       | B.2            | 2 GATS Synchronization Benchmark |     |  |  |

|-------|----------------|----------------------------------|-----|--|--|

|       | B.3            | Cellular Automaton               | 173 |  |  |

|       |                | B.3.1 Two-Sided Time Step Kernel | 173 |  |  |

|       |                | B.3.2 One-Sided Time Step Kernel | 173 |  |  |

|       | B.4            | Communication Patterns           | 174 |  |  |

| C     | Comp           | ompute Cluster Properties        |     |  |  |

| Index |                |                                  |     |  |  |

| Bib   | Bibliography 1 |                                  |     |  |  |

## 1 Introduction

Microprocessors and the main memory attached to them are the essential building blocks of computer systems. Over the last decades, the processor performance continuously increased by several orders of magnitude [14, p. 3]. In contrast, the performance of the main memory, which provides data to the processor, could not be improved that much and therefore created a large performance gap between these two essential components. To compensate that gap, several layers of *caches* — fast intermediate memories — were added between the processor and the main memory [14, pp. 72 ff.]. They hold recently used data that is accessed by the processors and hide the large access times of the main memory. Keeping the cache utilization as high as possible is critical to fully exploit the processor's processing capabilities [1, 15].

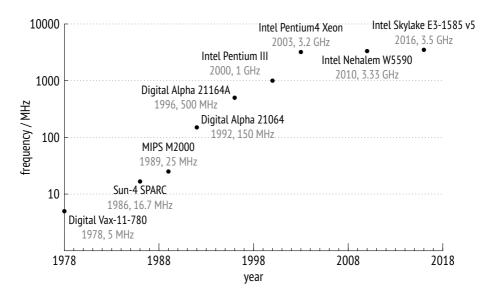

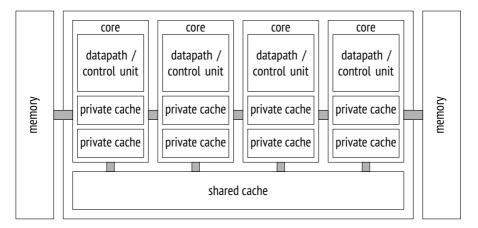

While several techniques for improving instruction processing contributed to the performance gains of processors, the clock rate has been the main driver. However, technical limits prevent further upscaling. In fact, the frequency of microprocessors stagnates since about 15 years as shown in Figure 1.1¹. To further increase the performance, the usage of *multi-core processors* became common at that time and they are ubiquitous by now. In this type of processors, the data path and control unit as well as caches are replicated and grouped in *cores* (see Figure 1.2). This enables parallel execution of programs on a single processor.

Besides the replication of some processor resources, other components are used by multiple cores. Usually, the cores are connected via an interconnect and share the main memory, although the memory might be distributed (see Figure 1.2). This enables programs to share data via the commonly used memory. The usage of this *shared memory* and the caches at the same time imposes an important problem. When a process accesses data, the information will be transparently saved inside the caches attached to the executing core. Thus, copies of the data from main memory are created. If more than one core accesses data in the shared memory, potential copies in the caches must be identified and an eventual modification must be handled such that

<sup>&</sup>lt;sup>1</sup>Additional data compared to [14, Fig 1.11] obtained from http://ark.intel.com/products/93742

Figure 1.1: Growth of processor frequency since 1978 (based on [14, Fig. 1.11]).

each process observes the most recent data. This task of maintaining the correct state of cached data is known as *cache coherence*.

#### 1.1 Motivation

Over the decades of processor design, several techniques were developed to improve the performance of a single processor core. Today's architectures are able to issue multiple memory accesses per clock cycle and also can load several machine words in parallel, e.g. to fetch data into their vector registers. If a data access causes a cache miss, i.e. the referenced item is not stored in the local caches, other caches must be checked for copies which are potentially modified. Similar, if a local write to shared data is encountered, other caches must be informed about that change. This causes traffic on the interconnect to keep the cached data coherent.

It has been shown that coherence traffic of so-called snooping protocols can exceed the capabilities of bus-based interconnects [16, 17]. A shift from pure snoop-based protocols, which require broadcasts [14, p. 364], to directory-based or mixed coherence schemes as well as different interconnects, such as point-to-point, ring, or mesh topologies, made multi-core processors less prone to contention by coherence traffic.

Figure 1.2: Schematic overview of a multi-core CPU with shared last level cache.

However, even on those architectures the implementation of coherence adds latency to memory accesses requiring a deep understanding to achieve good performance [18].

In addition to the challenge of efficient programming of large-scale coherence systems, two observations can be made.

First, advances in memory technology led to the integration of fast high-capacity on-chip memories that assist conventional main memory. This type of memory provides high bandwidth to the cores that share the processor die. However, the high bandwidth makes building a coherent multi-socket system practically impossible, because current coherent interconnects do not provide the required bandwidth to serve the coherence traffic. For the *Knights Landing* processor, a memory bandwidth of more than 400 GB/s is stated. Even if the coherence traffic is reduced, it exceeds the capacity of the QuickPath Interconnect (uni-directional bandwidth of 19.2 GB/s) which is used to provide coherence in systems with lower memory bandwidths. [19]

Second, other architectures intentionally break with a support of cache coherence. The Intel Single-Chip Cloud Computer [20] provides no coherence at all and enables the research for many-core processors without that feature. Further, HPE's *The Machine* [21] or the *EUROSERVER* project [22] are designed to consist of multi-core processors but do not provide a globally coherent system. While those two systems are still based on shared-memory, they provide coherence only inside a subdomain, or island, consisting of multi-core processors. Thus, research of processor producers as well as designs of system builders consider the absence of coherence.

#### 1 Introduction

As a result of these two observations, non-cache-coherent architectures based on shared memory need to be considered. Programming models that use shared memory and do not require transparent hardware-based cache coherence have to be regarded as well. One-sided communication of the *Message Passing Interface (MPI)* is such a model and is therefore focused within this thesis.

#### 1.2 Outline

Chapter 2, provides background information which is required for the subsequent discussions. Cache coherence and its limitations are discussed. The chapter also presents the Intel *Single-Chip Cloud Computer (SCC)*, which is used as non-cache-coherent many-core platform, as well as a short overview on programming models for many-core processors. This also covers one-sided communication which is investigated within this thesis.

In Chapter 3, efficient synchronization for one-sided communication on the SCC is discussed. Therefore, an existing classification of synchronization schemes is extended. Implementations of the MPI general active target synchronization are then surveyed according to this extended categorization. The survey also discusses the suitability of the implementation for the SCC. Based on this analysis, a synchronization protocol is designed and evaluated on the many-core chip to confirm its effectiveness.

Afterwards, Chapter 4 addresses the communication on the SCC in absence of hard-ware-based coherence. The design of a software-based cache coherence protocol for MPI's one-sided communication that relies on shared memory is derived. The chapter presents fundamental requirements according to the MPI standard, discusses the efficient implementation on the SCC, and shows the results of the experimental evaluation. In addition, beneficial features for future architectures are proposed.

Finally, Chapter 5 summarizes and discusses the results presented in the previous chapters. With a look at future work, the thesis is concluded.

#### 1.3 Contributions

The main contributions of this thesis are the following:

- 1. The concept, implementation and evaluation of a synchronization protocol for one-sided communication on a non-cache-coherent many-core architecture is presented. The concept is based on shared memory, but does not require cache-coherence. In the evaluation it is demonstrated that the implementation of the proposed concept is efficient and provides much lower latency compared to a tuned message-based solution.

- 2. The SCOSCo approach, a software-managed cache coherence solution for one-sided communication on non-cache-coherent many-core processors, is designed. Requirements for such an implementation with respect to the MPI standard are identified. Based on these, a suitable implementation for the Intel SCC is derived and an evaluation is provided. Both micro-benchmarks as well as a stencil application and a communication-intense three-dimensional Fourier transform confirm the efficiency of that approach with up to five times reduced communication share on the overall runtime.

- 3. From both contributions above, consequences for the possible future CPUs are derived. Beneficial features are identified which should be included in future systems to support one-sided communication on shared-memory system where cache coherence is not available.

In addition to these major contributions, the following minor ones evolved

- 1. The existing classification of implementation options for the synchronization of one-sided communication is extended by a new class. (see Section 3.2). The additional class closes the gap between literature and implementations.

- 2. A survey on existing MPI libraries with a focus on general active target synchronization is carried out. The implementations are classified using the extended scheme. Based on its outcome, general concepts of such implementations are identified (cf. Section 3.3).

- 3. As a result of the survey, a conceptual error in the stable version of the well-known MPI library Open MPI is identified. The bug has been reported to the community and was confirmed as well. See Section 3.3.3 for details.

- 4. Multiple implementation errors in the original MPI library for the Intel SCC are identified that prevent the usage and evaluation of MPI one-sided communication with this library or any one-sided MPI application (see Section 4.1.2).

- 5. A (possible) bug of the SCC's hardware is identified. The hypothesis is supported by an involved Intel engineer (cf. Section 4.4.2).

#### 1.4 Publications

The majority of the above contributions has been reviewed and published in the following publications and was presented at the according conference workshops and symposia.

- Steffen Christgau and Bettina Schnor. "One-Sided Communication in RCK-MPI for the Single-Chip Cloud Computer". In: MARC Symposium. Ed. by Eric Noulard. ONERA, The French Aerospace Lab, 2012, pp. 19–23.

- Steffen Christgau and Bettina Schnor. "Software-managed Cache Coherence for fast One-Sided Communication". In: Proceedings of the 7th International Workshop on Programming Models and Applications for Multicores and Manycores, PMAM@PPoPP 2016, Barcelona, Spain, March 12-16, 2016. Ed. by Pavan Balaji and Kai-Cheung Leung. ACM, 2016, pp. 69–77. DOI: 10.1145/2883404.2883409.

- Steffen Christgau and Bettina Schnor. "Synchronization of One-Sided MPI Communication on a Non-Cache Coherent Many-Core System". In: ARCS 2016

29th International Conference on Architecture of Computing Systems, Workshop Proceedings, April 4-7, 2016, Nuremberg, Friedrich-Alexander University, Erlangen-Nürnberg. Ed. by Ana Lucia Varbanescu. VDE Verlag / IEEE Xplore, 2016.

- Steffen Christgau and Bettina Schnor. "Exploring One-Sided Communication and Synchronization on a non-Cache-Coherent Many-Core Architecture". In: Concurrency and Computation: Practice and Experience 29.15 (2017). DOI: 10. 1002/cpe.4113.

## 1.5 Scope

This thesis addresses the domain of high performance computing. As a consequence, general purpose parallel programming environments, like Thread Building Blocks, Cilk, Go Routines of the Go Language, etc. are not covered. Further, the context of this thesis are many-core processors. Although there is no commonly shared strong definition, it is assumed that many-core processors are high-end or research chips with a significantly higher number of cores than found in commodity consumer-level products. In addition, the thesis is restricted to chips with physically shared memory, and fully coherent chips or systems are generally not in its scope. Also, this thesis focuses on the design of software, especially middleware that relies on hardware features, but does not address the hardware implementation of processors.

#### 1.6 Conventions

In this thesis the following conventions are employed.

- 1. All physical quantities are considered to be a product of a number and a unit. That is, a quantity divided by its unit gives the quantity's value. As a result, expressions like "latency / \mus" are used in plots or tables to indicate that the following given numbers should be considered as \mus.

- 2. Units of quantities are expressed with SI prefixes which are based on powers of ten. However, when a quantity is based on the unit Bytes, the prefixes k, M, G, and T have to be considered as powers of two. That is, k = 1024,  $M = 1024^2$ , and so forth.

- 3. Bytes are abbreviated as B and the small letter b denotes the unit Bit, not Byte.

- 4. Names of authors are displayed with small caps, such as in HOARE.

- 5. Source code is typeset with a mono-spaced font, like printf. Routines from the MPI standard are generally written in upcase letters, like MPI\_BARRIER, matching the standard's convention. In listings of real or pseudo code, they are shown according to the appropriate language binding, like MPI\_Barrier when C is used.

## 2 Background

In this chapter, the architectural concepts of many-core processors are briefly introduced. Also, limitations concerning the memory subsystem with a focus on caches are covered. Those motivate to focus on non-cache-coherent systems, like the Single-Chip Cloud Computer. In the progress, different programming models and their suitability for non-cache-coherent many-core processors with shared memory are discussed, especially the one-sided communication model and its realization within the Message Passing Interface standard.

## 2.1 Shared Memory Processors

In the domain of high performance computing (HPC), multi-core systems with shared memory are essential building blocks of computer systems. They consist of multiple cores which are connected via some type of interconnect. For performance reasons, memory controllers are integrated into the processor in most cases. The design allows all cores to access the memory attached to the processor, i.e. the processor provides shared memory. As depicted in the introduction, caches are used to bridge the performance gap between the raw processor performance of the cores and the much slower main memory. Figure 1.2 illustrates an exemplary design with private and shared caches. Either type can be moved closer or farther away from the cores in other designs. VAJDA [24, pp. 9. ff] as well as RÜNGER AND RAUBER [25, p. 21] describe different design variants and the concepts in more details.

Techniques, like instruction pipelining, out-of-order execution, or superscalar designs, improved the raw performance of the individual processor cores. Nowadays, the majority processors are able to complete more than one memory operations per cycle. A core of a contemporary Intel Skylake processor can theoretically issue four memory operations per clock cycle. With a word size of 64 bits and a clock rate of 3.5 GHz (cf. Figure 1.1) this results in 112 GB/s of theoretical peak memory bandwidth per single core, not considering references to instructions. In a multi-core system with four

#### 2 Background

cores, this results in 448 GB/s of data traffic [14, p. 73]. Current DDR4-3200 memory with a frequency of 1.6 GHz delivers only 25.6 GB/s — barely enough bandwidth for a memory intensive application running on a single core.

Since a long time, however, caches exploit the fact that most memory references reoccur both in space and time. They buffer data which is likely to be reaccessed in a certain time frame as well as data that is close to the last referenced ones. The caches are faster than the main memory, but can only buffer a subset. Nevertheless, they provide the bandwidth that an application demands, as long as the principle of spatial and temporal locality is fulfilled by the application [14, p. 72 f.]. Thus, they are an essential component for contemporary processors. Efficient systems without caches seem to be hardly feasible. Details about cache design, replacement strategies, and optimizations can be found in HENNESSY AND PATTERSON [14].

In addition to single processors that house several cores, connections between those multi-core processors are possible. In general, each of the connected processor nodes provides memory to the system which is accessible to every core in the system. Since the access latency of memory in local and remote nodes differs, those designs are also denoted as *non-uniform memory access (NUMA)*. They also impose a challenge to the interconnect between the nodes because it has to sustain the bandwidth demands of the individual cores that potentially access remote memory. Note that also multi-core processors can be NUMA, depending on the actual design [25, p. 21].

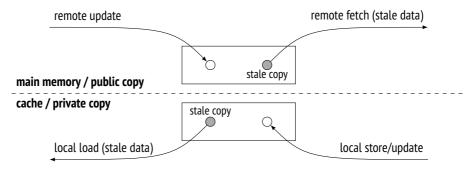

### 2.1.1 Memory Consistency and Coherence

Even in a single multi-core processor, the presence of multiple cores and their caches imposes two different but related problems.

#### **Memory Consistency**

When processes in a multi-core system exchange data via shared memory, i.e. they perform load and store operations, the question arises when the result of those events become visible to the running processes. The model that describes this property of the memory system is the *memory consistency model* or *memory model* [26, p. 229]. It can also be regarded as set of rules which specify the allowed behavior of programs running on the multi-core processors [27, p. 21]. If these rules are followed, the

memory system ensures that programs generate correct results according to the model. The rule set generally defines, in which order memory operations are allowed to be executed.

The problem of maintaining consistency is subject to many publications reaching back to at least LAMPORT's publication on correct program execution on multi-processor computers [28]. Within his model of sequential consistency, LAMPORT defines that the execution order of memory operations has to follow the instruction order in the program. That is, no reordering of the stated operations is allowed to happen. As a result, any sequentially executed interleaving of the (different) programs that maintains the original instruction orders represents an outcome of the parallel execution. [26, p. 231]

More relaxed models loosen the ordering rule of the sequential consistency model. They allow load or store operation to be reordered. The *total store order* model, e.g., allows independent load operation to execute before stores, but it maintains the order between writes [25, p. 95 f.]. To some extend, this model applies to contemporary Intel x86 processors [29].

The *release consistency (RC)* model [30] allows the reordering of all memory operations, but only within a pair of synchronization operations, named *acquire* and *release*. A processor has to complete an acquire operation before subsequent loads or stores are performed, but the order of independent accesses is unspecified. Completion of those accesses is enforced by the release operation. No reordering of acquire and release operations is allowed within this model.

For more details, GHARACHORLOO ET AL. [30] provide an overview of consistency models for shared memory multiprocessors that is extended by the survey of MOSBERGER [31].

#### **Cache Coherence**

The discussion of memory consistency ignores the presence of caches. This is valid, since from a programmers point of view they are transparent and, in fact, consistency is also an issue without caches. However, caches are critical components and need to be considered because they are used to implement the consistency [27, p. 21]. With multiple cores and their caches, the task arises to keep the caches up to date in order to avoid inconsistencies due to actions of other cores. This is the task of *cache coherence*. Coherence protocols are used to solve this problem.

#### 2 Background

Those protocols assign states to the cache lines. The lines represent the buffered subset of the main memory. The state describes the level of sharing inside the system. Coherence protocols define automata to describe the transitions between those sharing states. The set of the modified, exclusive, shared and invalid state is used by the probably most prominent protocol, *MESI*. Inputs to the automata are memory operations observed by the caches. Those are events from the local core as well as events issued by other ones. For example, an observed load on an exclusive cache line causes a transition into the shared state. Details of those protocols can be found in Chapter 7 in the book of SORIN, HILL, AND WOOD [27].

To observe operations by other cores, two different approaches are discussed in the literature: *snooping protocols* and *directory protocols*.

For snooping protocols, each cache maintains the state of a cache line. The cache observes, or snoops, memory operations by the local and other cores to change the cache line state according to the protocol [14, p. 354 ff.]. All memory actions issued by cores to their caches are broadcast to all other caches in the system. The observed operations serve as input to the protocol's automaton and cause according changes in the individual cache line states.

In directory protocols, the state is kept in a directory and not replicated in every cache of the system. Therefore, only the directory needs to be consulted when a memory operation is issued by the cores. The directory performs further steps like fetching the data from memory, requests data from other caches, collects the responses, resolves conflicts, and replies to the requesting cache. Thus, it relies on point-to-point messages with requests and replies rather than broadcasts.

The employed directory can be centralized. To avoid a bottleneck, it can be distributed as well. In that case, a (configurable) hash function can be used to identify the responsible directory based on the memory address [14, 32, 33]. In addition, the directory keeps track which caches contain copies of a memory block. Usually, a bit vector is employed to precisely track which caches own a copy. As a result the number of additional bits per cache line in the directory scales with the number of caches (or cores) within the system [14, p. 380].

A mix of the distributed and snooping protocol variants is also possible [14, p. 363 f.]. For example, for subdomains of the system a snooping protocol can be used. In case of a miss inside that subdomain, the directory protocol is employed to contact the directory and ask for the originally requested memory block. To find copies or invalidate cached data, the protocol may send requests, i.e. it snoops, on point-to-point links and waits for replies on order complete the operation [32, 34].

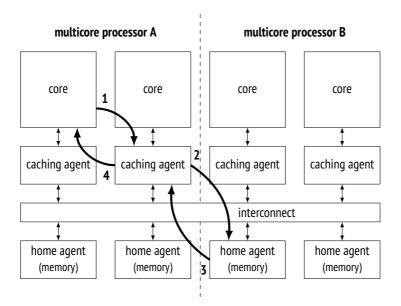

Figure 2.1: Messages sent in a QuickPath-connected system of multi-core processors.

Figure 2.1 illustrates the messages that are sent in a system of multiple multi-core processors with distributed shared memory and a mixed protocol, found in systems with Intel's QuickPath Interconnect technology [32, 34]. The diagram shows a message sequence that occurs in case of a local cache miss. In this case, a core sends a request to the cache controller (caching agent, CA) which is responsible for the requested memory address and is part of the last level cache in the local processor. From there, the responsible memory node (home agent, HA) that holds the directory is contacted if the cache controller could not satisfy the request from the last cache level. In the example, the memory node replies with data from memory, but it could also request data from other cache agents in case the address is shared.

#### 2.1.2 Limitations of Cache Coherence

Both snooping and directory protocols as well as mixed variants are used in multi-core and many-core processors.

Because snooping protocols require broadcasts, they often use a bus or a ring as interconnect since these are broadcast media and, therefore, well-suited for implementing those protocols [14, p. 356]. The bus' bandwidth needs to scale with the number of attached cores in order to provide them enough memory bandwidth. In fact, this is the limiting factor. As indicated above, a single core can easily require several GB/s of memory bandwidth. However, this exceeds the capacity of buses [14, p. 379], and such an approach will not scale for much more than eight cores [14, p. 363] or even connected multi-core processors, which has been demonstrated in experiments [16]. For that reason, such protocols are only used in systems with lower core counts or in systems with mixed protocols [25, p. 89, 32], where the last cache level of a multi-core processor is used as broadcast medium [25, p. 85].

In larger systems, like multi-core multiprocessor systems or many-cores, either mixed protocol variants or pure directory protocols are used [32, 35]. Since they rely on point-to-point messages only and do not employ broadcasts, the demands on the interconnect are lowered. Nevertheless, the increasing core count imposes new challenges to both the network performance as well as the storage capacity of the directories.

As pointed out above, a directory has to maintain a list of caches that possibly share a cache line. This implies a scaling problem because one bit per core has to be added to each cache block state. Thus, storage requirements for the directory are increased and can limit the use of directory protocols in the field of HPC when implemented in that straight-forward fashion [14, p. 379]. However, MARTIN, HILL, AND SORIN propose that the list of sharing caches can be stored in a hierarchical manner to solve this problem [36].

Besides those storage concerns, an increased core count still requires that the interconnect provides enough bandwidth to the cores [25, p. 31], even in presence of the coherence protocol messages. Compared to memory accesses in systems without coherence, the traffic per cache miss increases by about 20% [36] due to additional messages (cf. [32]).

In addition, the access latency to memory is increased. Instead of requesting memory directly, e.g. in case of a cache miss, the directory needs to be consulted. To provide coherence, this compromise has to be accepted, but its overhead might be small compared to high memory latency. In addition when the set of sharing caches is tracked precisely, the coherence traffic can be minimized and kept constant for up to 1024 cores [36].

Based on these observations, it is unlikely that cache coherence disappears completely, but its realization apparently becomes difficult. ASHBY ET AL. [37] state that according designs are "notoriously hard to verify". In addition, changes in technology may require design changes. Fast and large stacked on-chip memories provide much

higher memory bandwidths than conventional external memory: The integrated on-chip memory (MCDRAM) of the 72-core *Knights Landing* offers 450 GB/s, which is five times higher than the bandwidth of the chips conventional main memory. The processor uses a 2D mesh network, capable of handling 700 GB/s of traffic between the cores. It also provides cache coherence using a distributed tag directory [33].

Connecting multiple of these processors to build more powerful and coherent system is practically impossible. Coherent interconnects like QuickPath, with a maximum bi-directional bandwidth<sup>1</sup> of 38.4 GB/s [34] are not powerful enough to handle the coherence traffic even if a low share of coherence traffic is assumed [19, 33]. Even if one would connect the chips it might be done only in a *non-cache-coherent (nCC)* manner<sup>2</sup>, but this requires different programming schemes compared to multi-threading applications using shared memory.

Other systems drop the support for cache coherence by design, but still connect processors by means of shared memory. They provide coherence only within a subdomain of the whole system. The proposed *The Machine* focusses on memory-driven computing, i.e. to bring computation near the data by providing a huge pool of memory to the compute elements [38]. While the compute nodes are still cache-coherent multi-core processors, the whole system itself is nCC [21, 39] making it similar to a theoretical connection of Knights Landing processors.

A similar design is observed in the *EUROSERVER* project. Here two multi-core processors are connected with a coherent interface building a *chiplet* with attached memory. Multiple chiplets can be connected using a multilevel interconnect, but it does not provide a cache coherence protocol between the linked multiprocessor nodes. However, cached load and store operations to remote memory are possible. [22, 40]

In summary, "on-chip cache coherence is here to stay" according to the publication of MARTIN, HILL, AND SORIN [36]. Regarding the above examples, however, limitations of pure hardware-based coherence become visible and trends to intentionally avoid this hardware feature are coming up. Thus, the investigation of nCC systems with shared memory, especially many-cores, is critical. With the Single-Chip Cloud Computer such a system is investigated in the remainder of this thesis.

<sup>&</sup>lt;sup>1</sup>assuming an operating frequency of 4.8 GHz like on Haswell-EP platforms

<sup>&</sup>lt;sup>2</sup>personal conversation with Avinash Sodani, Knights Landing chief architect, on April 5 at ARCS conference 2016, Nürnberg

## 2.2 The Intel Single-Chip Cloud Computer

The Single-Chip Cloud Computer (SCC) is an experimental CPU architecture developed by Intel [20] within the Tera-Scale research program [41]. It can be regarded as a successor of the 80-core Teraflops Research Chip [42] which is also known as Polaris [43].

With the Polaris processor, the SCC shares a tiled architecture. All tiles are connected by an on-chip network. However, the SCC's tiles are not based on a specifically designed architecture, but on the well known x86 or IA-32 instruction set architecture. This can be considered as a consequence of the limited programming capabilities of the Polaris' cores which were programmed by hand-crafted VLIW assembly instructions, offered no I/O features and did not provide an operating system [44]. Thus programming the Polaris chip was limited to only a few researchers who were able to deal with these limitations.

The purpose of the SCC is to investigate scalable many-core processor design as well as further hard- and software-oriented research linked with this kind of architecture, such as energy management and parallel programming. A crucial aspect of the design was to drop coherence between the caches of the cores and support parallel applications with hardware message passing features. [20]

#### 2.2.1 Architectural Overview

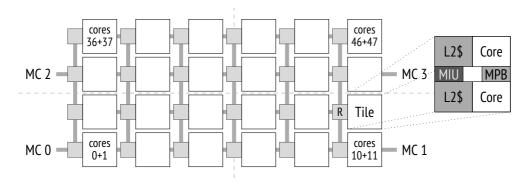

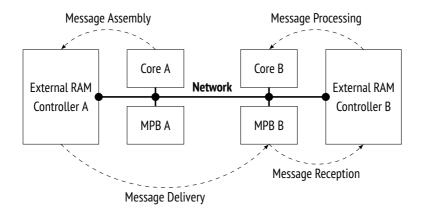

In contrast to its predecessor, the SCC consists not of 80 but of 24 tiles which are arranged in a 6 × 4 regular grid as shown in Figure 2.2. Each of those tiles contains five components: two cores with internal and external caches, a *Message Passing Buffer (MPB)*, a *Mesh Interface Unit (MIU)*, and a configuration register block located in the latter unit. A technical in-detail description of those parts can be found in [45]. Based on that specification, the following sections describe the essential aspects of these five components which are relevant for the presented work.

To connect the tiles with each other and the external memory, the SCC possesses an on-chip mesh network which is based on five-port routers. The local port of each router is connected to a tile, the other four build up the two-dimensional mesh. The network is packet-based and uses a static dimension-ordered routing [46, p. 8 f.]. That is, packets traverse in x-direction first and are routed along the y-direction to their target afterwards.

Figure 2.2: Overview of the tiled SCC architecture.

Further, the network attaches four DDR3 memory controllers to the chip. Six tiles with a maximum vertical distance of one and a maximum horizontal distance of two can be considered to belong to a memory controller domain (see Figure 2.2).

To access the chip, an external FPGA constitutes the system interface (SIF). An external computer is attached to the SIF-FPGA via PCI Express. This connection allows to inject and receive packets from the on-chip network. In addition, a voltage controller is integrated into the chip to enable dynamic frequency and voltage scaling. However, a discussion on energy-management is out of the scope of this work and further details are therefore omitted. Relevant research on this domain has been published in [47–49], among others.

#### Cores

The SCC cores are based on the 32-bit Pentium (P54C) architecture. Due the this legacy, the cores operate in-order. Instructions are executed in program order and are not dynamically reordered by the processor, e.g. to hide memory latencies as it is the case in contemporary architectures. In consequence, an SCC core stalls when a memory operation is issued but a preceding access is not yet completed.

Despite limited superscalar components in the Pentium design, the cores do not possess other features that enable parallelism at hardware level. There are neither vector units, multiple hardware threads, nor other instruction set extensions that can be found in contemporary processors. Thus, the SCC's performance is not comparable to such CPUs. However, this it not a critical aspect for the main purpose of the chip which is research.

#### 2.2.2 Memory Subsystem

For the work presented in this thesis, the memory subsystem is essential and is therefore discussed in detail within this section. The descriptions are based on [20] and [45], if not stated otherwise.

#### **Caches**

Two 16 KB L1 caches are integrated in each core, one for instructions and one for data. Their size is doubled compared to the original Pentium architecture. A line in those caches is 32 Byte large. The L1 cache can operate in write-through or write-back mode, i.e. when cached data is written the memory will be updated immediately or when the modified line is evicted, respectively.

In addition to the two integrated L1 caches, a second level cache is externally attached to each core and closely located on the tile (see Figure 2.2). Each L2 cache has a size of 256 KB and contains both data and instructions. It can operate in write-back configuration only. The line size is equal to the L1 cache. Both cache levels to not allocate lines when a write-miss occurs. In consequence, data is only cached on read accesses.

A key point of the SCC's architecture is the omitted cache coherence. There is neither hardware-assisted coherence between the two caches on a single tile nor between any caches of the overall chip. If the coherence property is desired, it has to be managed in software.

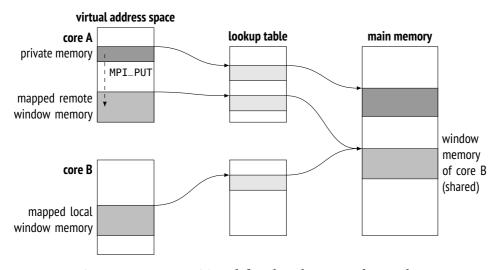

#### Mesh Interface Unit, lookup tables and Address Translation

The L1 and L2 caches are connected to a cache controller via a Front Side Bus interface. In case of a cache miss, the cache controller forwards the memory access to the *Mesh Interface Unit (MIU)*. This unit transforms the information from the cache controller into a network packet.

During the transformation of the memory access, an address translation takes place. Its input is the 32-bit physical address that was handed over to the MIU by the cache controller. The output of the translation is a 36-bit *system address* along with routing

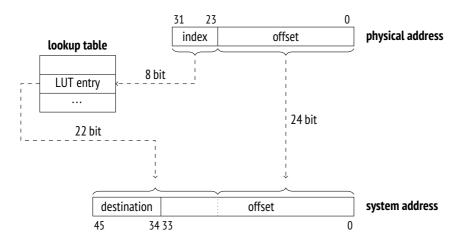

Figure 2.3: LUT-based translation of physical to system addresses by MIU.

information for the on-chip network. The translation is performed with the help of *lookup tables (LUTs)* as illustrated in Figure 2.3.

In the LUT-based translation procedure of the SCC, the upper eight bits from the physical address are used as index in a LUT. Each LUT entry is 22-bits large and contains network routing information such as the coordinates of the destination router/tile and the sub-target of the issued operation on that particular tile. The sub-target includes the four router ports as well as the tile's Message Passing Buffer and configuration registers that reside in the MIU. Since the DDR3 memory controllers are attached to router ports as well (e.g. on the west port of router at the lower left corner of the chip, see Figure 2.2), the external RAM is addressable too.

The location inside the given destination is specified by the 34 bits offset in the system address. It is constructed from 10 bits of LUT entry and the remaining 24 bits of the physical address. Regarding the physical addresses, the LUT mechanism consequently divides the addressable memory into  $2^{24} = 16 \, \text{MB}$  large pages which are identified by the data in an LUT entry.

The LUT-based address translation inside the MIU has several consequences:

1. The LUT mechanism provides access transparency. Independent of the addressed location, the required actions on software level are the same to perform a memory operation. This is even true on a machine instruction level as the translation happens outside the cores.

#### 2 Background

- 2. To address a specific location in the system from software, the physical address must be given. This is difficult when an operating system is used, which usually prevents direct access to a specific physical memory location when virtual address spaces are used.

- 3. The LUTs enable the definition of *shared memory*. If more than one LUT contains an entry with the same data, then different cores can access the same memory region. However, care has to be taken when accessing these shared memory areas due to the lack of hardware-based cache coherence.

The last consequence is further emphasized by the fact that a core's LUT resides in the configuration register block of the according tile. Accordingly, they are addressable by memory accesses and are writeable as well. The LUT configuration can be changed dynamically and memory can be easily turned into shared or private one at runtime.

The dynamic reconfiguration of the LUTs implies very little overhead since it just involves writing to the configuration registers. The written changes take effect immediately. However, effects of caching must be accounted carefully during reconfiguration since the caches operate with physical addresses. If a previously cached line is evicted after reconfiguration, it will be stored in the current destination configured by the LUT. It will not be stored in the position it was originally loaded from.

The concept of the address translation from a physical to a global (system) address is not special to the SCC. For example, the shared physical address space machine Cray T3D [50, p. 470 ff.] from 1993 used a similar scheme, where bits from the physical address are used as index for the reconfigurable *DTB annex* register set [51, p. 3-17 ff.]. Therein, the destination in the system for memory accesses is identified. Similar to the SCC, it is the software's responsibility that an access to a virtual address ends up at the right physical address and thus at the intended (remote) memory location.

Note that depending on the LUT configuration, the SCC can be classified differently. As long as no shared memory is defined, the cores operate independent of each other on isolated address spaces which makes the SCC a distributed system. That is why the SCC is also often referred to as an on-chip cluster. Contrarily, when shared memory is enabled by the LUT settings, the chip can be considered as a tightly coupled. Combining both aspects, the SCC can be considered as hybrid system [52].

#### 2.2.3 Message Passing Buffers

In addition to the cores and the caches, a 16 KB large SRAM memory, called *Message Passing Buffer (MPB)*, is placed on each tile and is connected to the MIU as well. In total, there are 384 KB of MPB memory available on the chip. A primary advantage is its lower latency compared to the external DRAM. An MPB access on a local tile only involves the MIU and the network<sup>3</sup>. It is three times slower than the L2 cache (18 core clock cycles) [46, p. 9]. Accessing remote MPBs adds further network hops. However, it does not involve overhead by the memory controllers. Thus, the on-die MPBs are still faster than the external memory. Additionally, due to the LUT mechanism, DDR and MPB accesses are transparent for software and can therefore be used in the same manner. Despite its name, the MPB can be used as general purpose memory. Thus it is sometimes refererred to as local memory buffer. Since, the term MPB is more common, it used in the remainder of this thesis.

#### 2.2.4 Memory Types

As depicted in Section 2.2.2, the physical address controls the destination of a memory access. This is because the physical address is used as input for the translation and LUT lookup, respectively. Anyhow, the physical address itself is the result of another translation process that converts a virtual address used by programs into a physical one. The page tables involved in this virtual-to-physical translation define the behavior of memory accesses in the system, i.e. the memory type.

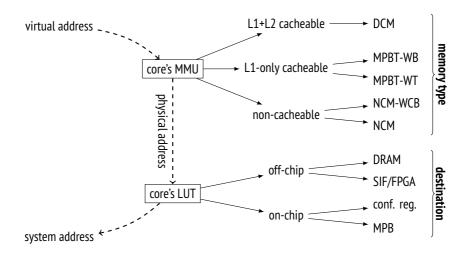

The memory type is defined by bits in the page table entries. Generally, the page table settings affect the cache behavior for the (usually) 4 kB large memory pages. It is important to understand, that the memory type setting is independent of the destination setting. Both settings are applied in different stages of the overall translation process that converts virtual addresses into SCC system addresses. This is illustrated Figure 2.4. The following sections describe which memory types can be configured by the page tables as well as their implications.

For the discussion, three bits of the page tables entries are relevant. The first one, named PCD, controls caching. If this bit is set, the memory inside that page is not cached. If it is unset, the usage of the second important bit, the PWT bit, is useful.

<sup>&</sup>lt;sup>3</sup>In principle, network accesses should not be required to access local MPBs, but a documented hardware bug prevents a network bypass which was originally intended by the designers.

Figure 2.4: Address translation mechanisms involved in memory accesses on the SCC.

This one controls the L1 cache mode. As it abbreviation indicates, a set PWT bit configures the L1 cache as write-through.

The third important bit was originally reserved in the Pentium page tables. For the purpose of the SCC's it was redefined and serves as utility for message passing. Its designation is PMB and it disables the L2 caches for pages having the PMB bit set in the page table entry. Thus, read accesses to such memory are cached only in the L1 cache. Further, the PMB bit enables a write combine buffer (WCB). This component can hold up to 32 write operations to subsequent bytes starting from an offset that is a multiple of 32. When another write operations is issued, the buffered writes are written to memory. The WCB is also flushed when it gets a write operations that does not fall in to the same 32 byte offset as the previously buffered accesses.

The combinations of those bits define different memory types which are discussed in the next paragraphs. Figure 2.4 gives an overview of the address translation processes, the discussed memory types and the possible destinations of memory accesses.

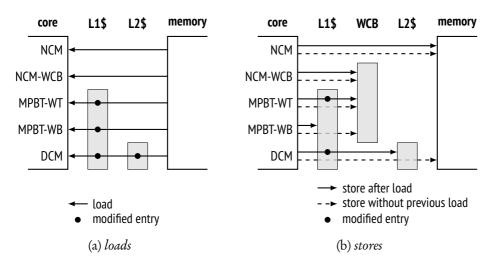

#### **Cacheable Memory**

When the page table entry's PCD bit is cleared, and the two other discussed bits are not set as well, all cache levels are activated. Consequently, a load operation fills cache lines in the L1 and L2 cache. Subsequent stores modify the cache lines and the modified

Figure 2.5: Semantics of load (a) and store (b) operations of the SCC's memory types.

data is written back only when a cache lines is replaced. This is the usual memory that is exposed by an operating system to user space processes. Since the caches are involved with this memory type, it is called *definitely cacheable memory (DCM)*.

Combinations of DCM with the other two bits are hardly useful. PWT will cause the L1 to be write-through but since the L2 cannot be configured is such, it keeps the write-back semantics. Thus, writes will hit the L2 if the writes are issued on already cached data. Using the PMB bit disables the L2 which contradicts the DCM semantics.

#### **Non-Cacheable Memory**

The contrary memory type to DCM is the *non-cacheable memory type (NCM)*. Here, the PCD bit is set which disables all caches, regardless of the other bits' setting. Thus, a read operation will always access the addresses memory, not the cache. Similar, writes go directly the memory, if the PMB bit is not set.

If the PMB bit is set, caches are still disabled, but the WCB is activated. Thus, writes can be buffered. This can be beneficial, if performance is an issue. Since an SCC core stalls when more than one memory access is in flight, it will observe long stalls when frequent accesses to NCM are performed which involve two traversals of the on-chip

#### 2 Background

network and latencies of the memory controllers. The WCB can be used to alleviate the time the core stalls. To differentiate the NCM with activated WCB from the plain NCM memory type, it is designated as NCM-WCB.

#### **Message Passing Buffer Memory Types**

The PMB bit in the page tables activates a memory type that is unique to the SCC. As stated above, when this bit is set and caching is not completely disabled (see previous section), but only the L1 cache is activated. When an L1 cache line is filled due load operations on such memory, the line is marked by setting an additional status bit. Thus, cache lines originated from pages with set PMB bit can be identified by the cache's circuitry.

This feature is exploited by the only SCC-specific extension to the instruction set of the Pentium cores, the CL1INVMB<sup>4</sup> instruction. The operation invalidates all lines with this bit and also clears the message buffer status bit on each line.

Due to the invalidation, cached and modified data is not written back but gets lost. A flush operation for these specially marked lines is not present in the instruction set. However, the privileged WBINV instruction writes back all L1 cache data and also invalidates all lines in the buffer.

The feature of fast invalidation of the marked cache lines is heavily connected with the MPB and supports fast on-chip message passing. Consequently, memory with the PMB bit set is referred to as *Message Passing Buffer type (MPBT)*. A MPB can be efficiently polled with this memory type for new data using a sequence of CL1INVMB and read operations from the MPB. To write data in the MPB it must be ensured that it is not stuck in the L1 cache due to previous reads from the MPB. In such a case, the CL1INVMB instruction has to precede write operations.

Since MPBT memory is cached only in the L1 cache, the memory type has to be distinguished in MPBT-WT and MPBT-WB, depending on the cache configuration that is controlled by the PWT bit. The WT variant has the general advantage that writes to cached data are also propagated to the targeted memory.

However, the MPBT memory activates the WCB. Consequently, writes to MPBT-WT memory modify the cache (if a cache-hit occurs) and are buffered by the WCB.

<sup>&</sup>lt;sup>4</sup> the mnemonic presumably stands for Cache Level 1 Invalidate Message Buffer lines

Hence, those operations materialize in the main memory only when the WCB is flushed. As illustrated in Figure 2.5b, the WCB can be thought as being placed behind the L1 cache. This also means, that writes to a cached line of MPBT-WB memory reach neither the WCB nor the addressed memory location as long as no flush of the written cache line is provoked. In absence of a cache flush based on addresses, there is no efficient way to achieve this goal.

## 2.2.5 Configuration and Atomic Registers

As depicted in Section 2.2.2, the MIU allows addressing of MPBs, memory, and configuration registers. This also includes the LUTs which are writeable as well and are part of the configuration register set. In addition, the core's hardware status information, thermal sensors, the tile frequency configuration, and the cache configuration are also available as memory mapped registers. The set also includes the tile ID register, which allows a tile's core to determine the tile's coordinates (x and y) and its own number z inside the tile (either 0 or 1). Thus, the global core ID can be computed.

Aside the mentioned registers, the MIU also provides a single atomic register per core that is denoted as *test-and-set register (TSR)*. Such a register can be used for synchronization purposes in software. On usual IA-32 processors, the legacy LOCK machine instructions prefix from the Pentium architecture is used in such cases. On bus-based architectures it locks the whole memory bus and prevented other participants (cores, e.g.) to perform memory operations. Thus, an atomic modification of a memory location is possible. In more recent architectures, the cache coherence protocol handles the LOCK prefix. Since cache coherence is missing on the SCC, the usage of the LOCK prefix is of no benefit. Even if uncached memory accesses are involved (see previous section), the implementation of a global memory lock operation seems to be challenging, not scalable, and prone to high latencies.

In contrast, the TSRs provide a minimalistic mean to implement synchronization. Initially, a value of one can be read from such a register. However, it atomically switches its value such that subsequent reads return zero. Hence, if a process reads a value of one it can be interpreted as having obtained the mutual exclusive lock. To release that lock, a write operation has to be issued to the register. The written value is ignored, but usually zero is used to indicate a release. After such a write operation, the register again returns the value of one for the very next read operation. To access the memory mapped TSRs in the MIU and obtain the described synchronization semantics, non-cached memory is the only option to do so. Cached operations would

# 2 Background

either prevent getting the most recent data from the TSR or would most likely be caught by the cache when attempting to release the lock.

When multiple processes running on different SCC cores need to synchronize by means of a single TSR the on-chip network is automatically involved. Since this is done by a memory access which itself underlies NUMA characteristics, unfairness occurs when cores on different tiles compete for the TSR [53]. This is especially the case, when the TSR is contented, like for spin-locks.

To work around the limited number of TSRs and their mutex-only semantics, the system's FPGA-based chipset has been extended and subsequently provide 96 *atomic increment registers (AIR)*. Those offer semaphore behavior and atomically increment on reads (and return the old value), respectively decrement on writes, and can be set up with associated initialization registers [54, p. 11 ff.]. However, compared to the TSRs, the latency of the AIRs is four times higher and unfairness is again inherited from the on-chip network. Further, contention needs to be considered as every AIR access is routed through the system interface [55].

#### 2.2.6 Software Environment

On top the described hardware features, different software packages are available for the SCC. Since the cores are based on the Pentium architecture, existing development toolchains, i.e. compilers, linkers, as well as low-level libraries can be reused. This enables compilation of most known software that supports the x86 architecture. Compatible software ranges from shells, basic command line utilities and scripting languages (Python, Perl) to database systems (MySQL) and web server software (Apache).

#### Linux for the SCC

To run those user-space applications an operating system is required. For this purpose, the Linux kernel was initially made SCC-compatible by Intel Labs as a customized version that was bundled along with user-land applications as *rckOS*. Subsequent work by SOBANIA, TRÖGER, AND POLZE improved the portability of the Linux kernel [56] which resulted in the creation of *sccLinux*<sup>5</sup>. Both versions have in common, that each core of the SCC runs a single instance of the operating system. This is mainly

<sup>&</sup>lt;sup>5</sup>https://github.com/hpi-scc/sccLinux, last accessed 2016-04-25

due to the nCC architecture of the SCC. Unless uncached memory is used, the Linux kernel must be made ware of the missing cache coherence, especially for shared kernel data structures. Although there are implementations of other operating systems [57], bare-metal application frameworks [58], and hypervisors [59, 60], which enable to run a single operating system instance (including Linux) on top of all SCC cores, this work focuses on the case of 48 individual instances.

#### **Default lookup table Configuration**

To support booting and running 48 individual Linux instances, the default LUT configuration is designed such that each core (and thereby each Linux instance) gets an equal amount of private memory. That is, only a single LUT has an entry that addresses a specific portion of the system's RAM.

In case of the SCC hardware available for this work, 32 GB of RAM are available. With a system page granularity of 16 MB (cf. Section 2.2.2), each core is assigned an amount of [32 GB/48/16 MB] × 16 MB = 672 MB RAM. This equals 42 entries in an LUT. Further, the LUT configuration ensures that the private memory of each core is located in the most closest memory controller. Consequently, each controller takes memory requests from 6 tiles or 12 cores respectively (cf. Figure 2.2 on page 17). The hardware setup ensures that all memory controllers are equipped with the same amount of RAM, i.e. 8 GB (8192 MB) per controller.

In addition to the private memory entries, the default LUT configuration includes entries to access all MPBs and configuration registers which are per-tile entities (see above) and thereby allocate  $2 \times 24 = 48$  LUT entries in total. Two additional entries are reserved for the voltage and frequency controller and the management interface. A summarized layout of the default LUT configuration is shown in Table 2.1.

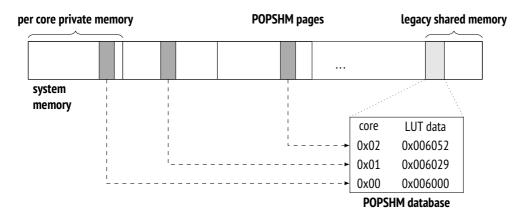

## **Legacy Shared Memory**

In this setup, 256-42-48-2=164 LUT entries are not used by private memory or other resources. In addition, the amount of private memory per memory controller  $(12 \times 672 \,\mathrm{MB} = 8064 \,\mathrm{MB})$  leaves 128 MB free for further usage. The default LUT configuration defines one entry (16 MB) per controller that uses this spare area. As the according entries are replicated for all cores, this portion of the system memory is shared and is denoted as *legacy shared memory (LSM)*.

| , ,        |         |                                   |

|------------|---------|-----------------------------------|

| Entry No.  | Entries | Purpose                           |

| 0 – 40     | 41      | private memory                    |

| 128 - 131  | 4       | legacy shared memory              |

| 191 – 215  | 24      | message passing buffers           |

| 224 - 247  | 24      | tile configuration registers      |

| 250 - 251  | 2       | voltage controller and management |

| 255        | 1       | private memory                    |

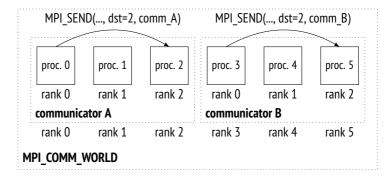

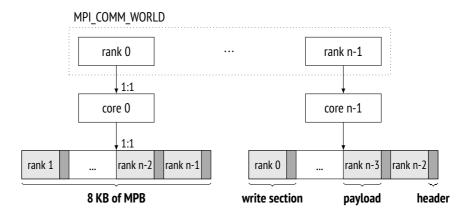

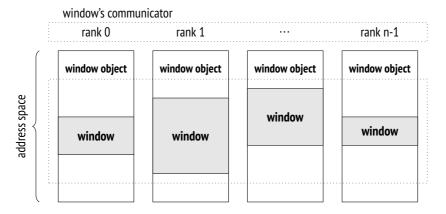

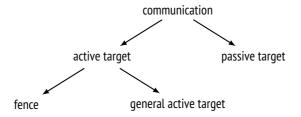

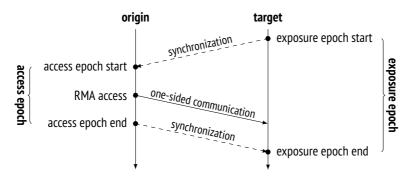

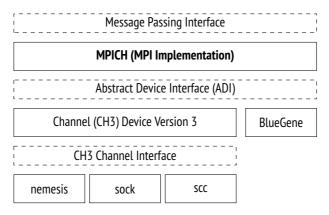

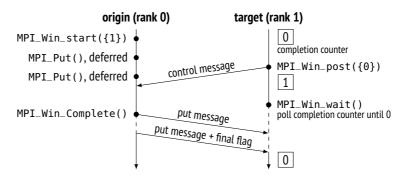

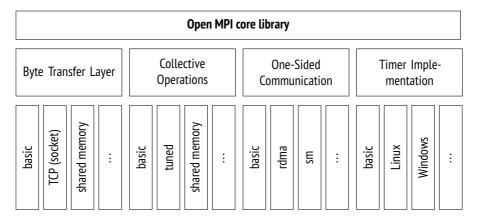

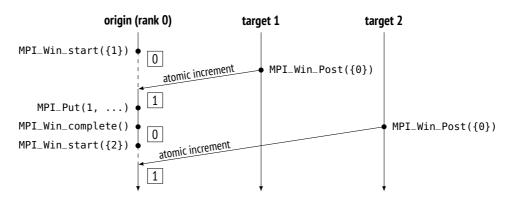

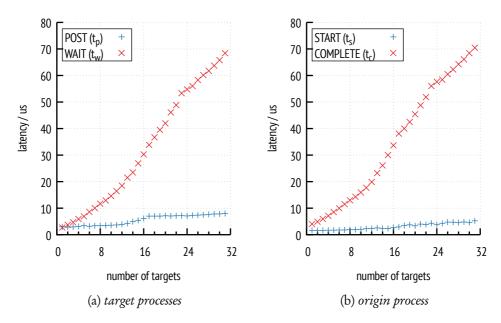

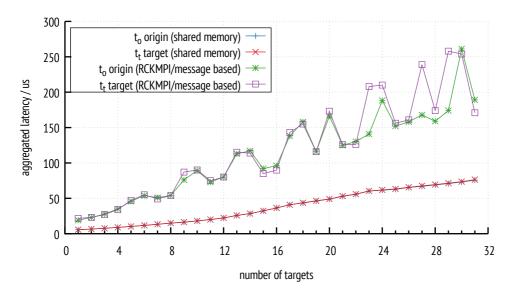

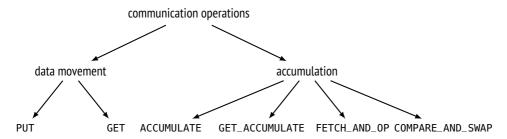

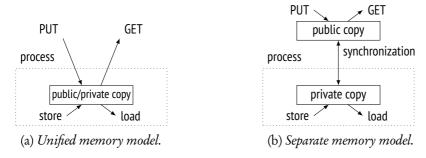

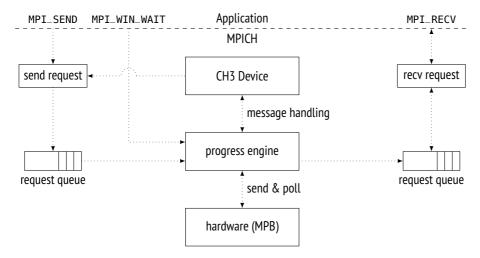

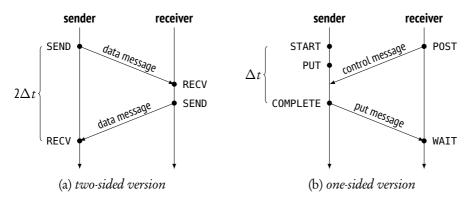

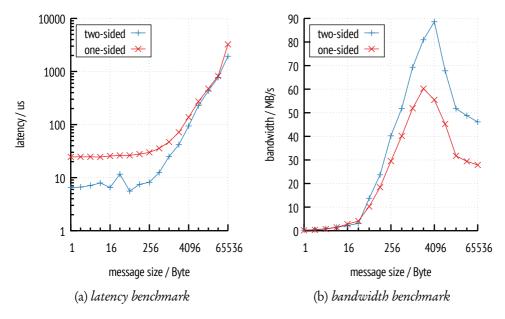

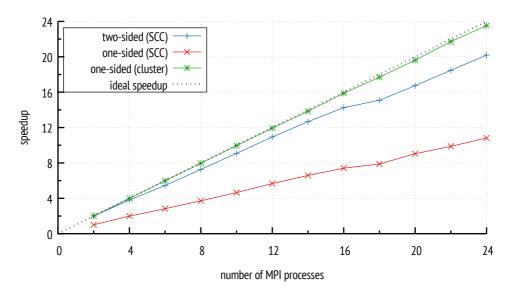

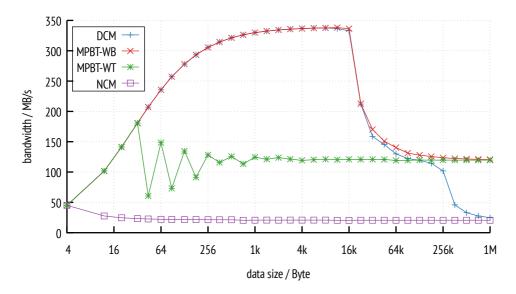

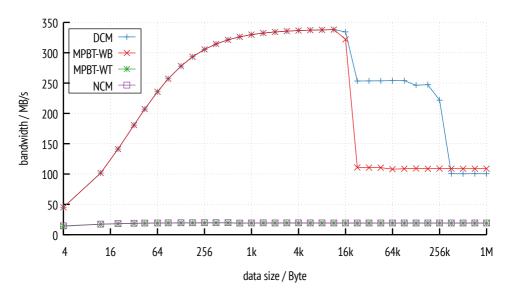

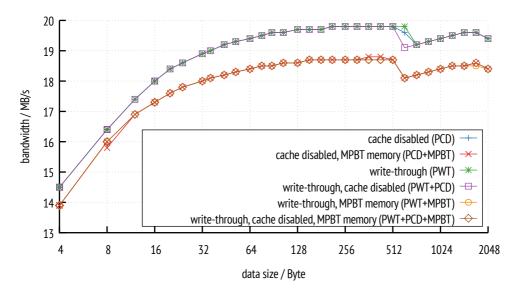

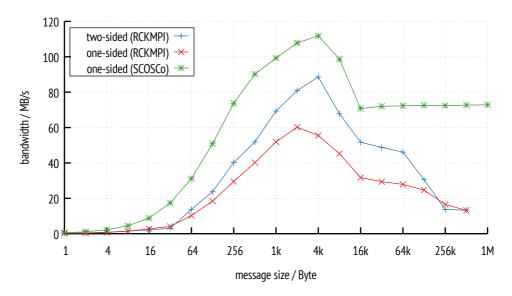

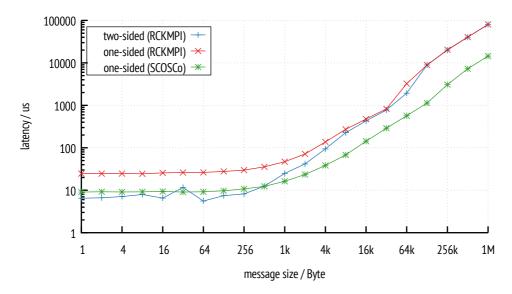

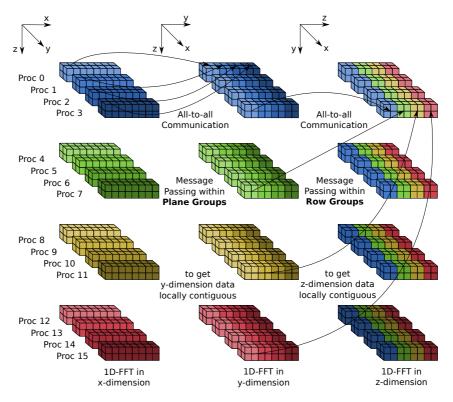

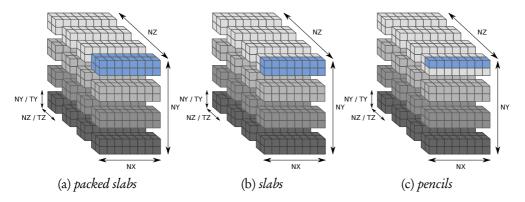

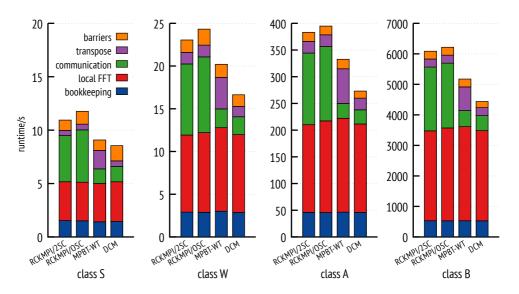

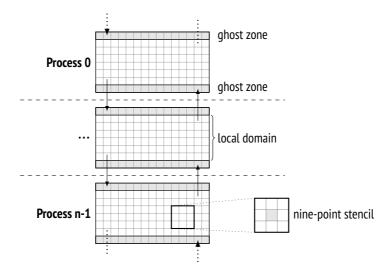

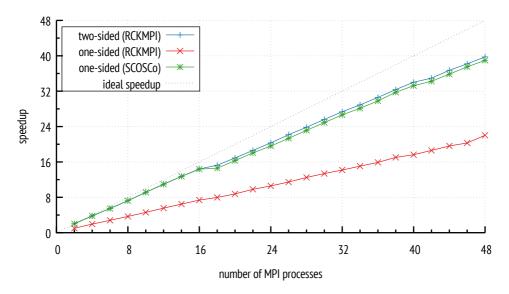

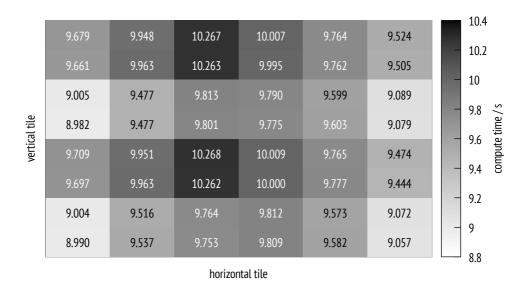

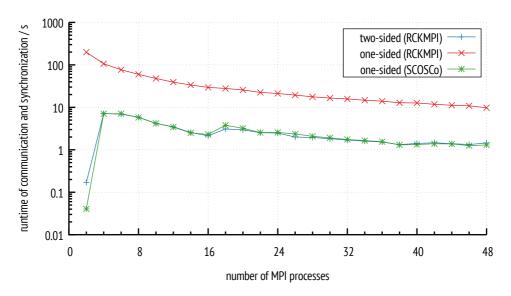

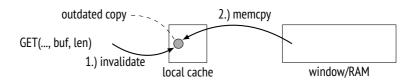

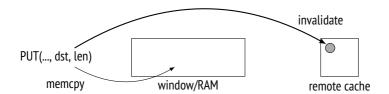

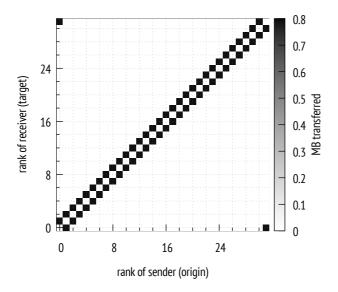

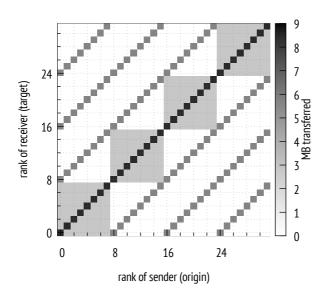

| all others | 160     | unused                            |