## Proceedings of the 4th Many-core Applications Research Community (MARC) Symposium

Peter Tröger, Andreas Polze (Eds.)

Technische Berichte Nr. 55

des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam

Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam | 55

Peter Tröger | Andreas Polze (Eds.)

Proceedings of the 4th Many-core Applications Research Community (MARC) Symposium

## Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.de/ abrufbar.

## Universitätsverlag Potsdam 2012

http://info.ub.uni-potsdam.de/verlag.htm

Am Neuen Palais 10, 14469 Potsdam Tel.: +49 (0)331 977 2533 / Fax: 2292 E-Mail: verlag@uni-potsdam.de

Die Schriftenreihe **Technische Berichte des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam** wird herausgegeben von den Professoren des Hasso-Plattner-Instituts für Softwaresystemtechnik an der Universität Potsdam.

ISSN (print) 1613-5652 ISSN (online) 2191-1665

Das Manuskript ist urheberrechtlich geschützt.

Online veröffentlicht auf dem Publikationsserver der Universität Potsdam URL http://pub.ub.uni-potsdam.de/volltexte/2012/5789/URN urn:nbn:de:kobv:517-opus-57898 http://nbn-resolving.de/urn:nbn:de:kobv:517-opus-57898

Zugleich gedruckt erschienen im Universitätsverlag Potsdam: ISBN 978-3-86956-169-1

## MESSAGE FROM THE PROGRAM CO-CHAIRS

In continuation of a successful series of events, the 4th symposium of the *Many-core Applications Research Community* (MARC) took place at the *Hasso Plattner Institute for Software Systems Engineering (HPI)* in Potsdam. On December 8th and 9th 2011, researchers from different fields presented their current and future work on many-core hardware architectures, their programming models, and the resulting research questions for the upcoming generation of heterogeneous parallel systems.

While the Intel Single Chip Cloud Computer (SCC) serves as common research platform for most MARC members, other interesting research on next generation many-core platforms was also discussed on this event. The symposium focused on topics such as

- · Operating system support for novel many-core architectures

- Virtualization solutions to deal with hardware limitations

- Dealing with legacy software on novel many-core architectures

- · New approaches for leveraging on-die messaging facilities

- Traditional and new programming models for novel many-core hardware

- Concepts for runtime systems on novel many-core hardware

- · Performance issues with modern on-die messaging facilities and caching infrastructures

This proceedings include 14 papers from 5 symposium sessions. Every paper was reviewed by at least three reviewers from the program committee, consisting of:

- Dr. Ulrich Bretthauer (Intel)

- Jaewoong Chung (Intel)

- Saurabh Dighe (Intel)

- Prof. Dr. Michael Gerndt (TU München)

- Diana Göhringer (Fraunhofer IOSB)

- Matthias Gries (Intel)

- Werner Haas (Intel)

- Prof. Dr. Hans-Ulrich Heiß (TU Berlin)

- Jim P. Held (Intel)

- Prof. Dr. Robert Hirschfeld HPI)

- Ulrich Hoffmann (Intel)

- Jason M. Howard (Intel)

- Dr. Michael Hübner (Karlsruhe Institute of Technology)

- Timothy M. Mattson (Intel)

- Georg Müller (Fujitsu)

- Prof. Dr. Jörg Nolte (BTU Cottbus)

- Prof. Dr. Andreas Polze (HPI)

- Dr. Felix Salfner (SAP Innovation Center)

- Prof. Dr. Bettina Schnor (Uni Potsdam)

- Prof. Dr. Theo Ungerer (Universität Augsburg)

- Dr. Peter Tröger (HPI)

- Dr. Daniel Versick (University of Rostock)

- Rob F. Van Der Wijngaart (Intel)

We would like to thank our program committee members for their hard work and for their suggestions in the selection of papers. We would like to thank all those who submitted papers for their efforts and for the quality of their submissions. We also would like to thank Jan-Arne Sobania and Sabine Wagner for their assistance and support.

Thank you for your active participation in the 4th MARC Symposium. We hope you found this event to be productive and enjoyable, and we look forward to seeing you next year at 5th MARC symposium and related events.

Peter Tröger & Andreas Polze, Hasso Plattner Institute, University of Potsdam, Germany Potsdam, January 2012

## CONTENTS

| I Isaias A. Compres and Michael Gerndt.                                                              |    |

|------------------------------------------------------------------------------------------------------|----|

| Improved RCKMPI's SCCMPB Channel: Scaling and Dynamic Processes Support                              | 1  |

| II Stefan Lankes, Pablo Reble, Carsten Clauss and Oliver Sinnen                                      |    |

| The Path to MetalSVM: Shared Virtual Memory for the SCC                                              | 7  |

| III Vincent Vidal, Simon Vernhes, and Guillaume Infantes                                             |    |

| Parallel AI Planning on the SCC                                                                      | 15 |

| IV Bertrand Putigny, Brice Goglin, and Denis Barthou                                                 |    |

| Performance modeling for power consumption reduction on SCC                                          | 21 |

| V John-Nicholas Furst and Ayse K. Coskun                                                             |    |

| Performance and Power Analysis of RCCE Message Passing on the Intel Single-Chip Cloud Computer       | 27 |

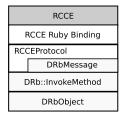

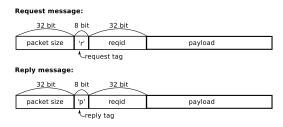

| VI Kouhei Ueno and Koichi Sasada                                                                     |    |

| Ruby on SCC: Casually Programming SCC with Ruby                                                      | 33 |

| VII Tommaso Cucinotta and Vivek Subramanian                                                          |    |

| Characterization and analysis of pipelined applications on the Intel SCC                             | 37 |

| VIII Bruno d'Ausbourg, Marc Boyer, Eric Noulard, and Claire Pagetti                                  |    |

| Deterministic Execution on Many-Core Platforms: application to the SCC                               | 43 |

| IX Paul Cockshott and Alexandros Koliousis                                                           |    |

| The SCC and the SICSA Multi-core Challenge                                                           | 49 |

| X Roy Bakker and Michiel W. van Tol                                                                  |    |

| Experiences in porting the SVP concurrency model to the 48-core Intel SCC using dedicated copy cores | 55 |

| XI Björn Saballus, Stephan-Alexander Posselt, and Thomas Fuhrmann                                    |    |

| Caching Strategies and Access Path Optimizations for a Distributed Runtime System in SCC Clusters    | 61 |

| XII Thomas Prescher, Randolf Rotta, and Jörg Nolte                                                   |    |

| Flexible Sharing and Replication Mechanisms for Hybrid Memory Architectures                          | 67 |

| XIII Jan-Arne Sobania, Peter Tröger, and Andreas Polze                                               |    |

| Towards Symmetric Multi-Processing Support for Operating Systems on the SCC                          | 73 |

| XIV Markus Partheymüller, Julian Stecklina, and Björn Döbel                                          |    |

| Fiasco.OC on the SCC                                                                                 | 79 |

# Improved RCKMPI's SCCMPB Channel: Scaling and Dynamic Processes Support

Isaías A. Comprés Ureña and Michael Gerndt

Technical University of Munich (TUM), Institute of Informatics,

Boltzmannstr. 3, 85748 Garching, Germany

{compresu,gerndt}@in.tum.de

Abstract—The Single-chip Cloud Computer (SCC), a 48 core experimental processor from Intel labs, is a platform for parallel programming research. Its hardware features and memory organization map naturally to message passing models. Standard and non-standard message passing libraries are already available for the SCC; one of the standard solutions is the RCKMPI library. RCKMPI's main features are three SCC specific MPICH2 channels. In this work, improvements to the SCCMPB channel are introduced; performance results for the new channel show better scaling with process count. The added flexibility of the new design also allows for the support of dynamic processes, a feature previously not supported in RCKMPI.

Index Terms—MPI, dynamic processes, communication protocol

## I. INTRODUCTION AND RELATED WORK

The Single-chip Cloud Computer (SCC)[2] from Intel Labs is an attractive platform for parallel programming research. Having a distributed memory organization, the message passing model maps naturally to it. The Message Passing Interface (MPI) is a dominant standard for message passing; it is widely used in super computers and has been shown to scale to hundreds of thousands of cores. A large number of parallel applications that use MPI are available; these applications can be compiled and run in systems that have a compatible MPI library. Support for MPI on the SCC was possible since early in the chip's life, through the use of a network driver[11] and MPI libraries configured to use sockets. The downside of using the driver was that communication performance was much lower than the lightweight but non-standard solutions. In order to reach acceptable performance with message passing on the SCC, applications needed to be ported to its libraries, like RCCE[3] or its non-blocking improvement (iRCCE[4] from RTWH Aachen). In addition to RCCE, other projects have implemented their own message passing based communication protocols, like the TACO[9] and X10[10] ports to the SCC.

Compatibility with MPI with no significant compromise in performance is desirable in new parallel architectures, given the large amount of software and tools available for it. There are currently two MPI projects for the SCC: the RCKMPI[5] and the SCC-MPICH[8] libraries. With the introduction of RCKMPI, MPI applications reached performance that was comparable to that of the non-standard lightweight solutions on the SCC. RCKMPI's main contribution was the introduction of three SCC specific MPICH2[7] channels. Being a first

attempt at efficient MPI on the SCC, it is natural to expect that there is potential for performance improvements in the channels; one such improvement was presented by Christgau et al. in [1], by the addition of topology-awareness to the library. In this paper, an improved communication protocol is presented for the SCCMPB channel of RCKMPI; the new design shows improvements in scaling with process count and supports dynamic processes from MPI-2.

## II. IMPROVED SCCMPB CHANNEL

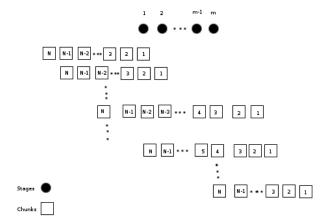

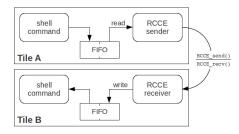

RCKMPI introduced three SCC channels: SCCMPB, SCC-SHM and SCCMULTI. The SCCMPB channel uses only the Message Passing Buffer (MPB) for communication; in this work, this channel is improved.

At initialization for the SCCMPB protocol, each MPB of a participating process was partitioned in sections of equal size. The main disadvantage of this design is that the size of each EWS becomes smaller as the size of an MPI job increases; in the 48 process case, the EWS size is 160 bytes (with 12 bytes used for protocol metadata). The size of the EWS influences channel performance, since with smaller buffers the communication protocol requires more round trips to complete the transmission of a packet. The second disadvantage is that, because these are initialized at job startup and remain static until job termination, MPI-2 dynamic processes can not be supported. Finally, it was not possible to share the MPB with other subsystems or use it directly for optimized collectives. The new channel design addresses all of these shortcomings.

The new SCCMPB channel is partitioned differently and works with two different protocols. The first protocol is the original one found in RCKMPI and is labeled as the base protocol. The second protocol is labeled as the extended protocol, and it depends on the base protocol for coordination.

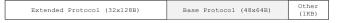

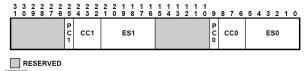

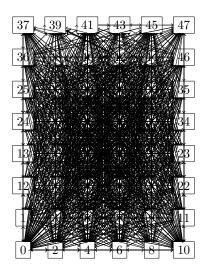

Fig. 1. MPB areas used by the base and extended protocols.

## A. Base Protocol

Similarly to the channels in RCKMPI, the base protocol consists of statically allocated Exclusive Write Sections (EWSs) placed at the receiver and a polling based strategy for new message detection. In contrast to the original, the size of these EWSs is not modified depending of the number of participating processes. They are always 48 and fixed at 64 bytes in size, for a total of 3KBs at each core's MPB. The 64 bytes in the static EWS setup allows for 48 bytes of payload. The remaining 16 bytes are used by the channel for metadata. The size of 64 bytes was selected based on the following observations:

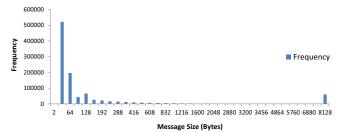

- MPICH2 packet headers are 32 bytes.

- Latency sensitive operations (like barriers) benefit from dedicated buffers.

- Packets smaller than 48 bytes occur with high frequency at the channel.

The last was first observed empirically by using RCKMPI's channel statistics feature. Inspecting the MPICH2 device layer reveals that preamble steps involving barriers and other collective operations are common, when operating with larger buffers; these preamble operations result in small point to point traffic that is typically smaller than 16 bytes in payload. A packet with 16 bytes of payload result in 48 bytes total at the channel (32 header bytes plus 16 payload bytes).

The 16 bytes of metadata contain the following:

- Checksum: A checksum to improve consistency in case of a hardware error.

- General purpose EWS control: Used to control access to the general purpose EWS (gEWS) used by the extended protocol (described in detail in II-B).

- Message size: Bytes of payload currently available in the EWS. This size can exceed 48 bytes if part of the payload is located at the gEWS.

- Packet size: This is the total size of the MPICH2 packet in transit. This value is independent of the actual payload available in the EWS.

- Receive sequence: This value is used to indicate that a message was received at the remote core that owns the EWS.

- **Send sequence:** Sequence number of the message that is currently in the payload area of the EWS.

The progress engine polls this metadata when receiving messages. It determines if to use the base protocol together with the extended protocol, based on the gEWS control data.

## B. Extended Protocol

The extended protocol uses a 4KB EWS that is labeled as the general purpose EWS (gEWS) internally. This buffer differs from the original EWSs in that it is placed at the sender and can be used to send messages to several receivers simultaneously. The gEWS can also be locked for its use in other operations, like spawn operations or optimized collectives. The size of 4KB was selected because it is the page size for the P54C architecture and it can be controlled with a single 32 bit field.

Together with the previously available metadata, a gEWS control field (32 bits) is specified by the sender. Each bit represents 128 bytes of the gEWS. All zeros indicate that the

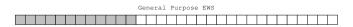

Fig. 2. Example gEWS state for 1536 bytes (bit field set to 0xFFF00000).

gEWS was not used for a particular message, while all ones indicates that the full 4KBs were used. When a new message is detected at the receiver, it reads the specified number of bytes starting from the payload area of the base protocol and then (if available) from the specified gEWS 128 byte slots.

Fig. 3. Ring buffers on a fragmented general purpose EWS.

The extended protocol design can be used to serialize messages by writing payload to the gEWS in 128 byte chunks and then updating the relevant bits in the gEWS control entry. The gEWS can also be treated as one or multiple ring buffers; one ring buffer can be constructed per each remote core with the use of the bit field. In case of fragmentation, the bit field is used to specify which chunks are used to build a ring buffer (as shown in figure 3).

## C. Protocol Characterization

To see why the addition of the extended protocol results in improved channel performance, an understanding of the original channel's behavior is necessary. When transmitting an MPICH2 packet, the total round trip time is the aggregation of the time required by several simpler operations. These times can be approximated with the following equation:

$$T_x(B,b,n) = \left[t_{sp}(n) + t_w + t_{rp}(n) + t_r + p_h t_h\right] \left\lceil \frac{B}{b} \right\rceil \tag{1}$$

where B is the size of the MPICH2 packet to send, b is the size of the EWS (in bytes) and n is the number of processes of the MPI job. The terms in the left factor represent the time required for writing, reading, polling and handling. The sender needs to poll the receive flag for the target process; this time is represented by  $t_{sp}$ . After the target EWS is available for writing, the bytes are written in  $t_w$  seconds. At the receiver, the progress engine polls the metadata to detect new messages;  $t_{rp}$  seconds are spent in doing this and then  $t_r$  seconds of CPU time are used reading the available payload. Polling times depend on the number of processes n. If the MPICH2 packet is complete with the last read payload, then  $t_h$  seconds are spent handling it; handling of a packet occurs with an application dependent probability of  $p_h$ .

These operations are done for each round trip of the communication protocol. The number of round trips required is the ceiling of the size of the packet divided by the size of the EWS (the  $\left\lceil \frac{B}{b} \right\rceil$  factor in formula 1). The time required to write at the sender and to read at the receiver are the same:  $t_r = t_w = t_{rw}$ . These are *memcpy* operations and their aggregated time  $t_{arw}$  depends on the total number of bytes to transfer, independently of the number of round trips. The time required for polling at the sender and receiver can be represented by a single variable for their combined worst case as  $t_{wcp}$ . Furthermore, packet handling is done with a much lower frequency; packets are only handled when they are done after several protocol round trips and can be ignored. With these observations, 1 can be simplified as:

$$T_x(B, b, n) = 2t_{arw}(B) + t_{wcp}(n) \left\lceil \frac{B}{b} \right\rceil$$

(2)

Conclusions can more easily be drawn from 2. The  $2t_{arw}$  term is a function of the total bytes B of the packet. The polling overhead  $t_{wcp}$  depends on the process count and increases linearly with it, since metadata is polled in a round robin fashion. The number of round trips  $\lceil \frac{B}{b} \rceil$  depends on the process count as well, since the size of b is determined at initialization based on the MPI job size.

The new design can be modeled similarly to the original one. The effect of the gEWS in the protocol, is that depending of the probability of it being free, the round trips required to transfer a packet are greatly reduced:

$$T_x(B,n) = 2t_{arw}(B) + t_{wcp}(n) \left[ p \left[ \frac{B}{b_{4KB}} \right] + [1-p] \left[ \frac{B}{b_{48B}} \right] \right]$$

(3)

where p is the probability of the gEWS being free and is application dependent. The number of round trips now depends on the application alone (given that the EWS and gEWS are now fixed with size  $b_{4KB}$  and  $b_{48B}$ ), and not on the number of processes. The worst case polling time still depends on process count, and is therefore not improved with respect to the original protocol.

From 3 it is easy to see that  $p \approx 1$  is desirable. Because of the way MPICH2 collectives (with a logical ring topology and other schemes) and most MPI applications (that send messages to only a few processes at the same time) are implemented, this is very often the case. Communication between a pair or processes is never stopped if the gEWS is not available, performance is just degraded by the limitation of 48 bytes of payload per round trip of the static EWS.

## III. SUPPORT FOR MPI-2 DYNAMIC PROCESSES

The dynamic processes functionality of MPI-2 is not used with the same frequency as point to point, collectives or one sided communication on current MPI applications. For this reason, their exclusion was found to be acceptable in the first release of RCKMPI. The spawn, connect and disconnect operations are necessary to support dynamic processes. Connect and accept are implemented at the channel, while spawn involves the interaction of the process manager and several parts of the library.

Fig. 4. Flow diagram of the accept algorithm.

For the addition of connect and accept to the channel, the gEWS was used. Since it is a shared resource, in this case used by the point-to-point communication subsystem, there are necessary steps before it can be used. The owner of the gEWS is the local core; therefore, its global state is stored in a local 32 bit field. If the gEWS is in use, the channel calls the progress routines until the send queues are cleared; after that, the gEWS is free to be used for any other purpose.

The spawn operation involves two process groups: the parent group and the child group. At each of these groups, one of the processes is the root process. The algorithm used is similar to the default one found in MPICH2, but latency optimized by the use of the gEWS directly, instead of relying on the non blocking point to point functionality provided by the channel implementation.

The parent group does an accept operation while the child group does a connect operation (flow charts shown in figures 4 and 5). The root process of each group writes the core IDs and other data required to build a process group structure, on its own gEWS. Then, they contact each other, exchange minimal but essential data: core ID where each is running, process group ID and size of each remote process group. After this, each root process shares this information with its peers, which read the rest of the process group data directly from the gEWS

Fig. 5. Flow diagram of the connect algorithm.

of the remote root process.

Before this operation is possible, the process manager passes the business card of the root parent to the root process at the newly spawned child process group. The root process of the parent group then waits for the child root to initialize the communication, and this is where the connect and accept operations start. The new process group generated by these pair of operations, is added to the process group list of each process. These groups are disjoint and can be reached through an inter-communicator, as specified in the standard.

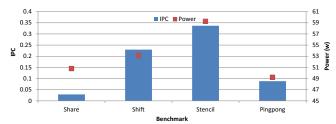

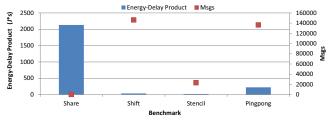

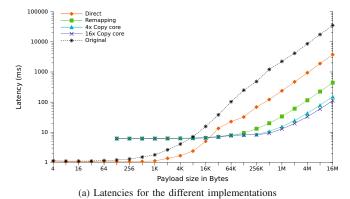

## IV. PERFORMANCE EVALUATION

In this section, the original and new SCCMPB channels' performance is evaluated with the use of the SKaMPI 5.0 benchmark suite and the NAS 3.3 LU and BT benchmarks. The software, hardware and configuration are the same for all tests in this section. The Rocky Lake SCC systems used for testing were configured with maximum frequency settings: 800MHz for the cores, 1600Mhz for the tiles and routers and 1066Mhz for the DDR3 memory. A Linux 2.6.38 image was loaded in all cores. The GCC compilers version 4.5 we used to compile the kernel, libraries and applications. Both C and Fortran MPI applications were compiled with the -O3 flag.

Fig. 7. MPI\_Gather scaling with buffer size.

Fig. 8. MPI\_Scatter scaling with buffer size.

## A. SKaMPI 5

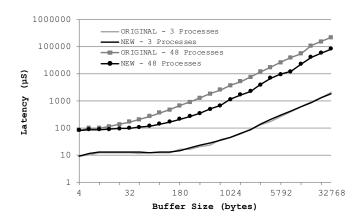

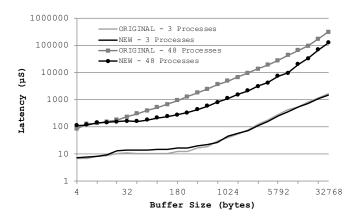

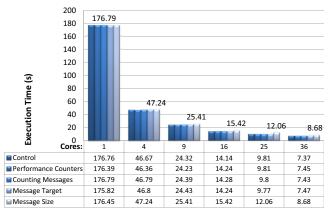

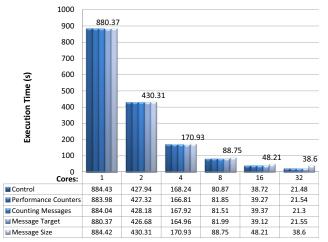

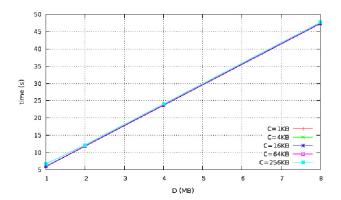

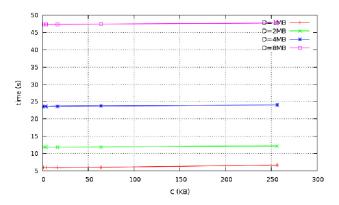

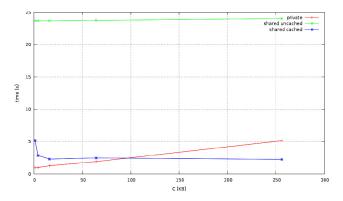

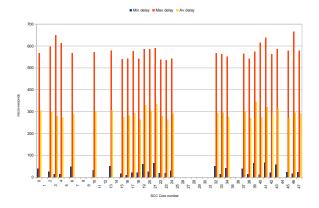

SKaMPI[12] is a benchmark suite that covers most of the MPI-2 API. Results for point to point and collective communication are presented here. Figure 6 shows point to point latency scaling with *MPI\_Sendrecv* (round trip times) for different message sizes. When running with 48 processes, the new channel scales better than the original for buffers greater than 128 bytes; at 16KB messages, their point to point performance differs by a factor of 6.25.

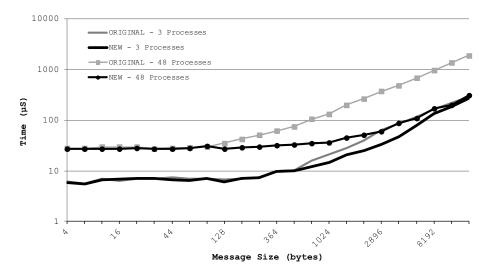

MPI\_Gather scaling for different buffer sizes is presented in figure 7. In the 48 process case and for 16KB buffers, their latency differs by a factor of 2.6. Scaling results for MPI\_Scatter are shown in figure 8. For the 48 process case, the new channel outperforms the original by a factor of up to 4.6.

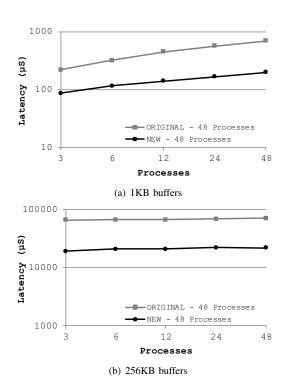

MPI\_Bcast scaling results, for 1KB and 256KB buffers, are presented in figure 9. In the 1KB buffer case, scaling is similar in both channels (as shown in 9(a)); however, absolute performance is much better in the new channel. For 1KB buffers, the latency differs by a factor of 3.5 in the 48 process case. For 256KB buffers, the difference in latency does not change much with process count (as presented in 9(b)). The latency of the old and new channels differ by a factor of 3.2, in this case.

Fig. 6. MPI\_Sendrecv scaling with message size.

Fig. 9. MPI\_Bcast scaling with process count for 1K and 256K buffers.

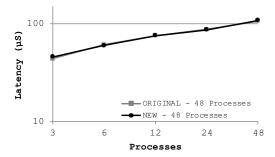

Scaling results for *MPI\_Barrier* are presented in figure 10. The latencies for this operation are very similar for both channels. This is expected since for small payloads (16 bytes and below) the same communication protocol is used by both channels.

## B. NAS Benchmarks

The NAS parallel benchmarks[13] are useful for evaluating parallel computers. The algorithms used by it are found very

Fig. 10. MPI\_Barrier scaling.

often in scientific applications. Results for the BT and LU benchmarks, at sizes W and A, are presented in this section.

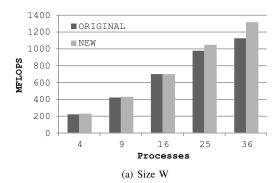

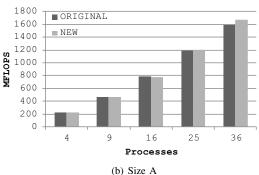

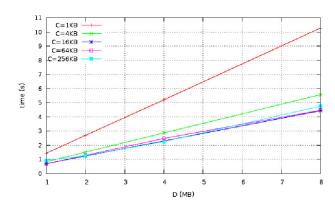

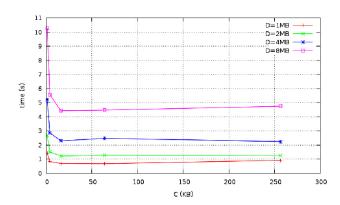

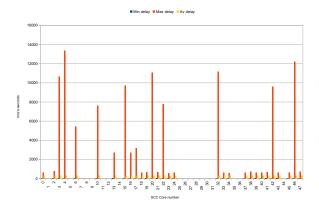

Both channels perform nearly the same when running the BT benchmarks (shown in figure 11) with 4 to 16 processes. For the BT benchmark, the new channel shows a performance improvement over the original one when running with 25 and 36 processes (as shown in 11(a) and 11(b)). The improvement is higher for the W size of the benchmark.

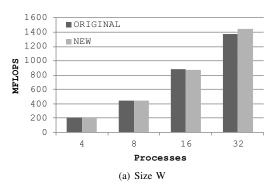

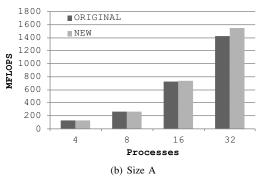

Results from the LU benchmark (figure 12) are very similar to those in the BT one. Performance when running with 4 to 16 processes is nearly the same with both channels. When running with 32 processes, the new channel shows better results (as presented in 12(a) and 12(b)).

## V. CONCLUSION AND FUTURE WORK

An improved design for the SCCMPB channel of RCKMPI was presented. The design consists of a base and an extended protocol that compliment each other. In contrast to the original design, the use of these new protocols resulted in channel bandwidth that is less dependent of process count; this was a consequence of the use of large EWS placed at the sender, that is shared for communication with several processes si-

Fig. 11. NAS BT scaling with process count.

Fig. 12. NAS LU scaling with process count.

multaneously and reduces the number of round trips required to complete a transfer.

Performance results from the SKaMPI and NAS parallel benchmarks were presented. The new design of the SCCMPB channel clearly outperformed the original one when running MPI jobs that use the 48 cores of the SCC; the advantage could be better observed in the SKaMPI point-to-point and collective tests. Good results were also observed for the NPB benchmarks for process counts larger than 25; the improvements in these benchmarks are not as large, since they have high computation areas and the improved channel performance only affects MPI communication times.

The way the MPB is partitioned was also modified. The new scheme allowed the MPB to be used by other subsystems of the MPI library and for optimized operations. This flexibility was used to add support for MPI-2 dynamic processes, by the addition of accept and connect operations that use the MPB directly. Future implementations of optimized collectives and one sided operations were also made possible by this new approach; these are good targets for future performance improvements to the RCKMPI library.

## REFERENCES

- Steffen Christgau, Simon Kiertscher, and Bettina Schnor. The benefit of topology awareness of MPI applications on the SCC. In Diana Göhringer, Michael Hübner, and Jürgen Becker, editors, MARC Symposium, pages 47–51. KIT Scientific Publishing, Karlsruhe, 2011.

- [2] Jim Held. "Single-chip Cloud Computer" an IA tera-scale research processor. Euro-Par Workshops, volume 6586 of Lecture Notes in Computer Science, page 85. Springer, 2010.

- [3] Timothy G. Mattson, Rob F. Van der Wijngaart, Michael Riepen, et al. The 48-core SCC processor: The programmer's view. Supercomputing Conference. ACM/IEEE, New Orleans, LA, USA, November 2010.

- [4] Carsten Clauss, Stefan Lankes, Jacek Galowicz, Thomas Bemmerl, iR-CCE: A Non-blocking Communication Extension to the RCCE Communication Library for the Intel Single-Chip Cloud Computer December 17, 2010, Chair for Operating Systems, RWTH Aachen University

- [5] Isaías A. Comprés Ureña, Michael Riepen, and Michael Konow. RCKMPI lightweight MPI implementation for intel's single-chip cloud computer (SCC). EuroMPI, volume 6960 of Lecture Notes in Computer Science, pages 208–217. Springer, 2011.

- [6] Rob F. van der Wijngaart, Timothy G. Mattson, and Werner Haas. Light-weight communications on intel's single-chip cloud computer processor. SIGOPS Oper. Syst. Rev., 45:73–83, February 2011.

- [7] William Gropp. MPICH2: A new start for MPI implementations. Lecture Notes in Computer Science, 2474:7, 2002.

- [8] Carsten Clauss, Stefan Lankes, and Thomas Bemmerl. Performance tuning of SCC-MPICH by means of the proposed MPI-3.0 tool interface. *EuroMPI*, volume 6960 of *Lecture Notes in Computer Science*, pages 318–320. Springer, 2011.

- [9] Randolf Rotta. On efficient message passing on the intel SCC. In Diana Göhringer, Michael Hübner, and Jürgen Becker, editors, MARC Symposium, pages 53–58. KIT Scientific Publishing, Karlsruhe, 2011.

- [10] Keith Chapman, Ahmed Hussein, and Antony Hosking. X10 on the scc. Santa Clara, United States, March 2011. Presented at the Second MARC Symposium.

- [11] Rob F. van der Wijngaart, Timothy G. Mattson, and Werner Haas. Light-weight communications on intel's single-chip cloud computer processor. SIGOPS Oper. Syst. Rev., 45:73–83, February 2011.

- [12] R. Reussner, P. Sanders, L. Prechelt, and M. Mueller. SKaMPI: A detailed, accurate MPI benchmark. Lecture Notes in Computer Science, 1497:52, 1998.

- [13] D. Bailey et al. The NAS parallel benchmarks. Technical Report RNR-91-002, NAS Systems Division, January 1991.

## The Path to MetalSVM: Shared Virtual Memory for the SCC

Stefan Lankes\*, Pablo Reble\*, Carsten Clauss\* and Oliver Sinnen<sup>†</sup>

\*Chair for Operating Systems, RWTH Aachen University

Kopernikusstr. 16, 52056 Aachen, Germany

Email: {lankes,reble,clauss}@lfbs.rwth-aachen.de

†Department of Electrical and Computer Engineering, University of Auckland

Private Bag 92019, Auckland 1142, New Zealand

Email: o.sinnen@auckland.ac.nz

Abstract—In this paper, we present first successes with building an SCC-related shared virtual memory management system, called MetalSVM, that is implemented using a bare-metal hypervisor, located within a virtualization layer between the SCC's hardware and the operating system. The basic concept is based on a small kernel developed from scratch by the authors: A separate kernel instance runs on each core and together they build the virtualization layer. High performance is reached by the realization of a scalable inter-kernel communication layer for MetalSVM. In this paper we present the employed concepts and technologies. We briefly describe the current state of the developed components and their interactions leading to the realization of a Shared Virtual Memory system on top of our kernels. First performance results of the SVM system are presented in this work.

Index Terms—Many-Core, SCC, SVM, Non-Cache-Coherent Shared-Memory

## I. INTRODUCTION

Since the beginning of the multicore era, parallel processing has become prevalent across-the-board. A further growth of the number of cores per system implies an increasing chip complexity on a traditional multicore system, especially with respect to hardware-implemented cache coherence protocols. Therefore, a very attractive alternative for future many-core systems is to waive the hardware-based cache coherency and to introduce a software-oriented approach instead: a so-called Cluster-on-Chip architecture.

The Single-chip Cloud Computer (SCC) experimental processor [1] is a *concept vehicle* created by Intel Labs as a platform for many-core software research, which consists of 48 P54C cores. This architecture is a very recent example for such a Cluster-on-Chip architecture. The SCC can be configured to run one operating system instance per core by partitioning the shared main memory in a strict manner. However, it is possible to access the shared main memory in an unsplit and concurrent manner, provided that the cache coherency is then ensured by software.

A common way to use such an architecture is the utilization of the message-passing programming model. However, many applications show a strong benefit when using the shared memory programming model. The project *MetalSVM* aims the realization of a SCC-related shared virtual memory manage-

ment system that is implemented in terms of a bare-metal hypervisor and located within a virtualization layer between the SCC's hardware and the current operating system. This new hypervisor will undertake the crucial task of coherency management by the utilization of special SCC-related features such as its on-die Message-Passing Buffers (MPB). In order to offer a maximum of flexibility with respect to resource allocation and to an efficiency-adjusted degree of parallelism a dynamic partitioning of the SCC's computing resources into several coherency domains will be enabled.

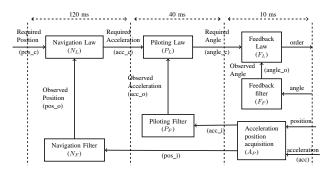

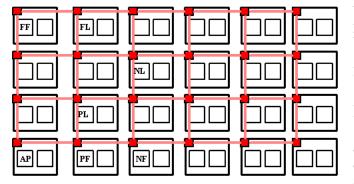

This paper focuses on the design of the MetalSVM kernel and its drivers optimized for the SCC as well as the SVM system. In Section II we refer to our previous work on the SCC and summarize related work regarding SVM system. We present a detailed insight in Section III to the design of MetalSVM and our small self-developed operating system kernel that builds the base of MetalSVM. The realization of an SVM system prototype is presented in Section VI. Important facts on the SCC supporting the path to MetalSVM are mentioned in Section IV and V with a focus on the memory system of the SCC followed by the implementation of a communication layer for MetalSVM. Section VII contains the knowledge on the port of a virtual IP interface to the SCC and presents related benchmark results. In Section VIII we describe first results for an exemplary parallel program using the SVM system prototype.

## II. PREVIOUS WORK

Referring to our previous work on the SCC we present further development on the fast inter-kernel communication layer as well as a closer look at the SVM system in this paper. The motivation and concept of our MetalSVM has been introduced at the 3<sup>rd</sup> MARC Symposium [2]. In addition to a summary of previous work on cluster-based SVM systems we first outline the potential of our approach. Other contributions to this Symposium have also shown that the memory system of the SCC is special and established methods hold a high potential for optimization. [3]

In [4], we evaluated different programming models (especially shared-memory and message-passing) for the SCC and we have shown how these models can be improved with

respect to the SCC's many-core architecture. Our experiments have shown that in particular the shared-memory programming is very complex and involved if caches are enabled because of the missing hardware cache coherency.

The Chair for Operating Systems (LfBS) at the RWTH Aachen University developed since 1996 the *Shared Memory Interface* (SMI) [5] as a programming interface that provides a large function set such as allocation and management of cluster-wide shared memory regions and its distribution and synchronization services. SMI provides no virtual common address space in contrast to an SVM system. However, shared memory regions can be explicitly allocated and managed. A small subset of its capabilities is used in this paper to benchmark our prototype of *MetalSVM*.

Existing SVM solutions are mainly based on traditional message-passing oriented networks. However, the SCC has the capability to directly access memory. From a programmer's perspective this is comparable to the Scalable Coherent Interface (SCI) standard [6] that belongs to the memory-mapped networks. In addition to the offer of a transparent read/write access to remote memory, SCI also defines a cache coherency protocol. But, PCI-SCI adapter cards that are available on the market do not support this feature. Several research projects used SCI-based PC clusters, which possessed a similar characteristic like SCC. Both systems consist of several processing units which are able to communicate transparently over shared memory regions without the support of cache-coherency.

At the LfBS, we have developed an SVM system for Intel architecture based compute clusters, called *SVMlib* [7], [8], which stores write notices and related changes in the global memory to realize a *Lazy Release Consistency* [9] model. Experiments have shown that the implementation of *SVMlib* at user level decreases the usability.

Furthermore, SVM systems can be integrated into virtual machines providing a simpler and more transparent access to the shared memory for an easy application of common operating systems and development environments. The vSMP architecture by ScaleMP¹ enables a cluster-wide cache-coherent memory sharing by implementing a virtualization layer underneath the OS that handles distributed memory accesses via InfiniBand-based communication on x86-based compute clusters. A similar project is vNUMA [10], which used Ethernet as interconnect. This project shares characteristics with our hypervisor approach such that the implementation of the SVM system takes an additional virtualization layer between the hardware and the operating system.

In fact, we want to exploit the SVM system with SCC's distinguishing capabilities of transparent read/write access to the global off-die shared memory.

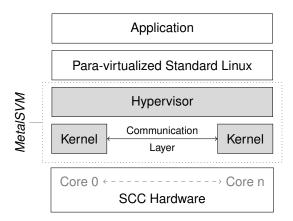

## III. DESIGN OF METALSVM

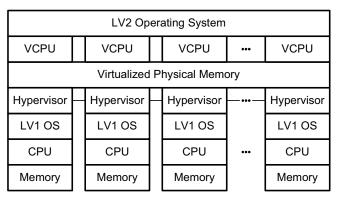

The concept of *MetalSVM* is to run a common Linux version without SVM-related patches on the SCC in a multicore

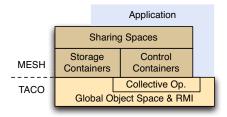

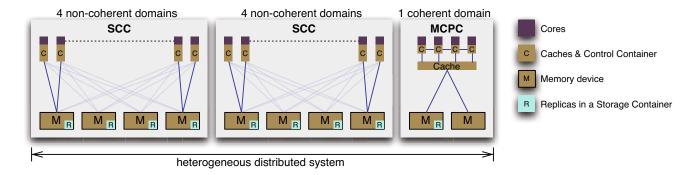

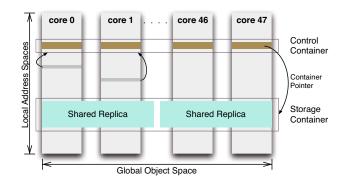

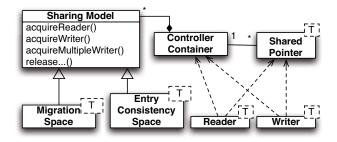

manner. For a better understanding, the structured diagram of Figure 1 illustrates the design approach of *MetalSVM*.

A major advantage of our approach, as introduced in [2], is no binding of *MetalSVM* to a certain version of Linux, because *integrating* would for example mean *patching* the kernel. The light weight hypervisor is based upon the idea of a small virtualization layer based on a monolithic-kernel developed from the scratch by the authors. A well-established interface to run Linux as para-virtualizated guest which is part of the standard Linux kernel is used to realize our hypervisor. Consequently, no modifications to the Linux kernel are needed.

Fig. 1: Concept and Design of MetalSVM

The aim of common processor virtualization is to provide multiple virtual machines for separated OS instances. We want to use processor virtualization that provides *one* logical but parallel and cache coherent virtual machine for a single OS instance, for instance Linux, on the SCC. Hence, the main goal of this project is to develop a bare-metal hypervisor, that implements the required SVM system (and thus the memory coherency by applying appropriate consistency models) within this hardware virtualization layer in such a way that an operating system can run almost transparently across the entire SCC system.

## IV. MEMORY SYSTEM

In this section we first briefly recap the memory system of the SCC and second outline the effects on the realization of an SVM system.

The SCC possesses four memory controllers providing a maximum capacity of 64 GByte of DDR3 memory. Each core has logically assigned 8 kByte of a tile's local memory buffer, called message passing buffer (MPB). To close the gap between register and main memory access time, the SCC cores have a classical memory hierarchy consisting of a local Level 1 and Level 2 cache. In addition to a Level 1 data and instruction cache size of each 8 kByte, all cores have a local Level 2 cache size of 256 kByte. Caches are organized with a cache-line size of 32 Byte in a non cache-coherent manner.

Intel Labs extended the P54C instruction set architecture (ISA) by a new instruction CL1INVMB that is closely connected to a new memory type (MPBT) indicated by a flag on

<sup>1</sup>http://www.scalemp.com

page granularity to support the use of the MPB. Accesses to this new memory type bypass the Level 2 cache and by default message-passing buffer entries are tagged.

Moreover, the flag that indicates MPBT can be used in a more generic way. Generally speaking, information about a special data type is tagged in hardware. However, this mapping is not fixed and can be adapted to use the hardware support that facilitates a coherent view on the MPB also for an SVM system.

Another extension of the SCC cores to the P54C architecture is a write combine buffer that holds one cache-line of 32 Byte. In write through mode accesses touching the same cache-line are wrapped together and written back en block from the Level 1 cache to the next level in memory hierarchy. This behavior may turn out to be useful for the SVM system. The intention for adding this feature was to accelerate the message transfer between the cores [1].

The P54C architecture uses an external Level 2 cache without the possibility to flush contents using hardware support. A flush routine has been developed that replaces all L2 contents by reading invalid data but this turned out to be costly. [11] We limit our first experiments to an SVM system prototype that only enables L1 caching for a shared memory region. To control write strategy of cached data a page table entry contains a bit, that the memory management of *MetalSVM* sets for shared pages to uses a *write through* strategy.

Obviously, a drawback of this solution is a significantly smaller amount of cache in use for shared regions. But to waive the use of Level 2 cache for shared memory regions a major advantage arises that is the possibility to tag SVM related data. Thus, a selective invalidate of cached data via CL1INVMB is possible. Due to the fact that our current SVM system uses write through, a method called fool write combine buffer is sufficient to flush cached data. The method simply touches an MPBT tagged cache-line that is only used for this purpose. Thus, the off-die memory holds current data.

## V. COMMUNICATION LAYER

The realization of the hypervisor needs a fast inter-core communication layer, which will be used to manage resources between the kernels. An important requirement to this communication layer is the support of asynchronous message-passing because it is not predictable when a kernel needs an exclusive access to a resource that is owned or managed by another kernel instance. As a result, the synchronous communication library *RCCE* [12] is not suitable for *MetalSVM*. An alternative approach is to copy the message to the message-passing buffer of the receiving core and afterwards to signalize the incoming message with a remote interrupt.

## Interrupt Handling

Realization of event based communication between the SCC-cores needs either interrupts or events have to be checked at defined points in time. We followed an interrupt driven approach for our communication layer to enable a fast communication. On the one hand the latency of signal passing is

important. On the other hand the time to process signals and its scalability influences the performance of our communication layer.

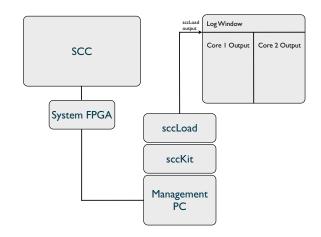

Previous versions of *sccKit* only supported the generation of an Inter-Processor Interrupt (IPI) by writing directly to the receiving core's configuration register. Hence, the receiving core can be interrupted this way but no information can be obtained about the sender of a specific interrupt. Since *sccKit 1.4.0* the system FPGA holds a Global Interrupt Controller (GIC) [13]. In addition to the direct method to generate an IPI the possibility arises to indirectly generate an IPI using the GIC. Consequently, this IPI can be used to obtain the information by which core it has been raised.

Event processing of the mailbox system, described in the following, is realized in the interrupt handler of *MetalSVM*. With the focus on scalability the information on the sender of an interrupt creates the option for a mailbox system to selectively check mailboxes.

## Mailbox System

A mailbox system has become part of *MetalSVM's* communication layer and extends iRCCE [14] to enable an event driven and fast asynchronous communication path between the SCC cores. For each communication path between two cores a mailbox of one cache-line size is reserved at each local MPB. Thus, the mailbox system takes 1.5 kByte of MPB space per core assuming a maximum number of 48 cores. RCCE provides a memory allocation scheme to manage the remaining MPB space of 6.5 kByte.

Accesses to a specific mailbox of a target core are restricted by only allowing the receiver to read data and toggle a send flag that the mailbox contains. A sender with the intention to pass a signal is allowed, in addition to toggle the send flag, to write data to the mailbox. Whenever a receiver toggles the send flag a signal has been processed and when a sender toggles the send flag a new signal has been placed. As a result of this communication method the generation of a *single reader single writer* problem leads to a simplified synchronization scheme that is enabled by the restriction of accesses to the mailboxes.

Signals between the cores are passed in a *remote write and local read* approach in contrast to the *local write and remote read* approach of the RCCE library. The mailbox system reverses the data flow compared to the RCCE send respective receive methods because event processing is realized in the interrupt handler.

## VI. SVM SYSTEM

The SVM system manages pages located in shared memory. A coherent view on the virtual common address space is enabled by flushing cached data at defined points in time. For a first prototype three functions are sufficient to enable the use of the SVM system and thereby explore the capabilities of the SCC for a software managed coherence scheme. Following SMI like functions are provided under *MetalSVM* to a kernel task of the current SVM version:

- svm alloc

- svm flush

- svm\_invalidate

The function <code>svm\_alloc</code> is used to allocate an amount of bytes in a cached shared memory region. The function <code>svm\_flush</code> is used to implicitly write back modified data<sup>2</sup>, and <code>svm\_invalidate</code> to remove possibly outdated data from the cache. This is either done within the interrupt handler of the current page owner or within the page fault handler on the core where the access violation occurs.

The SVM system of *MetalSVM* uses the mailbox system for the crucial task to change access permissions of shared pages. Therefore, a signal is sent to the page owner which can be identified because the information of ownership is located in a shared memory region and therefore accessible by all cores. If the ownership has changed in the meantime, e.g. another core has requested the page, the receiver of the signal has to forward the message to its new destination. As a result, the first sender of a signal in addition to the address of the target shared page is necessarily encoded by a signal, so that the owner vector entry can be updated.

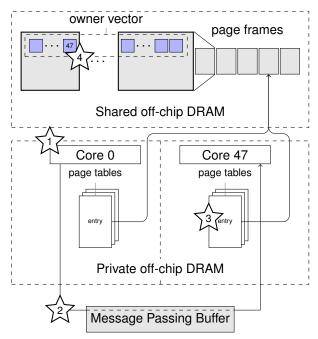

Fig. 2: Concept and design of the SVM subsystem

A strong consistency model is supported by the prototype implementation of our SVM system. At each point in time only one owner of a page exists which is allowed to read or write to it. This ownership is registered in an ownership vector, which is also located in the off-die memory as exemplarily illustrated by Figure 2. Each core possesses its private page tables.

Whenever a page is accessed without permission a kernel enters the page fault handler and sends a request to the current owner via the mailbox system. Regarding the strong consistency model no parallel access to shared pages is allowed and the ownership has to be exchanged. First, the current owner of the page clears its access permission. Second, it flushes the cache and third sets the new owner id to the ownership vector as an acknowledgment. As a result the core that requested access is registered as the new owner. After this procedure the requesting core can continue its calculation. Obviously, the performance of the mailbox system has a direct impact to the performance of the SVM system.

Figure 2 shows an example where an SVM related page fault occurs at Core 0 involving Core 47. Following steps have to be performed:

- 1) A page fault occurs at Core 0

- 2) After sending a message to Core 47 requesting the page, Core 0 is polling on the owner vector entry

- Core 47 flushes its cache and changes the page table entry

- 4) Core 47 changes the ownership

After this procedure Core 0 is the new owner and hereby has full access permissions.

## VII. IP STACK

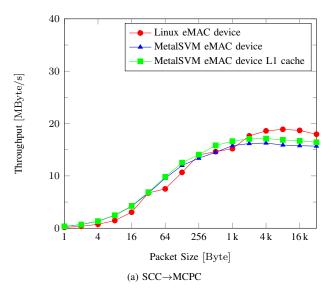

In this section we present the realization of two IP devices, one memory mapped virtual device for the realization of ondie communication and one eMAC device for the off-die communication. For this purpose the light-weight IP (lwIP) stack [15] has been integrated into the MetalSVM kernel. As a result, established BSD sockets are supported to enable an easy integration of standard application. In addition, we analyze a variant that interacts with the IP driver using an overloaded socket that bypasses the full IP stack. For further performance optimizations the developed devices are fully configurable having options to choose the MPB or off-chip DRAM for communication and to enable L1 caching. Applications for the described devices can be a monitoring the SVM system or providing an IP service to the guest operating system. Here, the guest can use a tunnel device to hand down IP packets to MetalSVM.

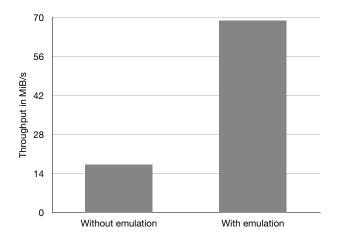

In principle, the first driver is a porting of Linux's eMAC device driver to lwIP and builds an interface to the Ethernet ports that are connected to the SCC. We used the driver of SCC Linux from sccKit 1.4.1 within the scope of Linux kernel 2.6.38.3-jbrummer as a reference, which uses non-cachable memory for the communication between kernel and hardware device. Again, the SCC offers the possibility to invalidate in one cycle the cache entries for MPBT tagged pages. The option to enable the L1 cache for the receive buffers of the eMAC device generates the possibility to visualize the benefit of this hardware support for communication. Here, specific cache entries have to be invalidated before the receiver reads data from its receiver buffer. When compared to the Linux driver that holds the L1 cache disabled for the receive buffers, a positive impact on performance is expected for the MetalSVM driver that reads a whole cache-line from the memory.

<sup>&</sup>lt;sup>2</sup>In this scenario, flushing of the write combining buffers.

Fig. 3: Transfer Throughput between MCPC and SCC via eMAC

Obviously this method reduces the number of memory accesses up to a factor of:

$$\frac{8 \cdot t_{CM}}{t_{CM} + 7 \cdot t_{CH}}$$

Where,  $t_{CM}$  is the time for a cache miss and  $t_{CH}$  is the time for a L1 cache hit.

The second driver uses an established standard and enables a virtual IP interface to realize inter-kernel communication. The support of standard interfaces for communication is not in the focus of MetalSVM. However, a driver has been written that realizes communication via memory mapped regions. For this driver a configuration exists to use either the off-die or the on-die memory (MPB).

The first configuration uses the off-die shared memory for communication and therefore generates no load to the MPB. An application might be to monitor the SVM system. The use of the second configuration is preferred to reach a higher performance. However, using the MPB can generate noise to the SVM system that runs in parallel.

In principle, each receiver optionally creates its own receive buffer either in on-die or off-die memory. The senders copy their data directly into the receive buffer and wake up the receiver via an inter processor interrupt. To allow parallel access between the receiver and senders, the receive buffer is managed as heap. The maximum transfer size is:

$$\frac{1}{2} \cdot size of (buffer) - size of (cache line)$$

The result of the split of larger messages into smaller submessages is that the receiver is able to process sub-messages that are present during the next transfer operation of the sender.

The data structure to manage the heap is located at the off-die memory to increase the size of the receiver buffer. In contrast to the presented mailbox system the lwIP drivers use

only one receive buffer per core. This is because the incoming messages are clearly larger than a mail of the mailbox system. Accesses to the receive buffers have to be synchronized. Therefore, the current version uses RCCE locks which enable an access to the hardware implemented Test-And-Set registers. Many features of the IP stack are needless for the inter-core communication. For instance, on the SCC it is not possible to receive corrupt data. To benefit from this behavior, we have developed a prototype, which emulates the BSD socket interface, bypasses the IP stack and forwards the messages directly to the receivers. In our approach, a parallel using of the IP stack and the bypassing approach is possible.

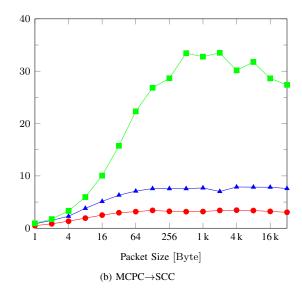

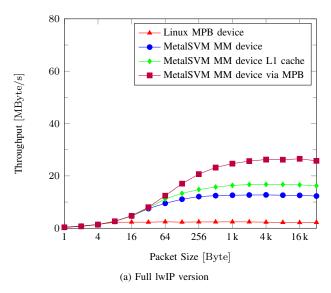

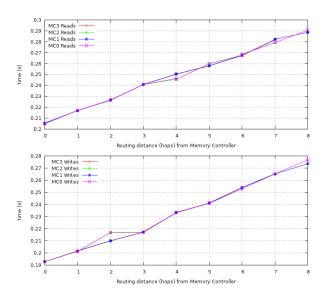

## A. Benchmark Results

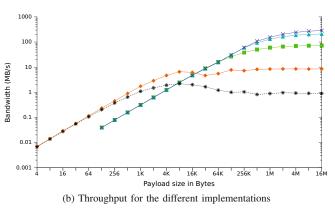

All diagrams of this section show the throughput average by different package size from small packages of 1 Byte up to large packages of 32 kByte. The test platform has been configured with a core frequency of 533MHz, a memory and mesh frequency of 800MHz. The driver uses as receive buffer size either 8 kByte for the off-die or 7 kByte for the on-die memory. For the evaluation of the performance of *MetalSVM*'s IP stack the established benchmark *netio*<sup>3</sup> has been used.

First of all, we present the results of our eMAC driver in comparison to the driver of SCC Linux. We used a standard configured SCC and MCPC from the *MARC Data Center*. Figure 3b shows the throughput from MCPC to SCC and Figure 3a illustrates the inverse direction. By enabling the cache for the receiving buffer of the SCC, the sending throughput of MCPC is increased by factor 5. These results document the huge impact of the MBPT flag.

Figure 4a shows the performance of the inter-core communication using the full IP stack. The performance of the current Linux driver is added as a reference.

<sup>&</sup>lt;sup>3</sup>http://www.ars.de/ars/ars.nsf/docs/netio

Fig. 4: Sending Throughput from Tile 0 to Tile 1

## VIII. APPLICATION

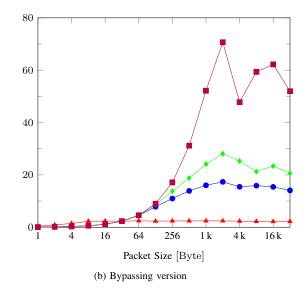

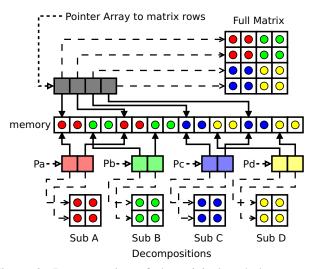

For the demonstration of our SVM system we have chosen a classical synchronous iteration program example. The heat distribution of square metal sheet with known temperatures at its edges represents a two-dimensional Laplace problem. Figure 5 illustrates the further described method.

The resulting partial differential equation can be solved with the common Jacobi Over Relaxation (JOR) algorithm standing for a simple parallel program example using a shared memory approach. The Jacobi iterations can be described by the following formula:

$$u_{i,j}^{k+1} = \frac{1}{4} \cdot [u_{i-1,j}^k + u_{i+1,j}^k + u_{i,j-1}^k + u_{i,j+1}^k]$$

An analysis of the capabilities offered by the *MetalSVM* layer is reached by executing kernel threads in the *MetalSVM*

kernel. Therefore, the function svm\_alloc is used in a collective way to allocate a shared memory region with Level 1 cache enabled.

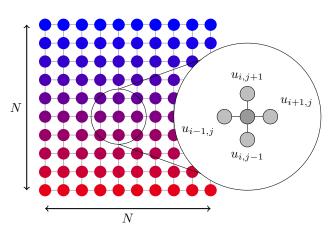

Allocated memory is used as follows: The simulation data of  $1024 \times 512$  **double** values are stored in two arrays namely old and new. After each iteration the values from new are moved to old by exchanging the references. A barrier follows to ensure that iterations are processed synchronously. We used the linear barrier implementation of the RCCE library. A static distribution to n cores of the squared problem size is used. Each core iterates over N/n lines. The shared memory application assumes a synchronous behavior after each iteration which creates the requirements for an SVM system to provide correct data. Enabled caches have to be flushed and invalidated implicitly, regarding a strong release consistency model, or explicitly, regarding a lazy release consistency. The current version of MetalSVM supports both as described in Section VI.

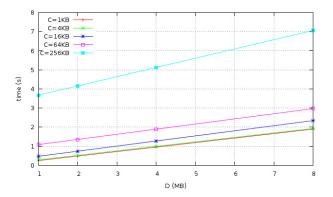

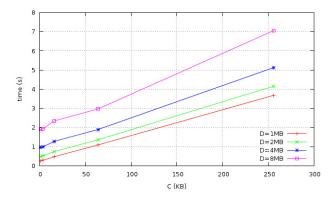

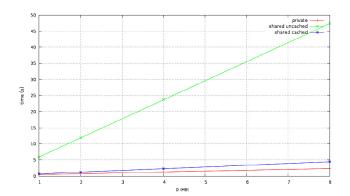

Fig. 5: Heat Distribution Problem

Figure 6 shows benchmark results of the previously described application with a different core count on the SCC platform <sup>4</sup>. Curve — depicts terms of a message passing laplace variant based on iRCCE [14], which uses a non-blocking behavior to exchange rows after each iteration. Curves and -- represent the performance measurements of a strong consistency model. The first setup — is the usage of only one memory controller (MC) holding the entire matrix. Here, the well known memory wall problem occurs. The consequence is a reduction of the scalability. As a second setup the matrix is statically partitioned to all four MC's to distribute the memory load. The result — is a better scalability up to 8 cores. The scalability has to be improved for the use of more than 8 cores. As a third setup a lazy release memory model has been applied to the given problem. Here, the caches are flushed after each iteration without the generation of an interrupt or an exception. Measurements of this setup — show a nearly optimal result.

Fig. 6: Laplace Runtimes

Nevertheless, it has to be considered that the JOR algorithm is an extremely stressful example for an SVM system. Here, the barrier after each iteration leads to a synchronized access of all cores to their neighbors' data. In the case of a lazy consistency, the majority of cores send a request mail and IPI to its neighbor just after the synchronization point. Certainly, for such an extremely stressful example the results are excellent. The linear runtime of the shared memory application is approximately half of the linear runtime of the message passing application. What shows the impact of the write combining buffer. In this experiment the message passing application reaches a super-linear speedup in a region of 32 to 48 cores by using the L2 Cache. Here, the problem size fits into the L2 Cache.

## IX. CONCLUSIONS AND OUTLOOK

In this paper, we have presented our first steps to design and implement a strong memory model for the SVM system that has been integrated into *MetalSVM*. The basic concept is based on a mailbox system with a low-latency interkernel communication layer. First benchmark results of our SVM system prototype are promising. In fact, the overhead of the Strong Release Consistency compared to the Lazy Release Consistency Model is tolerable. Moreover, this paper shows that the current drivers of SCC Linux's IP stack have potential for improvement. In the majority of the presented benchmarks the IP stack of *MetalSVM* reaches a significantly better performance.

In the future, we will investigate other, weaker memory models, to achieve the best performance for our bare-metal hypervisor. We plan to use experiences [17] from the design of kernel extensions for NUMA systems to reach a more dynamic memory distribution strategy like *Affinity-on-Next-Touch* [18]. In addition, improvements regarding the scalability of our synchronization layer and the collective operations ,provided by MetalSVM, are in progress.

We aim for the nearer future to increase of the usability of *MetalSVM* to address a broader audience. Besides, we recommend an integration of our improved IP solution back to SCC Linux so that all MARC members can benefit from this work.

## ACKNOWLEDGMENT

The research and development is funded by Intel Corporation. The authors would like to thank especially Ulrich Hoffmann, Michael Konow and Michael Riepen of Intel Braunschweig for their help and guidance.

<sup>&</sup>lt;sup>4</sup>core/mesh/memory frequency of 533/800/800 MHz

## REFERENCES

- [1] SCC External Architecture Specification (EAS), Intel Corporation, November 2010, Revision 1.1.

- [2] P. Reble, S. Lankes, C. Clauss, and T. Bemmerl, "A Fast Inter-Kernel Communication and Synchronization layer for MetalSVM," in Proceedings of the 3rd MARC Symposium, KIT Scientific Publishing, Ettlingen, Germany, July 2011.

- [3] M. van Tol, R. Bakker, M. Verstraaten, C. Grelck, and C. Jesshope, "Efficient Memory Copy Operations on the 48-core Intel SCC Processor," in Proceedings of the 3rd MARC Symposium, KIT Scientific Publishing, Ettlingen, Germany, July 2011.

- C. Clauss, S. Lankes, P. Reble, and T. Bemmerl, "Evaluation and Improvements of Programming Models for the Intel SCC Many-core Processor," in Proceedings of the International Conference on High Performance Computing and Simulation (HPCS2011), Workshop on New Algorithms and Programming Models for the Manycore Era (APMM), Istanbul, Turkey, July 2011.

- [5] M. Dormanns, K. Scholtyssik, and T. Bemmerl, "A Shared-Memory Programming Interface for SCI Clusters," in SCI: Scalable Coherent Interface, H. Hellwagner and A. Reinefeld, Eds. Springer Verlag, 1999, pp. 281–290.

- [6] ÎEEE, Ed., Standard for Scalable Coherent Interface (SCI), ser. IEEE The Institute of Electrical and Electronics Engineers, Inc., Standards. 1992, no. 1596.

- [7] S. Paas, T. Bemmerl, and K. Scholtyssik, "Win32 API Emulation on UNIX for Software DSM," in Proceedings of the 2nd USENIX Windows NT Symposium, Seattle, Washington, USA, August 1998, pp. 39-46.

- [8] K. Scholtyssik and M. Dormanns, "Simplifying the use of SCI shared memory by using software SVM techniques," in *Proceedings of 2*. Workshop Cluster Computing, Karlsruhe, Germany, March 1999.

- [9] P. Keleher, A. L. Cox, and W. Zwaenepoel, "Lazy Release Consistency for Software Distributed Shared Memory," in *Proceedings of the 19th* Annual International Symposium on Computer Architecture, 1992, pp. 13 - 21.

- [10] M. Chapman and G. Heiser, "vNUMA: A virtual shared-memory multiprocessor," in Proceedings of the 2009 USENIX Annual Technical Conference, San Diego, CA, USA, Jun 2009, pp. 349-362.

- [11] M. van Tol, "SCC L2 flush routine," http://marcbug.scc-dc.com/ bugzilla3/show\_bug.cgi?id=195.

- [12] T. Mattson and R. van der Wijngaart, RCCE: a Small Library for Many-Core Communication, Intel Corporation, May 2010, Software 1.0release.

- [13] The sccKit 1.4.x User's Guide, Intel Labs, October 2011.

- [14] C. Clauss, S. Lankes, T. Bemmerl, J. Galowicz, and S. Pickartz, iRCCE: A Non-blocking Communication Extension to the RCCE Communication Library for the Intel Single-Chip Cloud Computer, Chair for Operating Systems, RWTH Aachen University, July 2011, Users' Guide and API

- [15] A. Dunkels, Design and Implementation of the lwIP TCP/IP Stack, Swedish Institute of Computer Science, 2001.

- [16] J. Nagle, "Congestion control in IP/TCP internetworks," SIGCOMM

- Computer Communication Review, vol. 14, no. 4, pp. 11–17, 1984. [17] S. Lankes, B. Bierbaum, and T. Bemmerl, "Affinity-On-Next-Touch: An Extension to the Linux Kernel for NUMA Architectures," in Proceedings of the 8th International Conference on Parallel Processing and Applied Mathematics (PPAM 2009), Workshop on Memory Issues on Multi- and Manycore Platforms, Springer Berlin / Heidelberg, Volume 6067/2010 of LNCS, Wroclaw, Poland, 2010, pp. 576-585.

- [18] L. Noordergraaf and R. van der Pas, "Performance Experiences on Sun's WildFire Prototype," in Proceedings of the 1999 ACM/IEEE conference on Supercomputing, Portland, Oregon, USA, November 1999.

## Parallel AI Planning on the SCC

Vincent Vidal, Simon Vernhes, and Guillaume Infantes

Abstract—We present in this paper a parallelized version of an existing Artificial Intelligence automated planner, implemented with standard programming models and tools (hybrid Open-MP/MPI). We then evaluate this planner with respect to its sequential version through extensive experiments over a wide range of academic benchmarks, on two different target architectures: a small standard cluster and the research processor SCC ("Single-chip Cloud Computer") developed by Intel Labs and made available to the research community through the MARC program ("Many-core Applications Research Community"). We obtain interesting speedups (super-linear in some cases) on both architectures. Interestingly enough, these experiments also reveal different behaviors between the cluster and the SCC.

## I. INTRODUCTION

Automated Planning in Artificial Intelligence [1] is a general problem solving framework which aims at finding solutions to combinatorial problems formulated with concepts such as actions, states of the world, and goals. For more than 50 years, research in Automated Planning has provided mathematical models, description languages and algorithms to solve this kind of problems. We focus in this paper on Classical Planning, which is one of the simplest model but has seen spectacular improvements in algorithm efficiency during the last decade.

The sequential planning algorithm that will form the basis of our parallel algorithm has been implemented in the YAHSP2 planner [2][3] which participated to the  $4^{th}$  and  $7^{th}$  International Planning Competitions<sup>1</sup> (IPC) in 2004 and 2011. It uses a forward state-space heuristic search algorithm with relaxed plan extraction inspired by the FF planner [4]. The main differences with FF are that (1) the search algorithm is a complete weighted-A\* algorithm [5] (while FF first tries an incomplete one), (2) the heuristic function is based on  $h^{add}$  [6] instead the length of the relaxed plan length and (3) at each node of the search, a lookahead strategy is performed before classical node expansion in order to try to reach a node closer to a goal state, in a computationally easy way by using actions from the relaxed plan.

The parallelization scheme we propose is based on the principle already used in TDS [7] and HDA\* [8]: to distribute search nodes among the processing units (PUs) based on a hash key computed from planning states. In this way, the list of nodes to be expanded (the open list) owned by each PU are disjoint: computations made on a given state (applicable actions, heuristic function, lookaheads, etc.) are performed only once, by the PU the node belongs to. Another important

All authors are working at Onera, the French Aerospace Lab, in the DCSD department, Toulouse center. Email addresses: first-name.last-name@onera.fr.

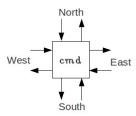

aspect is that communication between PUs can be performed in an asynchronous way: a PU expands nodes from its open list, sends sons to the PUs they belong to, and periodically checks its incoming messages to incorporate new nodes into its open list (between OpenMP threads, this last step is seamlessly performed by writing to shared memory).

We evaluate the performance of the parallel algorithm with respect to its sequential version over a wide range of academic benchmarks issued from the IPCs, on two architectures: a small standard cluster composed of four 12-core servers (48 cores in total), and the research processor SCC ("Single-chip Cloud Computer") embedding 48 cores on a single chip developed by Intel Labs. These experiments show that interesting speedups, sometimes super-linear, are obtained thanks to the parallelization. Unfortunately, some super-linear speed-downs are also observed, which suggests some improvements to the parallelized algorithm that could combine the advantages of both. This behavior was not unexpected, as the parallelized algorithm does not perform the same computations as the sequential version: the order of node evaluation being modified, the search space is not explored the same way, which can help or deserve the parallel algorithm.

The paper is outlined as follows. After introducing the research domain of Classical Planning in Artificial Intelligence and the mathematical STRIPS model of planning, we present the sequential algorithm implemented into the YAHSP2 planner. We then briefly explain the principles of the parallelization we propose, and the main modifications of the sequential algorithm. After having described the experimental evaluation, we conclude and draw some future works.

## II. BACKGROUND ON CLASSICAL PLANNING IN AI

Classical Planning is about finding a sequence of actions (possibly optimal) leading from an initial state towards a defined goal. We make some assumptions about the world:

- finite number of possible states of the world,

- full observability: one always know the state of the world,

- determinism: the result of applying an action to a state s

is always a single state s'.

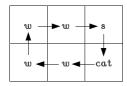

An example of an Automated Planning problem is described in Figure 1. There, a robot arm can move a single block at a time. It is able to unstack two blocks by taking the upper one; stack a block on another; pick-up a block from the table or put-down a block on the table. A planning algorithm should find a plan (a sequence of defined actions) that the robot can execute to reach the goal state from the initial one.

Planning is hard, in our case it has been shown to be PSPACE-complete [9]. The major problem for planning algorithms is to deal with the combinatorial explosion of the number of states during search.

This work has been funded by the Onera research program PR-SCC and supported by Intel Labs through a research proposal for working with Intel SCC and the Many-core Applications Research Community (MARC).

<sup>&</sup>lt;sup>1</sup>See http://ipc.icaps-conference.org/ for more information about the IPCs.

Fig. 1. An Automated Planning classic domain: BlocksWorld

a) PDDL (Planning Domain Definition Language): PDDL [10] is a language commonly used to represent planning problems, as for instance in IPCs. It helps to compare planners with well-established benchmarks<sup>2</sup> (over 40 different application domains and several thousand instances).

The operator stack of the previous domain (Figure 1) written using PDDL syntax is shown below:

After parsing a PDDL problem, planners transform the PDDL first-order language into a set-theoretic representation (sets of propositions) like STRIPS (see below). To do so, PDDL operators, like (stack ?ob ?underob), are instantiated into ground actions {(stack A B), (stack A C), ...}.

- b) The STRIPS model of Classical Planning: Planning problems can be expressed into the STRIPS model defined as follows. A state of the world is represented by a set of ground atoms. A ground action a built from a set of atoms A is a tuple  $\langle pre(a), add(a), del(a) \rangle$  where  $pre(a) \subseteq A, add(a) \subseteq$ A and  $del(a) \subseteq A$  represent the preconditions, add effects and del effects of a respectively. A planning problem can be defined as a tuple  $\Pi = \langle A, O, I, G \rangle$ , where A is a finite set of atoms, O is a finite set of ground actions built from A,  $I \subseteq A$  represents the *initial state*, and  $G \subseteq A$  represents the goal of the problem. The application of an action a to a state s is possible if and only if  $pre(a) \subseteq s$  and the resulting state is  $s' = (s \setminus del(a)) \cup add(a)$ . A solution plan is a sequence of actions  $\langle a_1, \ldots, a_n \rangle$  such that for  $s_0 = I$  and for all  $i \in$  $\{1,\ldots,n\}$ , the intermediate states  $s_i=(s_{i-1}\setminus del(a_i))\cup$  $add(a_i)$  are such that  $pre(a_i) \subseteq s_{i-1}$  and  $G \subseteq s_n$ .

- c) Prior work on Automated Planning: Different approaches exist [1]. One of the most successful for suboptimal planning is state-space search where each node corresponds to a state of the world and edges between nodes are applicable actions which allow to move from a state s to a state s' (state transition). Finding a path from the initial state I (node) to the goal state G provides a plan for a problem. Heuristic search algorithms like  $A^*$  are mainly used to find such a path. Various domain-independent heuristics have been developed to guide search. Many successful state-of-the-art sequential planners are based on Fast Downward [11].

Several approaches to parallel planning have been proposed in recent years. Most of them are modifications of the A\* algorithm, trying to transform sequential planning techniques

## Algorithm 1: plan-search

```

: a planning problem \Pi = \langle A, O, I, G \rangle and a weight \omega for the

heuristic function

output : a plan if search succeeds, \perp otherwise

1 open \leftarrow closed \leftarrow \emptyset

create a new node n:

n.state \leftarrow I

n.parent \leftarrow \bot

n.steps \leftarrow \langle \rangle

n.length \leftarrow 0

7 n' \leftarrow \texttt{compute-node}(\Pi, \omega, n, open, closed)

if n' \neq \bot then return extract-plan(n')

10

while open \neq \emptyset do

11

n \leftarrow \arg\min_{n \in open} n.heuristic

12

open \leftarrow open \setminus \{n\}

foreach a \in n.applicable do

13

create a new node n':

14

n'.state \leftarrow (n.state \setminus del(a)) \cup add(a)

16

n'.parent \leftarrow n

n'.steps \leftarrow \langle a \rangle

17

n'.length \leftarrow n.length + 1

18

n'' \leftarrow \texttt{compute-node}(\Pi, \omega, n', open, closed)

19

if n'' \neq \bot then return extract-plan(n'')

20

21

return 丄

```

into parallel ones. Some algorithms use a distributed hash function to allocate generated states to a unique processing unit and avoid unnecessary state duplications, like HDA\* [8]. Parallel Frontier A\* with Delayed Duplicate Detection [12] uses a strategy based on intervals computed by sampling to distribute the workload among several workstations, targeting distributed-memory systems. The Adaptive K-Parallel Best-First Search [13] algorithm presents an asynchronous parallel search for multi-core architectures. This paper also provides a recent bibliography about parallel planning. In the IPC 2011 competition, a multi-core track has been started. The most efficient planners were the ones using a portfolio-based approach, meaning they run different planners (or the same planner with different configurations) on each processor (or core) like ArvandHerd [14] and ay-Also-Plan Threaded [15].

## III. THE SEQUENTIAL PLANNING ALGORITHM

Algorithm 1 (plan-search) constitutes the core of the best-first search algorithm (a weighted-A\* here). The first call to compute-node may find a solution to the problem without search, by recursive calls to the lookahead process. If not, nodes are extracted from the open list following their heuristic evaluation and are expanded with the applicable actions (already computed and stored in nodes inserted into the open list), and a solution plan is returned as soon as possible. Search can be pursued in an anytime way, in order to improve the solution, with pruning of partial plans whose quality is lower than that of the best plan found so far. In our experiments, the weight  $\omega$  has been set to 3.

Algorithm 2 (compute-node) first performs duplicate state detection. It then computes the heuristic, checks if the goal is obtained or cannot be reached, and updates the node with the heuristic and the applicable actions given by compute-hadd. The node is then stored in the open list and a lookahead

<sup>&</sup>lt;sup>2</sup>The benchmark problems used in past planning competitions are all available on the IPC webpages

## Algorithm 2: compute-node

```

: a planning problem \Pi = \langle A, O, I, G \rangle, a weight \omega for the

heuristic function, a node n, the open and closed lists

output

: a goal node if search succeeds, \bot otherwise; open and

closed are updated

1 if \exists n' \in closed \mid n'.state = n.state then return \bot

2 else

closed \leftarrow closed \cup \{n\}

3

\langle cost, app \rangle \leftarrow \texttt{compute-hadd}(\Pi, n.state)

4

5

gcost \leftarrow \Sigma_{g \in G} \ cost[g]

if gcost = 0 then return n

else if gcost = \infty then return \bot

n.applicable \leftarrow app

10

n.heuristic \leftarrow n.length + \omega \times gcost

11

open \leftarrow open \cup \{n\}

\langle state, plan \rangle \leftarrow \texttt{lookahead}(\Pi, n.state, cost)

12

13

create a new node n'.

14

n'.state \leftarrow state

15

n'.parent \leftarrow n

n'.steps \leftarrow plan

16

n'.length \leftarrow n.length + length(plan)

17

return compute-node(\Pi, \omega, n', open, closed)

18

```

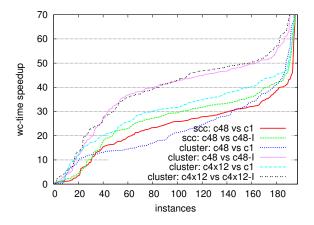

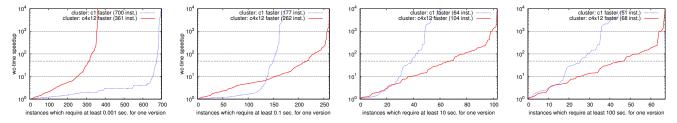

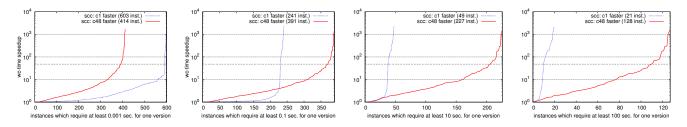

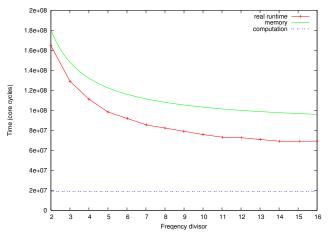

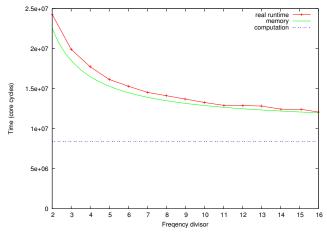

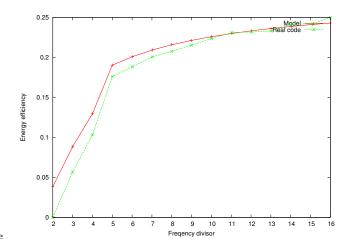

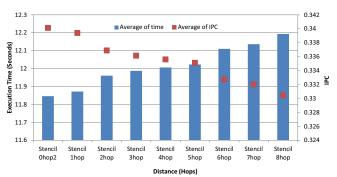

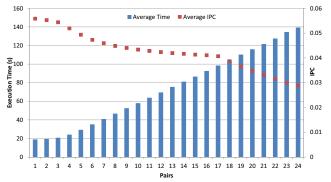

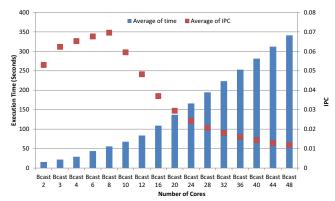

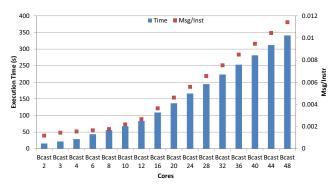

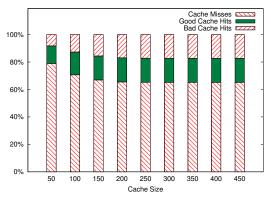

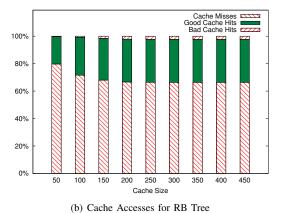

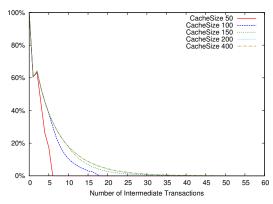

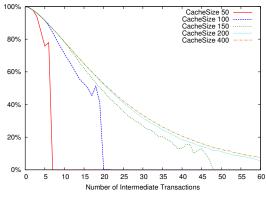

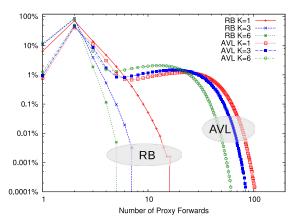

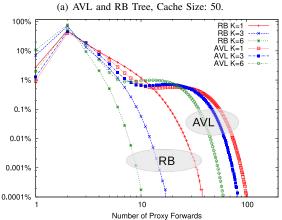

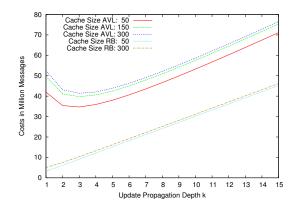

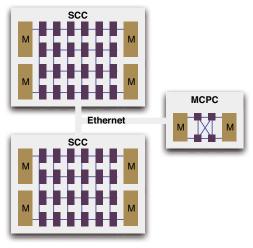

state/plan is computed by a call to lookahead. A new node corresponding to the lookahead state is then created and compute-node is recursively called. Recursion is stopped when a goal, duplicate or a dead-end state is reached.